嵌入式技术基础与实践-学习札记(一)

KL系列MCU简介与体系结构概述

该系列是业内首款基于\(ARM\ Cortex-M0+\)内核的\(MCU\),具有超低功耗、应用设计方便、扩展性好、系列品种齐全等特点。\(KL\)系列\(MCU\)面向家用电器、便携式医疗系统、智能电表、照明、电源、电机控制及工业控制系统等。\(KL\)系列的主要特点如下最高工作频率\(48MHz\)、支持直接存储器访问\(DMA\),位操作引擎\(BME\)、内核单周期访问内存速度可达\(1.77CoreMark/MHz\)、单周期访问\(I/O\)、关键外设速度比标准\(I/O\)最大提高\(50\%\);\(2\)级流水线设计减少了指令周期数\(CPI\),提高跳转指令和执行\(ISR\)中断服务例程速度;与\(8\)位,\(16\)位\(MCU\)相比具有更精简的代码密度,减少\(Flash\)空间、系统资源及功耗;更精简的指令系统优化访问程序存储空间,完全兼容\(ARM\ Cortex-M0\),兼容\(Cortex-M3/M4\)指令集子集。

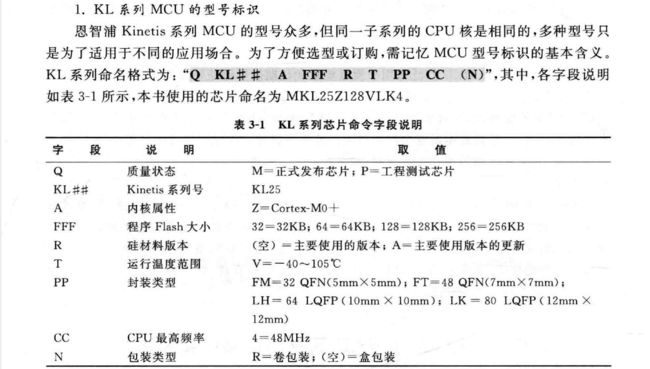

KL系列MCU的型号标识

KL系列MCU体系结构概述

\(KL\)系列\(MCU\)是以\(AMBA\)总线规范为架构的片上系统,如图所示:

KL25系列存储映像与中断源

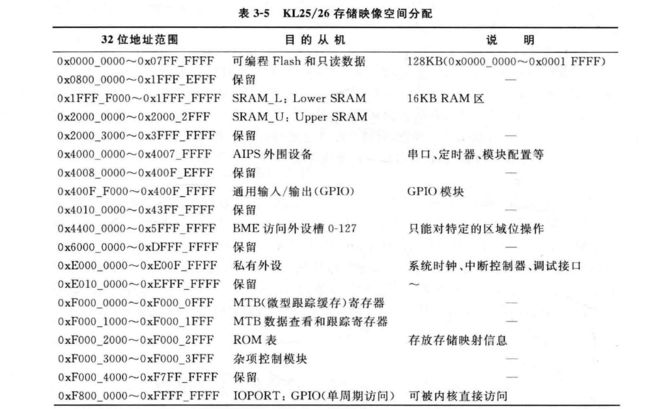

KL25系列存储映像

所谓存储映像在这里可以直观地理解为\(M0+\)寻址的\(4GB\)地址空间\((0x000\_0000\sim 0xFFFF\_FFFF)\)被如何使用,都对应了哪些实际的物理介质。下面利用\(GPIO\)模块来阐述有关的概念。

\(GPIO\)模块使用了\(0x400F\_F000\sim 0x400F\_FFFF\)地址空间,这些空间内的\(GPIO\)寄存器与\(CPU(即M0+内核)\)内部寄存器(如\(R0,R1\)等)不同,访问\(GPIO\)寄存器需要使用直接地址进行访问,也就是说需要使用三总线(地址总线,数据总线,控制总线)。而访问\(CPU\)内部寄存器,不需要经过三总线(汇编语言直接使用\(R0,R1\)等名称即可),没有地址问题。由于访问\(CPU\)内部寄存器不经过三总线,所以比访问\(GPIO\)寄存器来的快。为区别\(CPU\)内部寄存器,\(GPIO\)寄存器也被称为“映像寄存器”\((Mapping\ Register)\),相对应的地址被成为“映像地址”\((Mapping\ Address)\)。整个可直接寻址的空间被称为“映像地址空间”\((Mapping\ Address Space)\)。

对于此表,主要记住片内\(Flash\)区及片内\(RAM\)区存储映像。因为中断向量、程序代码、常数放在片内\(Flash\)中,源程序编译后的链接阶段需要使用的链接文件中需含有目标芯片\(Flash\)的地址范围及用途等信息,才能顺利生成机器码。链接文件中还需包含\(RAM\)的地址范围及用途等信息,以便生成机器码确切定位全局变量、静态变量的地址及堆栈指针。

\(KL25\)片内\(Flash\)大小为\(128KB\),地址范围是\(0x0000\_\sim 0x0001\_FFFF\),一般被用来存放中断向量,程序代码,常数等,其中前\(192B\)为中断向量表。

\(KL25\)片内\(RAM\)为静态随机存储器\(SRAM\),大小为\(16KB\),地址范围\(0x1FFF\_F000\sim 0x2000\_2FFF\),一般被用来存储全局变量、静态变量、临时变量(堆栈空间)等。

KL25中断源

中断是计算机发展中一个重要的技术,它的出现很大程度上解放了处理器,提高了处理器的执行效率。所谓中断,是指\(MCU\)在正常运行程序时,由于\(MCU\)内核异常或者\(MCU\)各模块发出请求事件,引起\(MCU\)停止正在运行的程序,而转去处理异常或执行处理外部事件的程序。

内核中断主要指异常中断,非内核中断又称可屏蔽中断,这类中断通过编程控制,开启或关闭该中断。

中断向量序号是每一个中断源的固定编号,由芯片设计产生时决定,编程时不能更改,它代表了中断服务程序入口地址在中断向量表的位置。\(IRQ\)中断号是非内核中断源的编号,每一个编号代表一个非内核中断源。

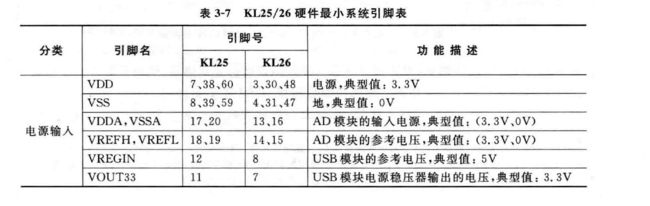

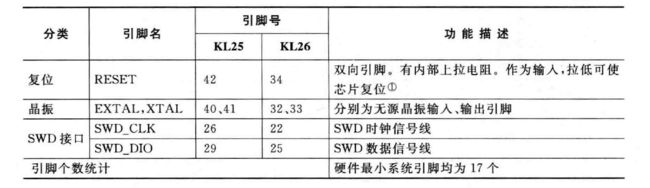

KL25的引脚功能

\(MCU\)的硬件最小系统是指包括电源、晶振、复位、写入调试器接口等可使内部程序得以运行的、规范的、可复用的核心构件系统。电路中需要大量的电源类引脚用来提供足够的电流容量同时保持芯片电流平衡,所有的电源引脚必须外接适当的滤波电容抑制高频噪声。

硬件最小系统引脚

GPIO及程序框架

通用I/O

所谓通用\(I/O\),也记为\(GPIO(General\ Purpose\ I/O)\),即基本输入/输出,有时也称并行\(I/O\),或普通\(I/O\),它是\(I/O\)的最基本形式。作为通用输入引脚,\(MCU\)内部程序可以通过端口寄存器获取该引脚状态。作为通用输出引脚,\(MCU\)内部程序通过端口寄存器控制该引脚状态。

上拉下拉电阻的基本接法

端口控制模块

\(KL25\)的大部分引脚具有复用功能,可以通过端口控制模块提供的寄存器编程指定其为某一具体功能。

\(PORT\)模块内含三类寄存器,分别是引脚控制寄存器\((Pin\ Control\ Register)\),全局引脚控制寄存器\((Global\ Pin\ Control Register)\)、中断状态标志寄存器\((Interrupt\ Status\ Flag\ Register)\)。

\(KL25\)芯片有\(5\)个端口\(A\sim E\),每个端口有\(32\)个引脚控制寄存器\(PORTx\_PCRn\)(其中\(x=A\sim E,n=0\sim 31\)),两个全局引脚控制寄存器\((PORTx\_GPCLR、PORTx\_GPCHR)\),一个中断状态标志寄存器\(PORTx\_ISFR\)。

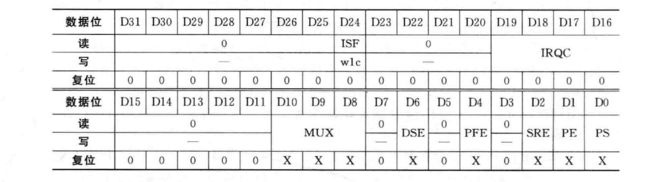

引脚控制寄存器

引脚复用控制字段,它决定引脚复用何种功能。

每个端口都有\(32\)个引脚控制寄存器\(PORTx\_PCRn\)。端口\(x\)的每个引脚控制寄存器\(PORTx\_PCRn=\) \(=4004\_9000+x\times1000+n\times 4(x=A\sim E,对应0\sim 4,n=0\sim 31)\)。

其中,\(X\)表示复位后状态不确定。下面给出相关功能说明,未说明的位或者字段为保留(只读,值为\(0\))。

\(D24(ISF)\)——中断状态标志(只读)。数字引脚模式下有效。\(ISF=0\),未检测到引脚中断;\(ISF=1\),检测到引脚中断。向该位写\(1\),可清楚中断状态标志。若引脚配置为\(DMA\)请求方式,在完成\(DMA\)请求传输后,将自动清楚中断状态标志。如果引脚被配置为电平触发的中断,引起中断的电平若一直有效,该标志将一直保持置位,即使被清楚后也会立即置位。

\(D19\sim D16(IRQC)\)——中断配置情况(读/写)。数字引脚模式下有效。\(IRQC=0000\),关闭引脚中断\(/DMA\)请求;\(IRQC=0001\sim 0011\)分别对应上升沿、下降沿、沿跳变、触发\(DMA\)请求;\(0100\)保留;\(1000\sim 1100\)分别对应逻辑低电平(逻辑\(0\))、上升沿,下降沿,沿跳变、高电平(逻辑\(1\)),触发引脚中断。其他值保留。特别注意:不是所有\(KL25\)的引脚均可配置为中断功能,只有\(A,D\)口的引脚具有上述这种中断功能。

\(D10\sim D8(MUX)\)——引脚复用控制(读/写)。不是所有引脚都支持引脚复用槽。\(MUX=000\),引脚不配置(模拟引脚);\(MUX=001\),配置引脚为通用输入输出\((GPIO)\)功能;\(MUX=010\sim 111\),分别配置引脚的功能为第\(2\)到第\(7\)功能(具体功能见芯片参考手册\(10.3\)节)。

\(D6(DSE)\)——驱动能力使能位(读/写)。表名引脚被配置为数字输出时的驱动能力状况,数字引脚模式下有效。\(DSE=0\),低驱动能力;\(DSE=1\),高驱动能力。由数据手册可知\(KL25\)低驱动能力是\(5mA\),高驱动能力是\(18mA\)。但并不是所有引脚都可配置为高驱动能力。

\(D4(PFE)\)——无源滤波使能位(读/写)。数字引脚模式下有效。\(PFE=0\),相应的引脚禁止无源输入滤波;\(PFE=1\)。

\(D2(SRE)\)——转换速率使能位(读/写)。数字引脚模式下有效。\(0\)——引脚配置成快转换速率。\(1\)——引脚配置成慢转换速率。

\(D1(PE)\)——上拉或下拉使能位(读/写)。数字引脚模式下有效。\(0\)——相应的引脚关闭内部上拉或下拉电阻;\(1\)——相应的引脚启用内部上拉或下拉电阻,引脚最为数字输入。

\(D0(PS)\)——上拉或下拉选择(读/写)。数字引脚模式下有效。\(PS=0\),如果\(PE=1\),引脚下拉电阻使能;\(PS=1\),如果\(PE=1\),引脚上拉电阻使能。\(KL25\)内部上下拉电阻大小为\(20\sim 50k\Omega\)。

全局引脚控制寄存器

每个端口有两个全局控制引脚寄存器,为只写寄存器。全局引脚控制寄存器(低)\(PORTx\_GPCLR\),地址\(=4004\_9080+x\times 1000\);全局引脚控制寄存器(高)\(PORTx\_GPCHR\),地址\(=4004\_9084+x\times 1000\)。

每个寄存器的高\(16\)位被称为全局引脚写使能字段\(GPWE\),低\(16\)位被称为全局引脚写数据字段\(GPWD\)。若\(GPWE=0xFFFF\),则\(GPWD\)字段的\(16\)位就被写入到一整组引脚控制寄存器的低\(16\)位中。

中断状态标志寄存器

每个端口都有一个中断状态标志寄存器\(PORTx\_ISFR\),地址\(=4004\_90A0+x\times 1000\)。

数字引脚模式下,每个引脚的中断模式可以独立配置,在引脚控制寄存器\(IRQC\)字段可配置选择。

每个端口的中断状态标志寄存器,对应该口的\(32\)个引脚,相应为\(1\),表明配置的中断已经被检测到,反之没有。各位具有写\(1\)清\(0\)特性。

GPIO模块——对外引脚与内部寄存器

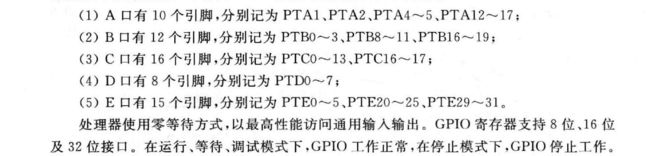

\(80\)引脚封装的\(KL25\)芯片的\(GPIO\)引脚分为\(5\)个端口,标记为\(A、B、C、D、E\),共含有\(61\)个引脚。

每个\(GPIO\)端口均有\(6\)个寄存器,\(5\)个\(GPIO\)端口共有\(30\)个寄存器。 \(A、B、C、D、E\)各口寄存器基地址分别为\(400F\_F000h、400F\_F040h、400F\_F0080h、400F\_F0C0h、400F\_F100h\),所以各口基地址相差\(40h\)。\(PORTx=400F\_F000+x\times 40\)。每个寄存器有\(32\)位,对应\(32\)个引脚输入输出模式。

GPIO基本编程步骤

- 通过端口控制模块的引脚控制寄存器\(PORTx\_PCRn\)的引脚复用字段\((MUX)\)设定其为\(GPIO\)功能(即令\(MUX=001\))。

- 通过\(GPIO\)模块相应端口的“数据方向寄存器”来指定相应引脚为输入或输出功能。若指定位为\(0\),则对应引脚为输入;若指定位为\(1\),则对应引脚输出。

- 若是输出引脚,则通过设置“数据输出寄存器”来指定相应引脚输出低电平或高电平。也可通过其他寄存器实现。

- 若是出入引脚,则通过“数据输入寄存器”获得引脚的状态。

需要进一步说明的是,这样编程只是为了理解\(GPIO\)的基本编程方法,实际并不使用,实际要把底层硬件的操作用构件把它们封装起来,给出函数名与接口参数。