FPGA定点小数计算(Verilog版)第三篇——除法运算(一)

更多精彩内容,请微信搜索“FPGAer俱乐部”关注我们。

定点小数除法运算,相比加法和乘法来说要复杂很多了,但是算法的基本思想还是很简单的。和整数除法类似,算法的核心思想就是,将除法运算转换为移位和减法运算。从具体实现的角度来看,一般有两种方式:

-

一种是除数不变,扩展并移位操作被除数

-

另一种是被除数不变,扩展并移位操作除数

本文采用的是第一种方法:

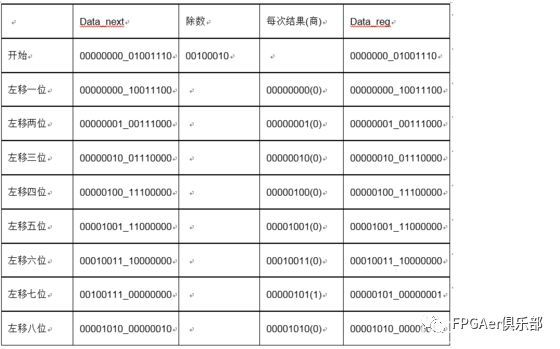

假设被除数与除数都是八位数据,这里的算法是:

将被除数,扩展成16位的数据,低8位为被除数的值,高八位的值全为0。有开始信号,对16位数据data赋值,然后开始运算。比较data的高八位和除数的值,如果大于0,说明被除数大,将此时商置1,赋值给data的最低位,然后将被除数高八位减去除数。然后将data向左移位一位,继续比较。最终计算8次后。Data的高8位数据就为所求的余数,低八位就为所求的商。

原理说白了就是:先移位,在比较(作差),迭代八次……

重要说明:本算法只支持正数,整数除法,需提前指定被除数和除数位数,且除数和被除数位数需相等。(改进的算法会在后期和大家分享)

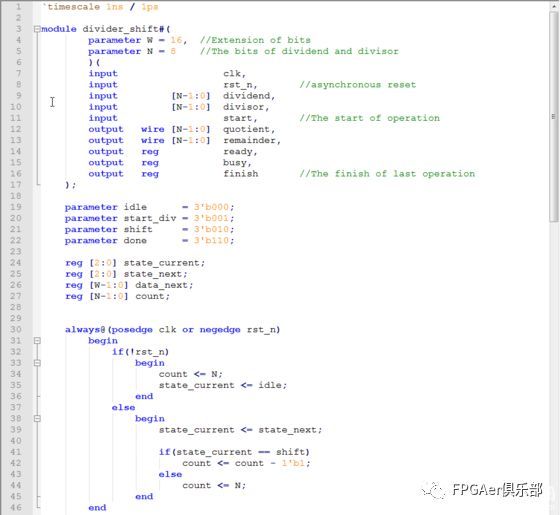

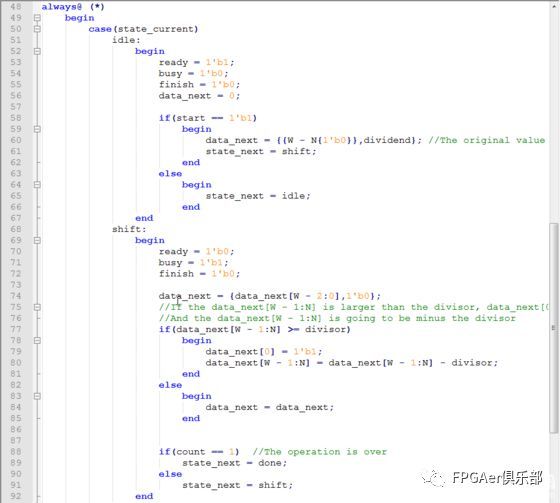

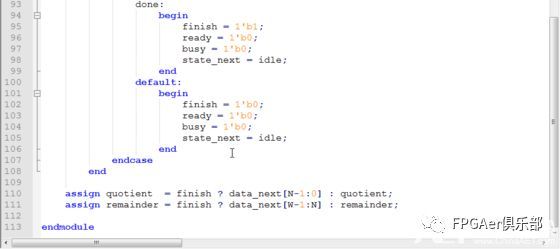

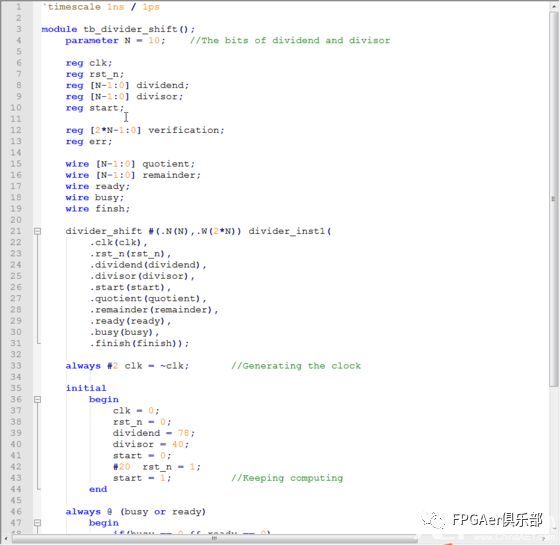

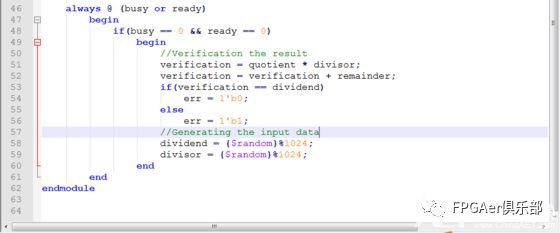

ChinaAET的代码语言功能太low,而且还不支持VerilogHDL,所以代码就直接贴图了:

下面是Testbench:

以及ActiveHDL的脚本文件:

仿真结果如下:

使用Synplify Pro综合并Map之后得到(Diamond中,MachXO3 6900C):

Design Summary

Number of registers: 42 out of 7485 (1%)

PFU registers: 42 out of 6864 (1%)

PIO registers: 0 out of 621 (0%)

Number of SLICEs: 32 out of 3432 (1%)

SLICEs as Logic/ROM: 32 out of 3432 (1%)

SLICEs as RAM: 0 out of 2574 (0%)

SLICEs as Carry: 15 out of 3432 (0%)

Number of LUT4s: 63 out of 6864 (1%)

Number used as logic LUTs: 33

Number used as distributed RAM: 0

Number used as ripple logic: 30

Number used as shift registers: 0

Number of PIO sites used: 38 + 4(JTAG) out of 207 (20%)

Number of block RAMs: 0 out of 26 (0%)

Number of GSRs: 1 out of 1 (100%)

本文转载自:http://blog.chinaaet.com/justlxy/p/5100052068,如涉及侵权,请私信小编删除。

============华 丽 的 分 割 线============

想加入我们FPGA学习交流群吗?可以长按或扫描以下二维码,审核通过后我们邀请您加入。

这些微信群旨在打造一个提供给FPGA工程开发人员及兴趣爱好者(统称“FPGAer”)进行技术交流、答疑解惑和学习的平台。而且我们也将会通过网络举办FPGA技术讲座,分享相关研究文献。

了解更多FPGA知识可以长按或扫描以下二维码关注“FPGAer俱乐部”。