ISE 工程调用PLL锁相环生成四种不同类型的时钟

第一步,用ise建立工程 ,这里不再赘述

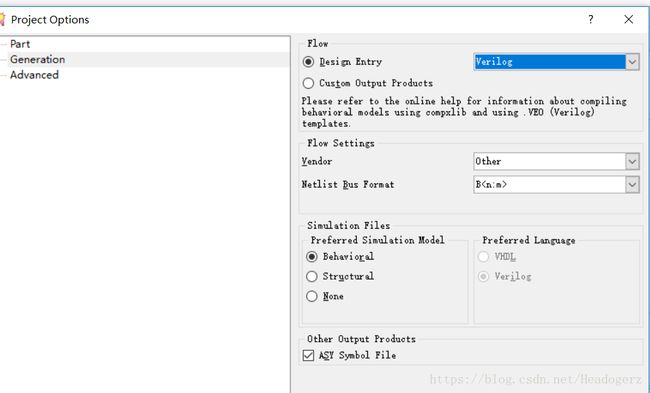

第二步,建立PLL工程,必须建立IP核工程才可以调用PLL。ip核在tools目录下。这里需要注意在配置完选型,需要将语言修改为verilog。

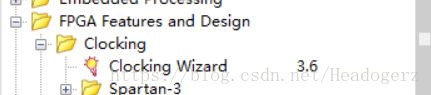

第三步,双击clocking,进行需求配置。

第四步,老师课内配置如下

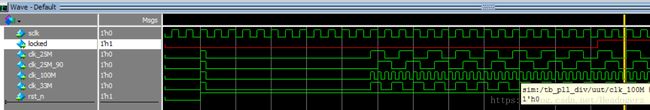

注意,没有使用PLL中的复位,只是使用了锁存位即locked

第五步,将生成的IPcord记住所在文件位置,找到.xco文件添加到工程中。接着要使用模块就需要有一个顶层模块。new source添加格式为verilog module 找到ip核下的.veo文件这个属于例化模板。new source 文件需要用到一下语言。例化到new模块中。

clk_div_4 instance_name

(// Clock in ports

.CLK_IN1(CLK_IN1), // IN

// Clock out ports

.CLK_25M(CLK_25M), // OUT

.CLK_25M_90(CLK_25M_90), // OUT

.CLK_100M(CLK_100M), // OUT

.CLK_33(CLK_33), // OUT

// Status and control signals

.LOCKED(LOCKED)); // OUT

附本人的new source程序

module div_4_25M(

input wire sclk,

input wire rst_n,

output wire clk_25M,clk_25M_90,clk_100M,clk_33M,

output wire locked

);

clk_div_4 instance_name

(// Clock in ports

.CLK_IN1(sclk), // IN

// Clock out ports

.CLK_25M(clk_25M), // OUT

.CLK_25M_90(clk_25M_90), // OUT

.CLK_100M(clk_100M), // OUT

.CLK_33(clk_33M), // OUT

// Status and control signals

.LOCKED(locked)); // OUT

endmodule

第六步,对模块进行仿真,检查是否达到要求。

附本人当时写的测试文件(直接使用ise添加仿真文件会简单很多)

`timescale 1ns/1ns

module tb_clk_25MM;

reg sclk;

wire clk_25M,clk_25M_90;

wire clk_100M,clk_33M;

wire locked;

initial

begin

#200 sclk=0;

end

always #10 sclk=~sclk;

CLK_25MM clk_25MM_inst(

.sclk (sclk),

.clk_25M (clk_25M),

.clk_25M_90 (clk_25M_90),

.clk_100M (clk_100M),

.clk_33M (clk_33M),

.locked (locked)

);

endmodule