浅析AMBA规范以及AMBA 5 AHB接口和AMBA 3 APB接口

官方文档:

ARM® AMBA® 5 AHB Protocol.pdf

AMBA™ 3 APB Protocol.pdf

Multi-layer AHB.pdf

一、AMBA简介

1、AMBA (Advanced Microprocessor Bus Architecture):

ARM® AMBA® 协议是用于连接和管理片上系统 (SoC) 中功能模块的开放标准和片上互连规范。它有助于首次开发带有大量控制器和外设的多处理器设计。AMBA 基于 CHI™、ACE™、AXI™、AHB™、APB™ 和 ATB™ 等规范为 SoC 模块定义了共同的框架结构,这有助于设计的重复使用。

2、AHB (Advanced High-Performance Bus):主要用于单片机中的系统总线。

主要用于Cortex-M家族的处理器。

3、APB (Advanced Peripheral Bus):用于低带宽的外设之间的连接。

4、ATB (Advanced Trace Bus):用于在芯片间传输 trace 数据。

5、ACE (AXI Coherency Extensions):用于智能手机中的 big.LITTLE™ 系统。

主要用于Cortex-A15、Cortex-A17、Cortex-A7架构的处理器。

6、AXI (Advanced eXtensible Interface):用得最多的 AMBA 接口,在复杂的片上系统中至多连接100个主、从模块。

主要用于Cortex-A、Cortex-R、Mali v500、Mali T760系列的处理器。

7、CHI (Coherent Hub Interface):用于许多服务器与网络应用程序所需要的高可扩展性的片上系统。

主要用于Cortex-A72、Cortex-A57、Cortex-A53架构的处理器。

二、AMBA 5 AHB 接口

1、概览:

AMBA AHB总线接口适用于高性能的综合设计。它定义了主模块(Cortex™-M 内核、DMA 存储器、DMA 外设、以太网 DMA、USB OTG HS DMA等)、连接组件和从模块(内部 Flash、内部 SRAM、AHB-APB 总线桥、APB 外设、FSMC等)之间的接口。

大多数挂在总线上的模块(包括CPU)只是单一属性的功能模块:主模块或者从模块。主模块是向从模块发出读写操作的模块,如CPU、DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。

在高性能、高时钟频率的系统中AMBA AHB具有以下四个特点:

a. 突发传输;

b. 单个时钟边沿操作;

c. 非三态的实现方式;

d. 64、128、256、512和1024位带宽可调的数据总线。

*注:突发传输(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度(Burst Lengths,简称BL)。

大部分AHB从模块是内部存储器、外部存储器接口和高带宽外设。虽然低带宽的外设也能作为AHB的从模块,但是从系统性能的角度来考虑,它们应该位于AMBA APB总线上。桥接AHB和APB总线使用作为AHB从模块的APB桥。

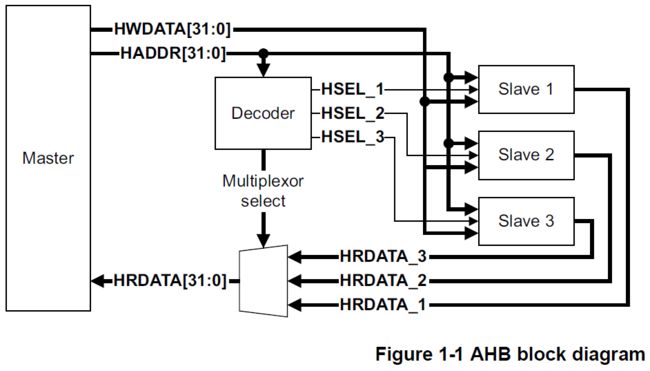

Figure 1-1展示了一个由一个主模块和三个从模块组成的AHB总线系统。这个总线的连接逻辑由一个地址译码器和一个由从到主的多路复用器组成。译码器根据从主模块输出的地址选择对应的从模块,并且使多路复用器挑选出对应从模块输出的数据返回给主模块。

*注:Figure 1-1仅仅展示了主要的地址和数据总线以及一般情况下的数据路由,不是所有的信号都被展示出来了。

在使用一个在不同主模块和对应从模块之间提供仲裁和路由信号的连接组件的情况下,AHB也支持多个主模块的设计。具体请参考Multi-layer AHB规范。

2、AHB接口各部分说明:

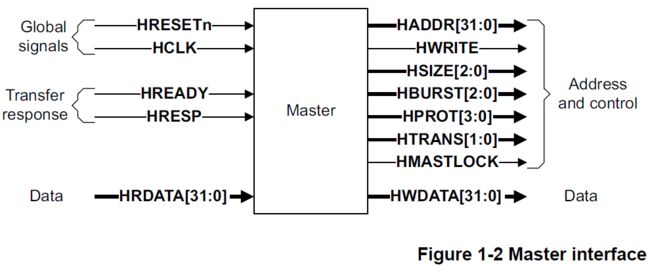

主模块提供了用于初始化读写操作的地址和控制信息。Figure 1-2展示了主模块的接口:

*注:Figure 1-2没有展示在AHB5协议中新增加的信号。

在系统中从模块用于响应主模块的初始化操作。从模块根据从译码器发出的HSELx选择信号响应总线中的传输指令。

从模块返回如下两个信号给主模块:

a. 完成传输或者继续传输;

b. 传输成功或者传输失败。

Figure 1-3展示了从模块的接口:

*注:Figure 1-3没有展示在AHB5协议中新增加的信号。

连接组件负责连接系统中的主模块和从模块。单个主模块的系统仅仅需要使用一个译码器和多路复用器。而多个主模块的系统需要在不同主模块和对应从模块之间提供仲裁和路由信号。包括地址、控制以及写数据信号的路由。

3、AHB接口工作过程:

主模块通过驱动地址和控制信号启动整个传输过程。这些信号提供传输的地址、方向和位宽信息,以及表明该次传输为突发传输模式中的哪一种。可以有以下三种传输模式:

a. 单次传输;

b. 没有地址边界的递增突发传输(incrementing bursts);

c. 有特定地址边界的包装突发传输(wrapping bursts)。

写数据总线将数据从主模块搬运到从模块,读数据总线将数据从从模块搬回主模块。

每次传输包含以下两个阶段:

地址传输阶段:一个地址和控制信号的时钟周期;

数据传输阶段:一个或多个数据传输的时钟周期。

由于从模块无法延长地址传输阶段的时间,因此所有从模块必须在规定时间内完成地址的采集。但是从模块可以使用HREADY信号向主模块请求延长数据传输阶段的时间。当该HREADY信号为低电平的时候,传输过程将被插入等待状态,这样从模块就有额外的时间可以提供或者采集数据。

从模块使用HRESP信号表明传输成功或者是失败。

4、AHB总线上各个信号的说明:

a. 全局信号:

HCLK:时钟信号,由时钟源产生。所有信号均在HCLK信号的上升沿传输。

HRESETn:复位信号,由复位控制器产生。低电平有效,复位整个系统和总线。

b. 主模块信号(由主模块产生的信号):

HADDR[31:0]:32位系统地址总线,该信号发送至从模块和译码器。

HBURST[2:0]:单次传输或者突发传输类型,该信号发送至从模块。支持4次、8次或者16次的突发长度。支持递增突发传输(incrementing bursts)和包装突发传输(wrapping bursts),并且支持未定义长度的递增突发传输。

HMASTLOCK:主模块锁定,该信号发送至从模块。如果为高电平则代表当前传输的信号为被锁定传输序列的一部分。该信号与地址和控制信号同步更新。

HPROT[3:0]:保护控制信号,该信号发送至从模块。提供了额外的如何处理系统中总线上的存取指令的信息。该信号表明总线上传输的是获取操作码的指令还是存取数据的指令,以及传输的是特权模式下的存取指令还是用户模式下的存取指令。

HPROT[6:4]:HPROT信号的三位扩展,增加了扩展的存储器类型,该信号发送至从模块。该信号扩展仅仅在AHB5协议中的Extended_Memory_Types选项为True的时候被支持。

HSIZE[2:0]:表明传输数据的大小,该信号发送至从模块。可以为一个字节、半字或者一个字,最大不允许超过1024位。

HNONSEC:表明当前处于非安全传输模式还是安全传输模式,该信号发送至从模块和译码器。该信号仅仅在AHB5协议中的Secure_Transfers选项为True的时候被支持。

HEXCL:独立传输模式,该信号发送至独立存取监视器(Exclusive Access Monitor)。表明当前传输的数据为独立存取序列的一部分。该信号仅仅在AHB5协议中的Exclusive_Transfers选项为True的时候被支持。

HMASTER[3:0]:主模块标识符,该信号发送至独立存取监视器以及从模块。如果主模块具有多个独立存取能力的线程,则主模块生成该信号。为确保每个主模块有唯一的标识符,连接器可以修改该信号。该信号仅仅在AHB5协议中的Exclusive_Transfers选项为True的时候被支持。

HTRANS[1:0]:表明当前的传输类型,该信号发送至从模块。可以取IDLE、BUSY、NONSEQUENTIAL、SEQUENTIAL四种类型。

HWDATA[31:0]:主模块向从模块进行写操作期间写数据总线传输的数据,该信号发送至从模块。写数据总线的位宽不一定为32,可以为其他值。不过建议数据总线位宽最少为32位,这样可以操作更高的带宽。

HWRITE:表明传输的方向,该信号发送至从模块。高电平表示写操作,低电平表示读操作。该信号与地址信号同步更新。但是在突发传输模式时,该信号必须保持不变。

c. 从模块信号(由从模块产生的信号,全部发送至多路复用器):

HRDATA[31:0]:在读操作期间被选中的从模块向连接多路复用器的读数据总线发送的数据。然后多路复用器将数据传输给主模块。读数据总线的位宽不一定为32,可以为其他值。不过建议数据总线位宽最少为32位,这样可以操作更高的带宽。

HREADYOUT:如果为高电平则表明传输结束,如果为低电平则表明继续传输。

HRESP:传输响应信号,通过多路复用器之后向主模块提供额外的传输状态信息。如果为低电平则表明传输状态为OKAY,如果为高电平则表明传输状态为ERROR。

HEXOKAY:表明独立传输是否成功的信号。该信号仅仅在AHB5协议中的Exclusive_Transfers选项为True的时候被支持。

d. 译码器信号(由译码器产生的信号):

HSELx:在系统中字母“x”必须被替换为每个从模块唯一的标识符,例如“HSEL_S1”、“HSEL_S2”和“HSEL_Memory”,该信号发送至从模块。每一个从模块有它自己的选择信号HSELx。该信号表明当前传输的信号是针对被选中的从模块。当一个从模块刚刚被选中,它必须先检查HREADY信号以确定之前的总线传输已经完成。然后从模块才能相应当前的传输信号。HSELx信号与地址总线的译码器相结合。

e. 多路复用器信号(由多路复用器信号产生的信号):

HRDATA[31:0]:被译码器所选中的读数据总线,该信号发送至主模块。

HREADY:如果为高电平则表明之前主模块和所有从模块之间的传输已经完成,该信号发送至主模块和从模块。

HRESP:被译码器选中的传输信号的相应,该信号发送至主模块。

HEXOKAY:表明被译码器选中的独立传输是否成功的信号,该信号发送至主模块。

*注:由于HRDATA[31:0]、HRESP和HEXOKAY三个信号经过多路复用器之后信号的名称并没有改变,所以有关这三个信号更多的描述请参考上面的有关从模块信号的描述。

AHB总线的具体传输方式以及时序等更多信息请阅读官方文档,这里不做赘述。

三、AMBA 3 APB接口

1、概览:

APB是AMBA 3协议族的一部分。它提供了一个降低了复杂度并且为低功耗而优化过的接口。

APB可以连接任何低带宽的并且不需要高性能的流水线的总线接口的外设。APB是一个不包含流水线的协议。

APB总线桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

所有状态转换仅在时钟信号的上升沿触发,这使得在程序设计流程中使能一个集成在APB中的外设是非常容易的。每次数据传输至少占用两个时钟周期。

APB可连接AHB-Lite和AXI接口。你可以使用它来存取外设的可编程控制寄存器。

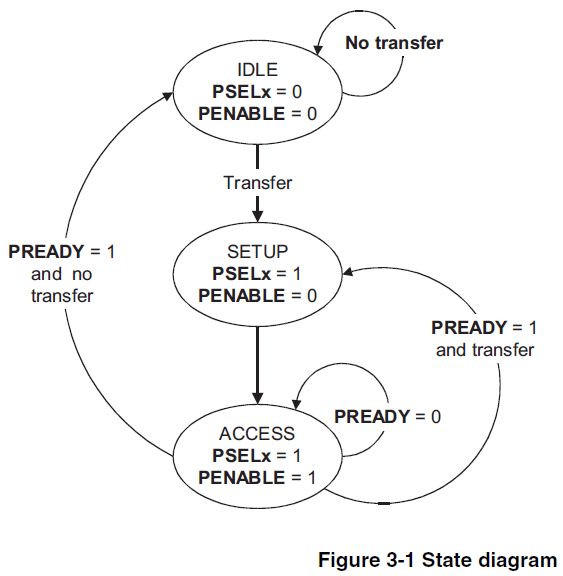

Figure 3-1展示了APB总线的状态转换图:

这个状态机有以下三种状态:

IDLE:APB的默认状态。如果APB总线桥没有数据需要传输,则APB总线一直保持这个状态。

SETUP:当要传输数据时总线必须转换为SETUP状态,此时对应的选择信号PSELx被APB总线桥置1。总线仅仅保持SETUP状态一个时钟周期,然后在下一个时钟信号的上升沿跳变到ACCESS状态。

ACCESS:使能信号PENABLE在ACCESS状态下被APB总线桥置1。在SETUP状态转变为ACCESS状态的期间地址、写、选择和写数据的信号必须保持稳定。退出ACCESS状态是由从模块发出的PREADY信号控制的。如果从模块使PREADY信号保持低电平,则下一个时钟周期保持ACCESS状态。如果从模块使PREADY信号保持高电平,在没有数据需要继续传输的情况下APB总线退出ACCESS状态进入IDLE状态,在需要继续传输数据的情况下APB总线直接进入SETUP状态。是否需要继续传输数据由APB总线桥控制。

2、APB总线各个信号的说明:

PCLK:时钟信号,由时钟源产生。APB总线的状态转换仅在PCLK信号的上升沿触发。

PRESETn:复位信号,与系统总线的复位信号相同。APB总线的复位信号是低电平有效。这个信号一般与系统总线的复位信号直接相连。

PADDR:地址信号,由APB总线桥产生。这是APB接口的地址总线,最大32位宽。

PSELx:选择信号,由APB总线桥产生。每一个外设(从模块)都有一个选择信号,它代表着对应从模块被选中,并且需要传输数据。

PENABLE:使能信号,由APB总线桥产生。它代表着APB总线将在下一个时钟信号的上升沿传输数据。

PWRITE:方向信号,由APB总线桥产生。高电平代表着写数据,低电平代表着读数据。

PWDATA:写数据信号,由APB总线桥产生。在PWRITE信号为高电平的时候被写入的数据,最大32位宽。

PREADY:准备信号,由从模块产生。这个信号代表从模块的读写操作已经完成。

PRDATA:读数据信号,由从模块产生。在PWRITE信号为低电平的时候读出的数据,最大32位宽。

PSLVERR:错误信号,由从模块产生。从模块不强制要求具有PSLVERR信号引脚,此时APB总线桥的PSLVERR信号引脚需要接低电平。

APB总线具体的读写数据以及错误响应的时序请阅读官方文档,这里不做赘述。

四、附:Multi-layer AHB方案

1、概览:

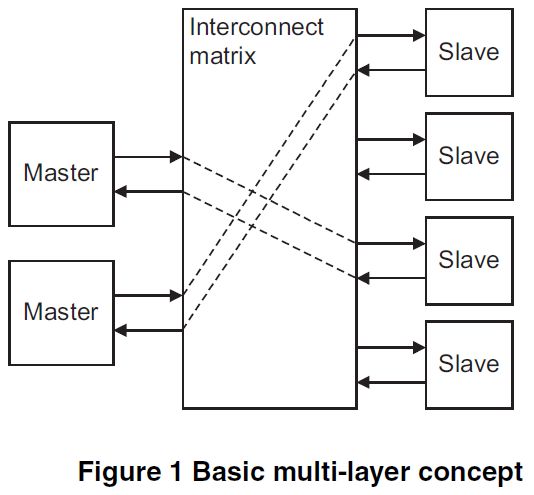

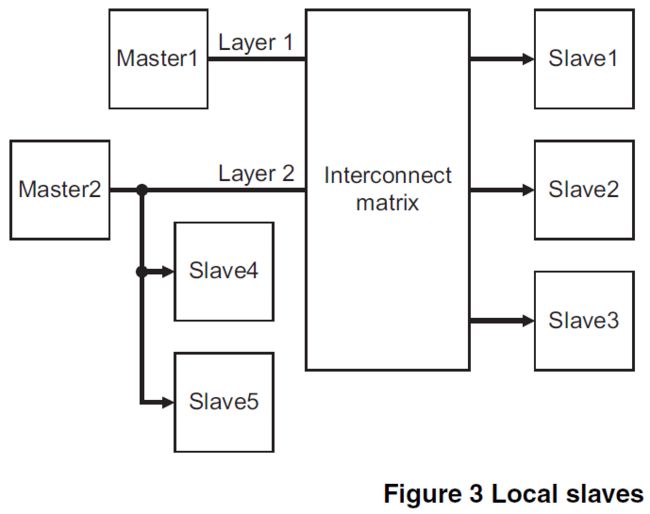

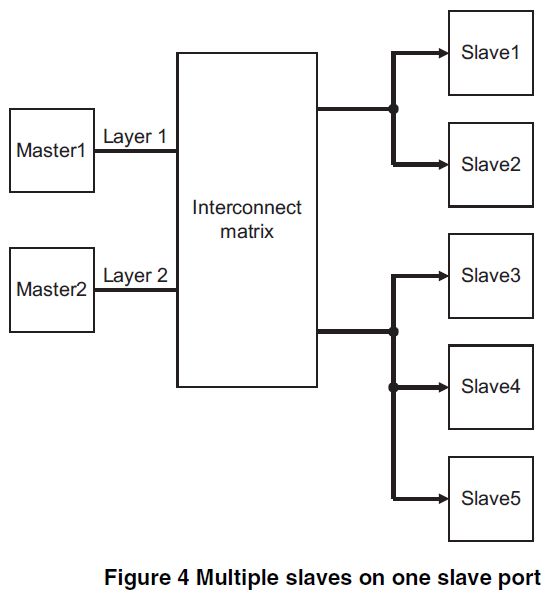

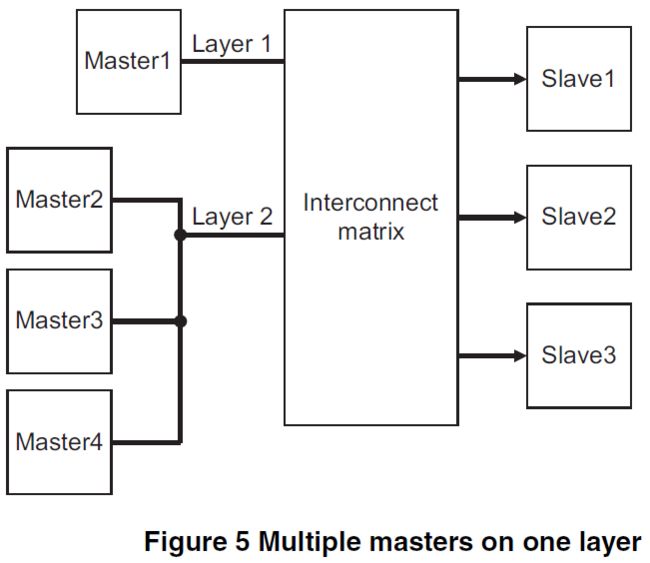

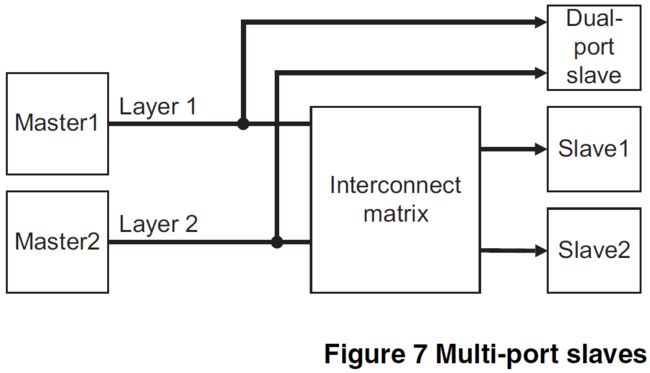

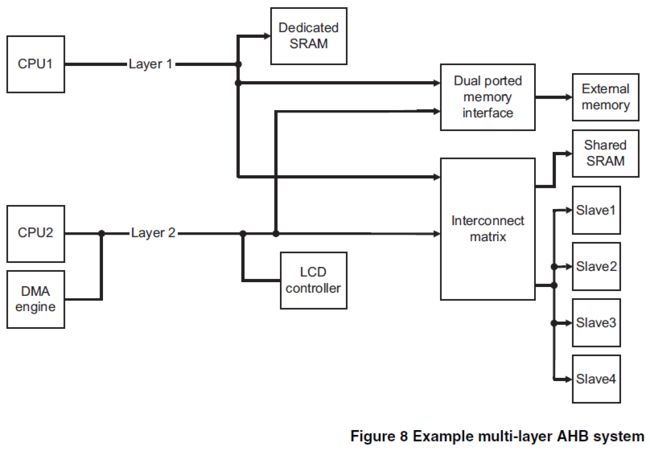

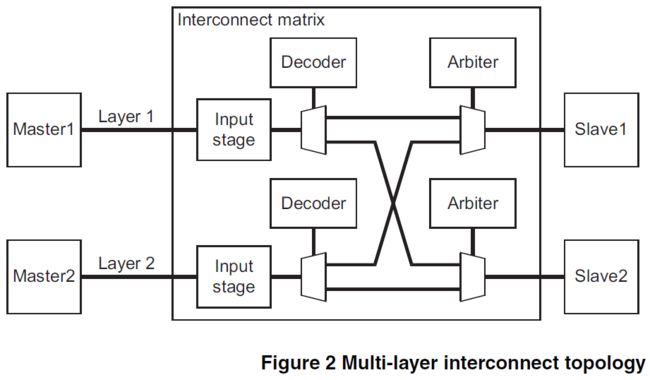

Multi-layer AHB是一个基于AHB协议的互连方案。它使系统中的多个主模块能够平行访问多个从模块,这归功于一个更为复杂的互连矩阵(interconnect matrix)。

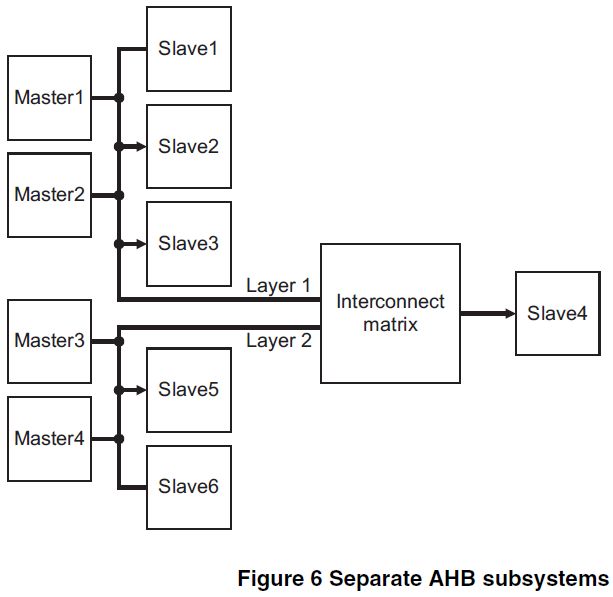

多层次系统最简单的实现方式是每个主模块都有自己的AHB层次(AHB

layer),并且使用互连矩阵连接从模块,如Figure 2所示:

在这个互连矩阵内:

a. 每个层次都有自己的用于选择从模块的译码级(Decode stage);

b. 多路复用器为从模块选择合适的主模块。

如果两个层次同时访问同一个从模块,那么互连矩阵内的仲裁器将决定哪个层次享有更高的优先级。那个未取得访问权限的层次需要使用HREADY信号进入等待状态,直到取得访问权限,等待的同时该层次的输入级(Input Stage)将保存一份流水线地址和控制信息的备份。

每个从模块都有自己的仲裁器,并且可以使用不同的仲裁方案,比如:

a. 循环制算法:每一次传输或者突发传输后换一个输入层次;

b. 固定优先级算法:仲裁器使用一个固定的优先级表,高优先级的层次总是优先于低优先级的层次取得访问权限。

互连矩阵的输入输出端口的数量可以根据系统需求灵活变动。

本文参考链接:

AMBA总线袁劲松新浪博客

【博客大赛】AHB重点难点总结-绝对值得你看 - sunyzz的博客 - EDN China博客

Duanxx的STM32学习:stm32的总线AMBA、AHB、APB - 系统其他栏目 - 红黑联盟

AMBA 开放规格 - ARM

AMBA Protocol – Architecture – ARM Developer