Linux系统时间不准问题分析

Linux系统时间不准问题分析

CPU:PowerPC P1020RDB-PC

OS: Linux-2.6.35

问题:系统跑一段时间后,执行date和hwclock分别获取系统时钟和rtc时钟,出现差异,

差异为sysclk时间比rtc每分钟慢0.6秒。误差是比较大了。

一、问题分析

1. 转换误差

2. 时钟不稳定

3. 时钟频率不对

二、结构分析

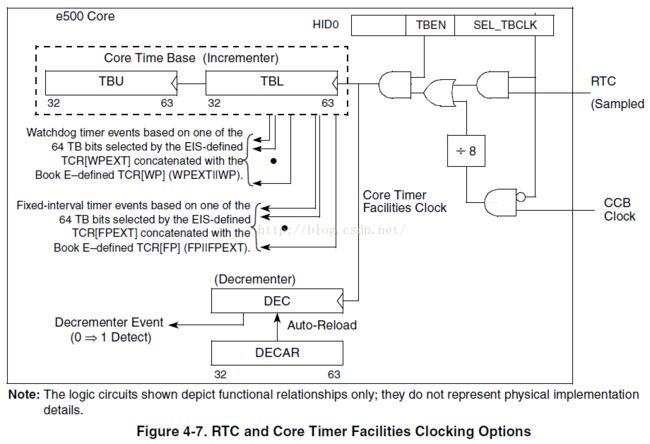

下面是CPU内部的核心时钟组成

如上,Core Time Base(TBU+TBL)是一个时钟计数器,里面存放的cycles随着CCB Clock分频出来的时钟一直递增,cycles = 系统时间*HZ。

DEC 作为时钟事件的中断触发,按照时钟频率递减,减到0后产生Decrementer Event事件,可以在中断触发时由程序写入初始值,也可以设置为Auto-Reload DECAR的值。这一块还没具体分析有什么用。

上图中的RTC并没有使用。

当前系统参数

外部时钟 = 66.0M

CCB Clock = 400M

SYSCLK = 800M

从CCB 8分频出来给Core Time Base和 DEC 的时钟为 50M

接下来来看一下Linux系统内时间管理的内容

clock source用于为linux内核提供一个时间基线,实际上就是一个时间相关的结构体,如果你用linux的date命令获取当前时间,内核会读取当前的clock source,转换并返回合适的时间单位给用户空间。在硬件层,它通常实现为一个由固定时钟频率驱动的计数器(上面的TimeBase),计数器只能单调地增加,直到溢出为止。系统启动时,内核通过硬件RTC获得当前时间,并设置到计数器内,在这以后,内核通过选定的时钟源更新实时时间信息(墙上时间),而不再读取RTC的时间。

clock source可以有多个,系统启动时会检查所有clocksource,然后将精度最好的时钟源设为当前时钟源。每个时钟源的精度由驱动它的时钟频率决定,可以用如下命令查看clock source:

[root@t:home]#cat/sys/devices/system/clocksource/clocksource0/available_clocksource

timebase

[root@t:home]#cat/sys/devices/system/clocksource/clocksource0/current_clocksource

timebase

看一下我们系统中timebase时钟源的定义 time.c (arch/powerpc/kernel)

static struct clocksource clocksource_timebase = {

.name = "timebase",

.rating = 400,

.flags = CLOCK_SOURCE_IS_CONTINUOUS,

.mask = CLOCKSOURCE_MASK(64),

.shift = 22,

.mult = 0, /*To be filled in */

.read = timebase_read,

};

.read = timebase_read,该函数就是读取TB的计数值

timebase_read是通过汇编来实现的。

static cycle_t timebase_read(structclocksource *cs)

{

return(cycle_t)get_tb();

}

static inline u64 get_tb(void)

{

returnmftb();

}

#define mftbu() ({unsigned long rval; \

asm volatile("mftbu %0" :"=r" (rval)); rval;})

三、具体分析

1.转换误差

现在我们可以获取到cycles的计数值,也知道了HZ=50M,那么根据公式很容易就得到系统时间了。

times_elapse= cycles_interval / frequency

但是,因为内核中使用除法不太方便,所以将这个公式转换成了乘法与移位操作

times_elapse = cycles_interval * mult >> shift

关于这个转换有个专门的内核函数,可以由frequency和精度值计算出mult和shift

后面再贴。

从上面clocksource_timebase的定义已经看到shift=22, mult=0(后续计算) 了,看一下mult的计算。

在clocksource_init 函数中找到mult的初始化

clock->mult= clocksource_hz2mult(tb_ticks_per_sec,clock->shift);

打印出来这个值为clock->mult =83886080

现在shift和mult的值都有了,那我们来验证一下转换的误差

就以times_elapse = 1s为例,则cycles_interval = frequency = 50000000

按照公式:

times_elapse = cycles_interval * mult >> shift

>>> (50000000*83886080)>>22

1000000000L = 1s

由此可见,将除法转换成乘法并未带来误差。

2.时钟频率不对

前面的计算都是按照CCB Clock 8分频50M来计算,但是这个50M是否准确?

那就看看这个50M到底从哪来的

time_init (/arch/powerpc/kernel/time.c)

-->ppc_md.calibrate_decr(); == generic_calibrate_decr(void)

-->get_freq("timebase-frequency",1, &ppc_tb_freq)

此处获取到的ppc_tb_freq = 50M

get_freq是从设备树中读取的,但实际的设备树中并没有timebase-frequency这个选项

最终找到uboot中 fdt.c (arch/powerpc/cpu/mpc85xx)

void ft_cpu_setup(void *blob, bd_t *bd)

{

do_fixup_by_prop_u32(blob,"device_type", "cpu", 4,

"timebase-frequency",get_tbclk(), 1);

}

由do_fixup_by_prop_u32将get_tbclk()的值填入"timebase-frequency",原来是uboot创建了这个选项,继续查找50M的来历,看看get_tbclk函数

à

#ifndef CONFIG_SYS_FSL_TBCLK_DIV

#define CONFIG_SYS_FSL_TBCLK_DIV 8

#endif

unsigned long get_tbclk(void)

{

unsigned long tbclk_div = CONFIG_SYS_FSL_TBCLK_DIV;

return (gd->bus_clk + (tbclk_div >> 1)) / tbclk_div;

}

àget_clocks

gd->bus_clk = sys_info.freqSystemBus;

àget_sys_info

unsigned long sysclk = CONFIG_SYS_CLK_FREQ;

sysInfo->freqSystemBus= sysclk;

sysInfo->freqSystemBus *= (in_be32(&gur->rcwsr[0]) >>25) & 0x1f;

上面代码可以看出get_tbclk()的原始值是从CONFIG_SYS_CLK_FREQ得来的

cpu_p1020.h(include/configs)中的定义

#define CONFIG_SYS_CLK_FREQ 66666666

而实际上外部时钟是66.0M,原来是配置文件指定错了。

系统实际参数

外部时钟 = 66.0M

CCB Clock = 396M

SYSCLK = 792M

DDR = 396M

ppc_tb_freq = 49500000

clock->mult = 84733414

clock->shift = 22

重新计算一下转换误差:

times_elapse = cycles_interval * mult >> shift

>>> (49500000*84733414)>>22

999999998L

误差为每秒2ns,已经很小了

附:内核中由除法转换成乘法的函数 clocksource.c(kernel/time)

/**

*clocks_calc_mult_shift - calculate mult/shift factors for scaled math of clocks

*@mult: pointer to mult variable

*@shift: pointer to shift variable

*@from: frequency to convert from

*@to: frequency to convert to

*@minsec: guaranteed runtime conversionrange in seconds

*

*The function evaluates the shift/mult pair for the scaled math

*operations of clocksources and clockevents.

*

*@to and @from are frequency values in HZ. For clock sources @to is

*NSEC_PER_SEC == 1GHz and @from is the counter frequency. For clock

*event @to is the counter frequency and @from is NSEC_PER_SEC.

*

*The @minsec conversion range argument controls the time frame in

*seconds which must be covered by the runtime conversion with the

*calculated mult and shift factors. This guarantees that no 64bit

*overflow happens when the input value of the conversion is

*multiplied with the calculated mult factor. Larger ranges may

*reduce the conversion accuracy by chosing smaller mult and shift

*factors.

*/

void

clocks_calc_mult_shift(u32 *mult, u32*shift, u32 from, u32 to, u32 minsec)

{

u64tmp;

u32sft, sftacc= 32;

/*

* Calculate the shift factor which is limitingthe conversion

* range:

*/

tmp= ((u64)minsec * from) >> 32;

while(tmp) {

tmp>>=1;

sftacc--;

}

/*

* Find the conversion shift/mult pair whichhas the best

* accuracy and fits the maxsec conversionrange:

*/

for(sft = 32; sft > 0; sft--) {

tmp= (u64) to << sft;

do_div(tmp,from);

if((tmp >> sftacc) == 0)

break;

}

*mult= tmp;

*shift= sft;

}

使用举例:

#include

#include

typedef unsigned int u32;

typedef unsigned long long u64;

#define NSEC_PER_SEC 1000000000L

void

clocks_calc_mult_shift(u32 *mult, u32*shift, u32 from, u32 to, u32 maxsec)

{

u64 tmp;

u32 sft, sftacc= 32;

/*

* * Calculate the shift factor which is limiting the conversion

* * range:

* */

tmp = ((u64)maxsec * from) >> 32;

while (tmp) {

tmp >>=1;

sftacc--;

}

/*

* * Find the conversion shift/mult pair which has the best

* * accuracy and fits the maxsec conversion range:

* */

for (sft = 32; sft > 0; sft--) {

tmp = (u64) to << sft;

tmp += from / 2;

//do_div(tmp, from);

tmp = tmp/from;

if ((tmp >> sftacc) == 0)

break;

}

*mult = tmp;

*shift = sft;

}

int main()

{

u32 tsc_mult;

u32 tsc_shift ;

u32 tsc_frequency = 2127727000/1000; //TSC frequency(KHz)

clocks_calc_mult_shift(&tsc_mult,&tsc_shift,tsc_frequency,NSEC_PER_SEC/1000,600*1000);//NSEC_PER_SEC/1000是因为TSC的注册是clocksource_register_khz

fprintf(stderr,"mult = %d shift = %d\n",tsc_mult,tsc_shift);

return 0;

}

http://blog.chinaunix.net/uid-24774106-id-3909829.html