SPI接口扫盲 SPI定义/SPI时序(CPHA CPOL)

SPI接口扫盲

百度上找出来的SPI接口中文描述都说的太过简略,没有一篇文档能够详尽的将SPI介绍清楚的。wikipedia英文版[注释1]中,SPI接口介绍的很好,但是毕竟是英文版,读起来终究不如母语舒服,所以我结合自己的工作经验,对其进行了汉化、整理 。

SPI ( Serial Peripheral Interface,串行外设接口)是一种同步、串行通讯接口规格,常用于短距离通讯,主要是在嵌入式系统中。此接口由Mototola公司推出,已成为一种事实标准(没有统一的协议规范,但是基于其广泛的使用,根据实际使用中大家通用的习惯形成了一个类似行规的标准)。

SPI典型的应用场景包括SD卡(SD接口中包含SPI接口)和液晶显示。

SPI是一种高速的,全双工,同步的通信总线。分为主(master)、从(slave)两种模式,一个SPI通讯系统需要包含一个(且只能是一个)maser(主设备),一个或多个slave(从设备)。

SPI接口的读写操作,都是由master发起。当存在多个从设备时,通过各自的片选(slave select)信号进行管理。

硬件开发人员设计、提供的SPI接口,其实只是一个数据读写通道 ,具体读写数据所代表的意义需要在应用中定义。不像SD接口那样,对于命令有着明确详细的定义。

除了供电、接地两个模拟连接以外,SPI总线定义四组数字信号:

注释:

当只有一个maser、一个slave时,将master与slave上名字相同的4对接口两两互联,即可完成了接口的互联。如下图所示:

注释:

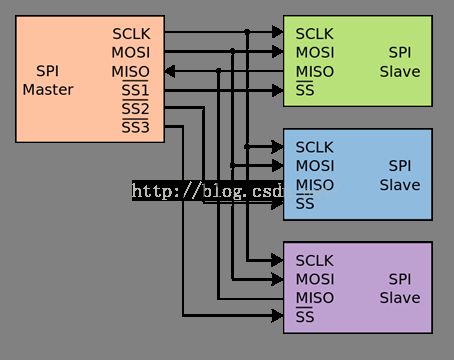

当存在一个master、多个slave时(注意,当master上有n个SS时,对应可以连接n个slave),连接方式如下图所示,注意SCLK/MOSI/MISO三个接口采取复用模式连接,不同SS单独连接对应的slave,SS信号绝不可复用:

SPI接口如何进行数据传输?SPI接口是一种典型的全双工接口,通过同步时钟SCLK的脉冲将数据一位位地传送。所以在开始通讯前,master首先要配置接口时钟(确定其通讯频率是SLAVE可以支持的,通常为数兆赫兹)。

当MASTER片选一个SLAVE时,每向SLAVE发送一个周期的SCLK信号,都会有1bit的数据从MOSI发送至slave,与此同时,slave每收到一个周期的SCLK信号,都会从MISO向master发送1bit的数据。这种全双工通讯,是由硬件保证的(MASTER与HOST中各有一个移位寄存器作为收发数据的缓存)。

SPI是一个很开放的接口,指令解析、帧大小、LSB/MSB(Least Significant Bit/Most Significant Bit)等规则并没有一个完善的定义,不同的SPI设备在这些方面的定义会有不同:

不同于SD等接口的严谨的command定义,SPI接口的master与slave之间的命令、数据解析都可以自定义,只要保证master与slave之间采用相同的规则就好。

不同SPI芯片,每次连续传输的数据量的大小(取决于MASTER、SLAVE中缓存最小的那个)常常不同。当一次连续通讯的的数据量超过帧的大小时,会出现数据丢失的现象。所以,每完成1帧的传输后,MASTER会停止接口时钟输出,master、slave读取、处理收到的数据,然后进行下一帧的传输。

在SPI接口协议中,并没有中断的定义,但是实际应用中,我们可以使用接口中断提高接口通讯速度。比如SLAVE是负责数据数据加解密的,MASTER下发一组明文给SLAVE加密,如果此时有个SLAVE输出到MASTER的中断信号,那么MASTER可以清楚的知道何时SLAVE完成了数据处理并读出处理结果,不必通过查询一遍遍的等待结束。

以上我们讲的SPI接口,一个时钟周期可以进行全双工的1bit数据通讯。实际应用中,如果对于全双工的需求不高,而且期望提高通讯速度的话,SPI有两种常见变形可供选用:

一、 两线模式的SPI

CLK与SS信号保持不变,MOSI与MISO则变形为DATA_0与DATA_1。

DATA_0与DATA_1是输入输出状态由MASTER配置的数据管脚:当MASTER打算向SLAVE中写数据时,处于输出状态;当MASTER打算从SLAVE读数据时,处于输入状态。

二、 四线模式的SPI

CLK与SS信号保持不变,MOSI与MISO删除,新增四条数据线DATA0~3。

DATA0_~3是输入输出状态由MASTER配置的数据管脚:当MASTER打算向SLAVE中写数据时,处于输出状态;当MASTER打算从SLAVE读数据时,处于输入状态。

这样一来,大大提高了单方向上数据传输的速度,但是增加了接口资源的开销。

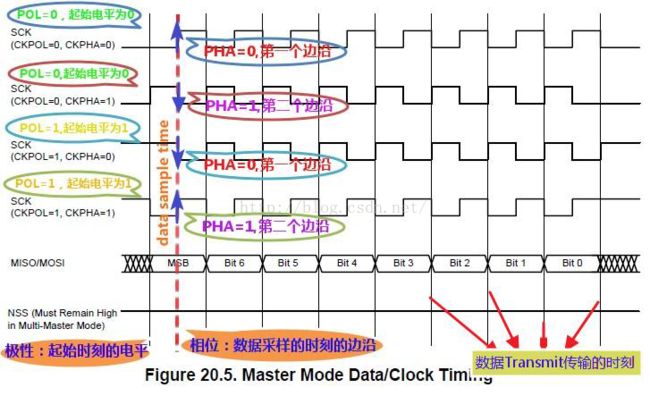

由于SPI缺乏一个统一的规范,所以在时序描述上存在一定的差异性。CPOL与CPHA的定义,有些芯片DATASHEET中描述与通用的规则是相反的,所以选型时候一定要以DATASHEET中的时序图为准。

另外,某些芯片上,关于SPI接口时序不使用CPOL/CPHA进行定义,而是使用CKP和CKE进行定义,在此不再详细解释这两个概念的意义(比较绕,这些参数看多了特容易混淆),建议直接参考时序图。

关于SPI时序的说明,之前我参考了crifan的博客,其中还有个问题待解决:

对于CPOL和CPHA这四种模式,不同的模式之间,相对来说有何优缺点,比如是否哪种模式更稳定,数据更不容易出错等等,还是不清楚。

我这里给出我的思考结果:

首先是CPOL的选择,我们从芯片设计角度开始谈这个问题。首先,如果寄存器赋值时没有特殊要求必须是下降沿触发赋值时,我们会选择上升沿触发,且时钟关闭时固定为低电平。这样一来,保证了时钟关闭时漏电最小(低电平下没有电压差,减小了漏电流IDDQ,同时上升沿触发也保证了来了时钟能够立刻采样信号,快速响应)。当然了,如果要求寄存器下降沿采样,那么时钟关闭时固定为高电平了。

借用此思想,对于CPOL的选择,如果配置可以选择的话,我建议参考MASTER与SLAVE接口IO的配置参数。如果两边都是上拉,那么建议选择CPOL为1,这样一来,当我们配置CPOL时,不会在接口上制造出一个下降沿(单SLAVE的应用场景下,SLAVE的片选有时会直接连接GND,而此时MASTER本不想通讯但是传入了一个下降沿,SLAVE那边区分不出来这是不是有效通讯);而且这样在IO上的漏电也能有效控制(没有电势差,没有电流)。如果一边上拉一边下拉,如果从功耗的角度考虑,建议选择下拉电阻更小(漏电流更大)的IO的上下拉配置进行CPOL赋值。

关于CPHA的选择,我个人更倾向于使用CPHA配置为1的状态。此配置下,第一个时钟沿驱动数据数据输出,第二个时钟沿驱动数据采样,比较符合硬件上的使用习惯。

当然了,这都是纸上谈兵,很多时候时序类型的选择还要结合芯片硬件条件、功能实现需求等问题考虑。

注释1:维基百科上SPI接口的详细描述http://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus