---恢复内容开始---

以下内容整理自Transient-Steady Effect Attack on Block Ciphers 2015

这篇文章提出了一种新的攻击:暂稳态效应攻击

暂稳态效应:组合电路的输出在跳转为正确的值之前会保持一个暂时的值

优点:和其他故障攻击相比,不需要大量的加密去建立统计模型,即攻击阶段需要的加密次数更少

攻击实现:注入时钟毛刺,得到暂稳态值,也就是包含秘钥信息的故障输出

目标电路:两种不屏蔽s盒和一种屏蔽s盒的AES电路,FPGA实现

实验结果:对于未屏蔽的S盒 加密一次可以获得秘钥的一个字节

对于屏蔽了的s盒 加密20次可以获得秘钥的一个字节

1.背景介绍

侧信道攻击的提出1

现在已经有很多侧信道攻击密码电路的方法(泄露信息型):

功耗分析 2、3

template 4

碰撞 5、6

mutual information 7

故障攻击,DFA是其中比较有名的 8,基于故障模型从正确的密文输出和错误的密文输出中恢复秘钥

2010年提出故障灵敏度分析FSA 9,这种方法基于AES的s盒的关键路径具有数据依赖性,但是破解需要多次加密

2011年FSA与碰撞攻击结合,攻破了有屏蔽的AES电路 10,缺点是增加了加密次数

2012年提出顺时针碰撞故障灵敏度分析CC-FSA,针对屏蔽AES电路

他们指出,如果两轮输入完全相同,第二次的时间会更短,因为在组合电路中几乎没有了翻转

2012年紧接着提出时钟宽度攻击FRA,攻破了串行屏蔽AES的s盒

但是以上两种方法有共同的缺点:

1.混乱的时钟频率

2.检测合适的时钟宽度很低效

3.加密次数太多

这篇文章的贡献

提出一种新的故障攻击方法:暂稳态攻击TSE attack

目标电路通常在第一个周期内进行计算,并注入一个时钟毛刺以创建一个非常短的第二个周期。根据第一周期中的短路径数据和长路径数据计算出第一时钟周期的正常输出。根据第二个周期的短路径数据和第一个周期的长路径数据计算第二个周期的错误输出。通过组合两个连续时钟周期的输出,我们可以恢复短路径数据的信息

(秘钥所在的路径比较短)

2.准备工作

AES10轮加密,每轮需要16个s盒。当功耗、面积被限制时,算法的串行实现更棒。

举个例子:

在每一轮加密中,用4个s盒循环4次 13-14

很多低功耗的实现方法被提出 15-16

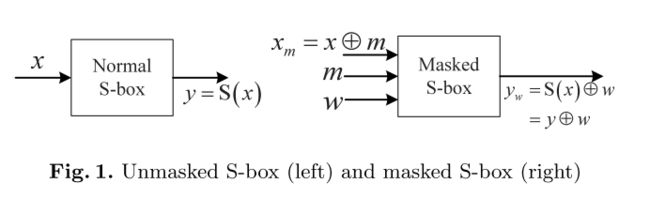

屏蔽是针对功耗分析的常规对策。 掩码值使敏感的中间值随机化,并使数据和功耗之间的依赖性最小。 S-box是AES算法中唯一的非线性运算,作为基于塔场的方法,已经提出了许多掩蔽方案[17]。

屏蔽和未屏蔽的s盒:

Li等人提出了CC-FSA攻击。 在2012年[11]。 如果输入在连续的两个时钟周期没改变,第二个周期几乎没有信号翻转。 这称为顺时针碰撞,第二个时钟周期的建立时间将非常短。 他们让目标在第一个周期中正常工作,并插入一个时钟毛刺去产生非常短的第二个时钟周期。 如果输出正确,顺时针碰撞将会被检测到。

3.暂稳态效应攻击

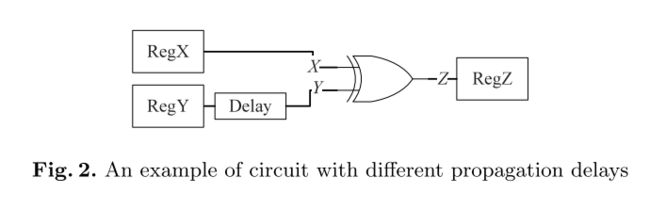

组合电路中数据路径的长度不一样

例如,我们可以假设信号a的路径延迟短于信号b的路径延迟。 在a到达之后,b到达输出之前,输出会呈现一个非法值。 当两个信号之间传播延迟的差异足够长时,输出将保持在非法值。 这称为瞬态稳定效应。 暂态稳定效应可能导致数据相关的功耗,并间接泄露秘密信息[18-22]。 但是,在本文中,我们显示了由瞬态稳定效应引起的暂存值可以被捕获并可以用于直接恢复秘钥。

基于暂稳态效应,提出了暂稳态效应攻击:

目标电路通常在第一个周期内进行计算,并注入一个时钟毛刺以创建一个非常短的第二个周期。根据第一周期中的短路径数据和长路径数据计算出第一时钟周期的正常输出。根据第二个周期的短路径数据和第一个周期的长路径数据计算第二个周期的错误输出。通过组合两个连续时钟周期的输出,我们可以恢复短路径数据的信息。

(秘钥所在的路径比较短)

基本思路

X、Y信号的延迟分别为tX、tY,输出Z的值会被寄存器捕获

假设tX $/<<$ tY,第一个时钟周期的输入是X1,Y1,第二个时钟周期的输入是X2,Y2。

第二个时钟上升沿之后,X2,Y2沿着不同的路径传播,像涟漪以不同的速度扩散一样

在一段时间t(tX/>t/>Y)之后,X2到达异或门的输入,但是Y还没有到达2

所以在t段时间内,Z的输出是f(X2,Y1)

我们假设d=tY-tX足够大,并因此,f(X2,Y1)会在输出保持一段时间的稳定

如果注入的时钟毛刺周期小于等于d,这个暂稳态值就能被存到regZ中(注意,如果毛刺周期大于d,regZ就会捕捉到一下周期的正确值,暂稳态值就不会被捕获)

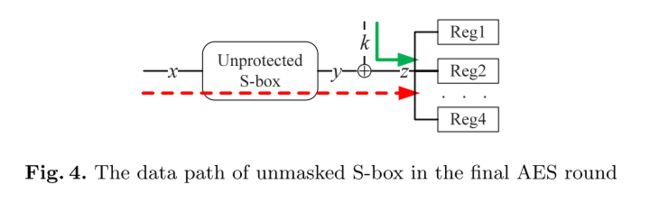

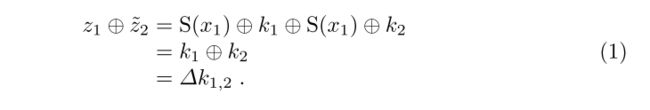

unmasked S盒攻击设想

串行实现的s盒,假设在执行最后一轮AES加密,红色路径长,绿色路径短

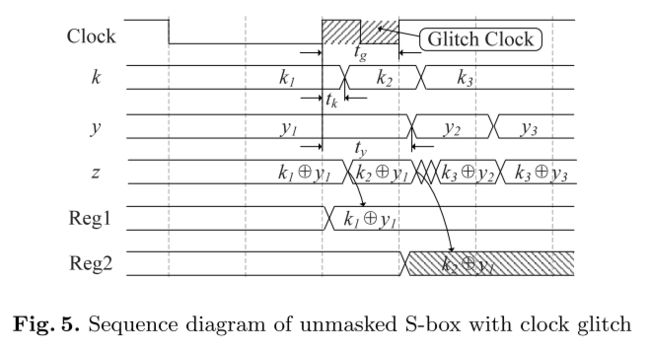

如图五所示,在第二个时钟上升沿,第一个时钟周期的输出![]()

寄存在reg1

k的保持时间过了之后,k2传播通过异或门,输出变为![]()

这个暂存的值会在ty-tx这段时间内稳定。

总结一下就是:如果我们在第一个时钟周期后注入一个时钟毛刺构成第二周期,保证这个周期tg满足![]()

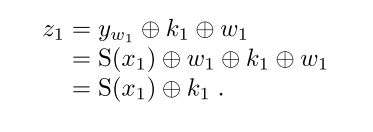

,reg2就可以捕获到![]() ,知道了z1和

,知道了z1和![]() ,我们可以计算:

,我们可以计算:

因为这些路径的延迟我们不知道,所以要进行TSE攻击,攻击步骤如下:

1.扫描时钟毛刺频率,逐渐改变时钟毛刺周期的长度,在每一个频率下,用固定的x1和随机的x2进行Npre次的加密,并记录错误输出

2.找出能使得故障输出稳定的毛刺频率范围,根据上面的分析,x1固定的条件下,根据公式![]() ,错误的输出应该和x2无关

,错误的输出应该和x2无关

3.选定毛刺的频率

4.在选定的毛刺频率下,加密Nattack次,记录![]() ,计算每次加密的攻击结果

,计算每次加密的攻击结果![]()

5.选择故障输出中频率最高的结果

6在其他时钟周期.重复4、5步骤,用来恢复 等

等

步骤1-3称为预计算阶段,对于一个目标电路来说只需要进行一次。

步骤4-6称为攻击阶段,可以在一个固定的频率下进行。

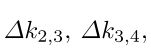

masked s盒攻击设想

masked s盒有三个输入:

the masked value:![]()

the input masked :m

the output masked:w

输出用w屏蔽:![]()

因为w是用来屏蔽s盒的输出的,所以它的路径要比xm和m都要短

我们关注基于“塔场”的masked s盒

正如图6所示,红的比绿的都长:

在第一个时钟周期,reg1会捕获到正常的输出:

yw1代表第一个时钟周期 屏蔽s盒 的输出

我们在第一个时钟周期之后注入一个时钟毛刺。如果毛刺周期的长度比xm和m的延时短,比w和k长,暂稳态的输出就可以被reg2捕捉到:

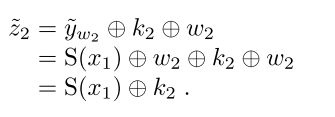

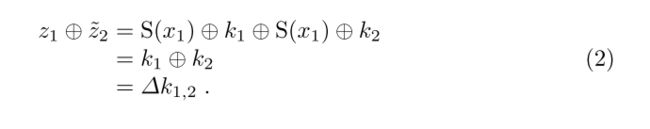

根据正常的输出和故障输出,可以得到:

注意:攻击只适用于,如果在同一时钟周期内有密钥加入且没有屏蔽

(此处原文:Note that the attack described in this section is only applicable if the final unmasking is done within the same clock cycle as the final key addition.)

4.实验和有效性

我们在两种未屏蔽s盒上15 16,和一种屏蔽s盒17 上验证TSE攻击

开发板型号:

DE2-115 FPGA board with Altera Cyclone IV EP4CE115

时钟函数:RIGOL DG4102 function

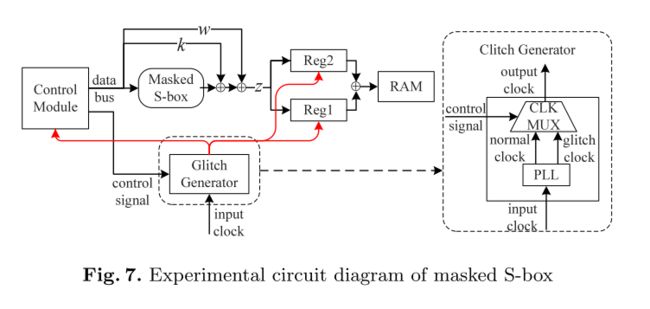

电路框图如图7所示:

锁相环PLL产生两个时钟信号,低频--正常时钟,高频--产生毛刺,由多路选择器来选择时钟信号

两个连续的时钟周期的输出![]() ,分别寄存在reg1和reg2

,分别寄存在reg1和reg2

攻击结果![]() 存在RAM中

存在RAM中

像第3节提到的,如果没有故障注入,输出将是

如果攻击成功结果就是![]()

在未屏蔽s盒A上的实验

s盒 文献15

设定密钥字节![]()

如果攻击成功,RAM里面的就是![]()

预计算阶段:

在64MHz到480MHz选择80个点

在每一个频率点,x1是固定值0x31,x2变化

对于每一个x2