关注 | 摩尔定律到底还能走多远?

![]()

文章经授权转载自半导体行业观察(ID:icbank)

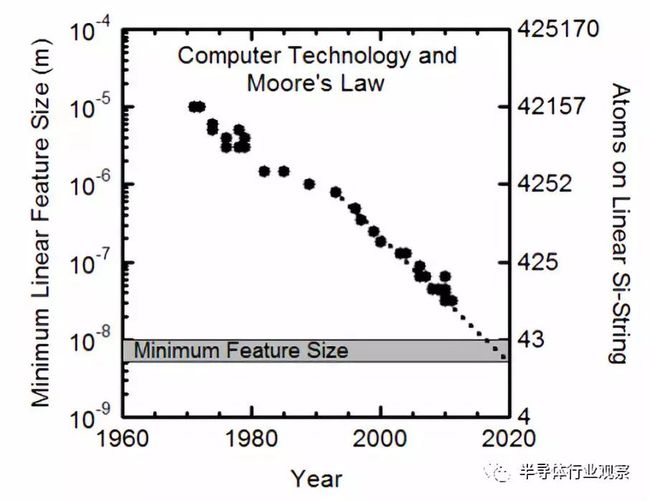

近日,三星公布了其半导体工艺路线图,除了今年下半年使用EUV的7nm量产之外,接下来还将有5nm和4nm FinFET,而到了2020年则会开始3nm基于Gate All-Around (GAA)晶体管的最新工艺。除此之外,ASML则确认了其光刻机使用EUV加上大数字孔径可以实现1.5nm的特征尺寸从而可望支持摩尔定律发展到2030年。近些年来,“摩尔定律接近尾声”的声音不绝于耳,而这些消息却像是给摩尔定律打了一剂强心针,至少在技术上我们还能继续把特征尺寸缩小这件事继续做几年。

从平面工艺到GAA

摩尔定律的辉煌始于上世纪下半叶,平面CMOS器件工艺诞生后特征尺寸就在不停地缩小,按照摩尔定律的描述是集成度每18个月翻一番。一方面,缩小特征尺寸可以增加集成度,或者说降低单个晶体管的成本,这就从经济角度推进了特征尺寸缩小;另一方面,在平面CMOS工艺中,缩小特征尺寸可以增加晶体管开关速度,也就是说特征尺寸缩小也增强了晶体管的性能,而更强的性能给芯片开拓了新的市场应用,也给半导体行业资本注入带来了巨大的想象空间。从上世纪九十年代的多媒体PC,本世纪初的互联网PC,到2010年代的智能移动设备风行,这些新应用市场的打开无一不依靠处理器芯片的快速性能提升。因此,从经济和性能两个方面一推一拉成了摩尔定律的强大动力。虽然在晶体管特征尺寸缩小的过程中遇到了一些小小的困难,但是通过将铝互联改成铜互联,在栅极加入High-k材料、引入stress engineering等方法都可以在不改动平面器件工艺的情况下把特征尺寸继续做小。

然而平面器件到了28nm节点之后遇到了很大问题。主要问题是栅极对于沟道的控制能力(尤其是亚阈值区的漏电流)随着栅长(gate length)减小而快速减小,漏电流成了一个很大的问题。

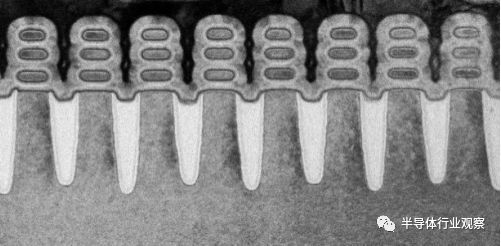

在这时候,由UC Berkeley胡正明教授开发的FinFET就应运而生。在FinFET中,沟道不再是二维的而是三维的“鳍”(Fin)形状,而栅极则是三维围绕着Fin,这样就大大增加了栅极对于沟道的控制能力,从而解决了漏电流的问题。FinFET在2001年由胡正明教授在学术界正式提出,而在2013年秋天TSMC正式在16nm工艺中使用FinFET。从16/14nm开始,FinFET成为了半导体器件的主流选择。

在器件问题解决之后,另一个问题是制造工艺,主要的瓶颈是光刻精度如何满足几纳米特征尺寸的要求?根据光学,数字孔径越大,光刻波长越小,则光刻精度越好。因此在学术界如何提升光刻精度是很清楚的,即使用波长较短的光(如紫外线EUV等)以及增大数字孔径使用浸没式光刻等。然而,在业界,使用EUV一直是一个痛苦的选择:大家知道早晚得用,但是出于成本和工艺成熟度考量大家总是希望越晚用EUV越好,能不用EUV就先撑几代再说。因此就出现了double-pattern(用在16nm)甚至multi-pattern等办法实现在不使用EUV的情况下也能做到超低特征尺寸下的光刻,代价是工艺的复杂性大大上升。到了7nm终于是撑不住了,巨头纷纷开始宣布使用EUV。当然之前的multi-pattern也不算是走了弯路,因为即使是用了EUV,在未来更小的特征尺寸下估计还是要上multi-pattern。与此同时,ASML在近日也公布了其路线图,并指出其1.5nm光刻技术将足够支持摩尔定律到2030年。

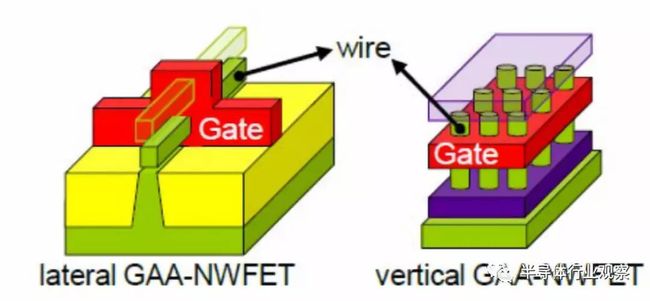

在工艺问题解决后特征尺寸继续缩小,但是到了5nm左右连FinFET也不太够用了,这时候就出现了Gate All-Around (GAA)器件。在平面器件中,沟道有一面面对栅极;在FinFET,立体沟道三面都被栅极围绕;到了GAA,沟道由纳米线(nanowire)构成,而纳米线的四面都被栅极围绕,从而再度增强栅极对于沟道的控制能力。

三星本次公布的GAA称为多桥沟道FET(multi-bridge-channel FET, MBCFET),事实上从2008年久开始研发了。在2017年的VLSI technology symposium(半导体工艺领域最好的会议之一)上,IBM就发表了与GlobalFoundries和Samsung合作研发的5nm GAA晶体管,所以今年三星公布3nm GAA其实在意料之中。不过有一些出乎意料的是三星宣布量产3nm GAA的时间点(2020年),因为之前业界专家普遍预测3nm GAA预计要到2022年才能真正量产,而三星在2020年计划量产3nm GAA的计划实属激进方案,可见半导体巨头对于下一代工艺路线图的争夺非常激烈。

2017年IBM公布的与GlobalFoundries和Samsung合作研发的5nm GAA晶体管

随着摩尔定律接近物理瓶颈,特征尺寸缩小和性能上升越来越难

如之前所述,随着特征尺寸的不断缩小,栅极对于沟道的控制能力减弱,因此必须引入新的器件结构以满足晶体管的要求。从时间上可以看到这种明显的趋势:平面工艺晶体管的特征尺寸缩小过程持续了数十年,之后到了2013年下半年16/14nm节点正式引入FinFET,然而FinFET仅仅维持了10年不到,2020年左右的3~5nm节点就必须转入GAA。

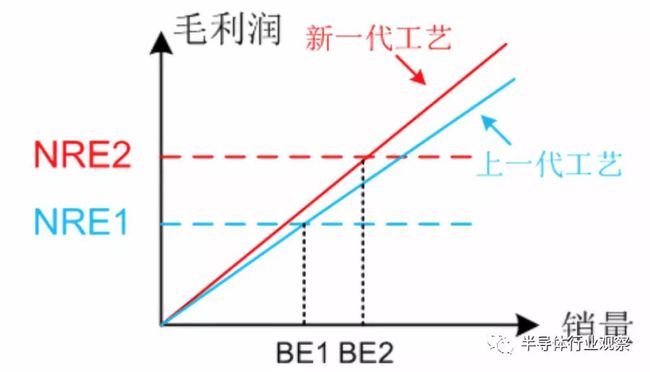

而GAA又能维持多久呢?可能没有过几年我们又必须去找下一代其他器件技术才能继续缩小特征尺寸。而使用新器件就意味着半导体工艺必须有较大的更新,带来的结果就是芯片设计的NRE成本大大上升。根据估计,在7nm等先进节点,一款芯片的设计和流片一次性NRE成本高达数亿美元,这就意味着只有大公司才能玩得起。另外随着NRE成本快速提升,也意味着芯片的出货量只有足够大才能把一次性成本平均掉达到盈亏平衡(break even,BE)点。这就使得只有手机芯片之类出货量巨大,对平均成本非常敏感而又希望芯片性能能定期升级的品类才会使用最新工艺。

而且,除了一次性成本在快速上升之外,晶体管的集成度在随着特征尺寸缩小的同时上升速度也在减缓。这是因为之前的特征尺寸缩小比较“实诚”,最小栅长、最小金属线宽都在同步以相同比例缩小,而在16nm以下的时候特征尺寸缩小往往只是指栅长缩小,最小金属线宽缩小的倍数并没有这么大。这就导致了实现相同功能的芯片随着特征尺寸缩小其芯片面积缩小倍数没那么大了。

根据高通的分析,10nm节点的单位晶体管面积相对上一代节点缩小了37%,而到了7nm节点相对10nm节点单位晶体管面积缩小变成了20%~30%。这就意味着在最新的工艺节点,即使不考虑一次性成本,平均成本的下降也变小了。须知摩尔定律的主要动力就是成本下降,而在一次性成本快速提升但平均成本却下降有限的时代,摩尔定律的进一步发展动力就不那么强了。

除此之外,随着摩尔定律特征尺寸缩小,半导体电路的性能提升速度却在减缓。在摩尔定律发展的黄金时代,随着特征尺寸缩小器件,器件可以运行在更高频率;另一方面器件阈值电压也同步下降,因此每代工艺之间的电源电压也在下降。按照电路动态功耗的计算公式,CMOS数字电路的动态功耗和电源电压的平方成正比,和时钟频率也成正比,因此在同时降低电源电压和提高时钟频率的时候,虽然电路性能呈指数级提升,其功耗却不会上升,这也称为Dennard Scaling。

然而,Dennard Scaling在特征尺寸进入深亚微米(90nm)后开始失效,因为漏电流变得越来越严重,因此阈值电压无法随着特征尺寸下降而同步下降,这一方面导致器件的性能随着特征尺寸缩小的增长速度在变慢,另一方面意味着电源电压没法快速下降因此功耗指标随着特征尺寸缩小的收益也变小。

举例来说,当年摩尔定律的黄金年代0.18um工艺的额定电压是1.8V,当特征尺寸缩小到0.13um时额定电压也缩小到了1.2V,其特征尺寸和额定电压都以接近相同的比例(0.7倍)在缩小。到了28nm工艺时其额定电压是0.9V,而在特征尺寸缩小接近一半的16nm FinFET其额定电压为0.7V,特征尺寸缩小了接近一半但是额定电压的减小却没有那么显著。

到了10nm以下的节点,晶体管性能提升更是缓慢。虽然单个晶体管的速度还是随着特征尺寸缩小而提升的,但是芯片上的金属互联却在渐渐成为瓶颈。如之前的讨论,随着特征尺寸缩小我们同时也希望金属最小线宽也能同步缩小以增加集成度降低成本,然而随着金属线宽缩小它的阻抗却在上升,这就导致了金属线带来的RC延迟成为了芯片性能的瓶颈。结果就是在10nm以后的节点芯片性能随着特征尺寸缩小提升非常有限。

根据高通的分析,10nm节点的芯片速度比上一代节点能提升16%,而到了7nm芯片速度相比10nm几乎不会有提升——你看到的7nm芯片比起上一代10nm芯片的性能提高几乎完全来自于芯片架构和电路设计而非特征尺寸缩小。此外,功耗的减小也变慢,10nm节点比起上一代半导体节点功耗可以减小30%,到了7nm节点相比10nm节点的功耗降低久只有10-25%了。

除了GAA的其他技术

虽然摩尔定律在接近物理极限的今天继续缩小特征尺寸的代价越来越大收益越来越小,但是半导体工艺和器件的更新却还是要继续,因为这类更新是半导体行业前进的源动力之一。然而,我们会看到一条与原来摩尔定律不尽相同的半导体演进路线:特征尺寸的缩小的重要性可能略有减弱,而新半导体器件的专用性会加强,即未来可能会针对不同的应用开发更多专门的半导体晶体管器件,而不是用一种CMOS包打天下,从而实现功耗、性能等指标的改善。这种使用新半导体器件针对专用应用实现的性能提升可以看作是摩尔定律的最新延续。

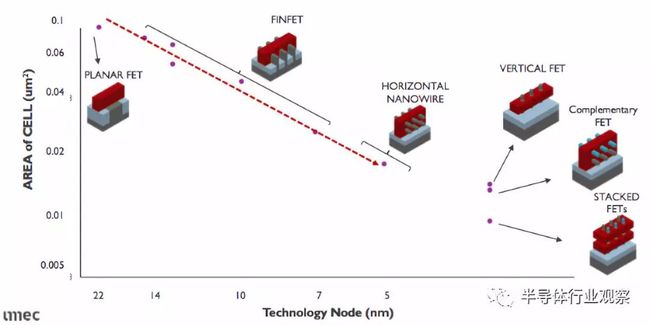

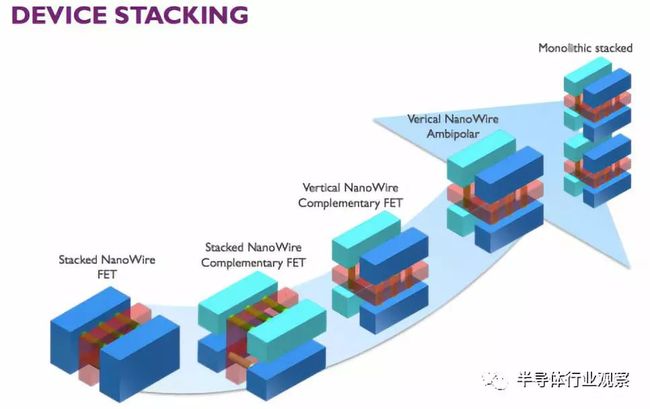

上图是欧洲顶级半导体研究机构IMEC的半导体器件随着特征尺寸变化的路线图。可以看到在FinFET到5nm左右之后,横向纳米线(Horitontal Nanowire),即之前讨论的的三星GAA将在5nm~3nm节点得到使用。之后的技术路线中,IMEC建议使用垂直生长技术,例如垂直纳米线GAA Vertical FET。与横向GAA不同,垂直GAA的纳米线的方向是垂直于芯片的,因此可以实现更进一步的特征尺寸缩小。

近日,IMEC刚刚联合Unisantis发表了使用垂直GAA工艺的SRAM单元,相比于今年二月三星发布的7nm工艺节点SRAM单元(0.026mm2),使用垂直GAA的SRAM可以把尺寸进一步缩小20%至0.0205mm2。同时,IMEC表示垂直GAA是一种特别适合SRAM的器件,而在未来的芯片中IMEC预期会使用不同的半导体器件实现不同的模组,例如横向GAA实现逻辑单元,使用垂直GAA实现SRAM等。

横向和垂直GAA比较

除了垂直GAA之外,IMEC路线图上还包括了互补FET(complementary FET, CFET)。互补FET的原理是,使用一根纳米线作为n型FET,而使用与其相邻的另一个纳米线作为p型FET,即nFET和pFET在垂直于芯片的方向做堆叠,从而实现更高的面积利用效率。

IMEC器件进化路线图

由IMEC的路线图可以看出,研究人员正在逐渐把二维的半导体器件三维化,向垂直方向堆叠器件以实现更高的面积利用效率。除了半导体器件之外,封装技术也在向2.5D和3D堆叠方向演进。这种向垂直维度演进的势头,也可以看作是摩尔定律未来的发展方向。

结语

三星等巨头使用新器件以延续特征尺寸继续缩小可以看作是摩尔定律的下一步。然而,随着逼近物理极限,我们看到特征尺寸缩小对芯片带来的经济和性能提升都越来越有限。未来我们可望看到半导体行业往专业细分化方向发展。与过去一种器件工艺一种芯片平台覆盖绝大多数应用不同,专业细分化的半导体行业将会针对不同的应用开发针对性的专用器件(例如垂直GAA之于SRAM)、封装(例如3DIC之于高端FPGA)和芯片,从而实现芯片性能、成本的进一步演进。这可以看作是摩尔定律的延续,而在这样的延续过程中芯片设计人员将变得更为重要。

END

以上文章为转载,不代表本报观点