s3c2440时钟学习(韦东山老师课程学习笔记)

S3C2440时钟体系(韦东山学习笔记)

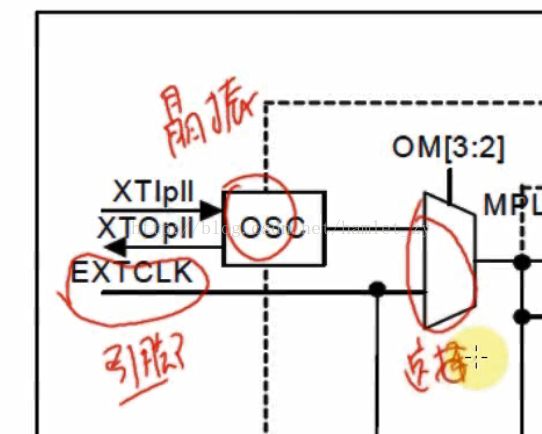

1、 S3C2440可以外接晶振,然后通过内部电路产生时钟源 ; 也可以直接使用外部提供的时钟源,它通过引脚的设置来选择。

如果2440时钟源选择的是12M晶振,如何得到400M的FCLK,136M的HCLK,68M的PLK?通过PLL,这就是PLL的作用,分频。

那么如何选择是用晶振产生时钟源,还是外部提供的时钟源呢?通过OM[3:2]引脚来选择。(配置手册7-1图)

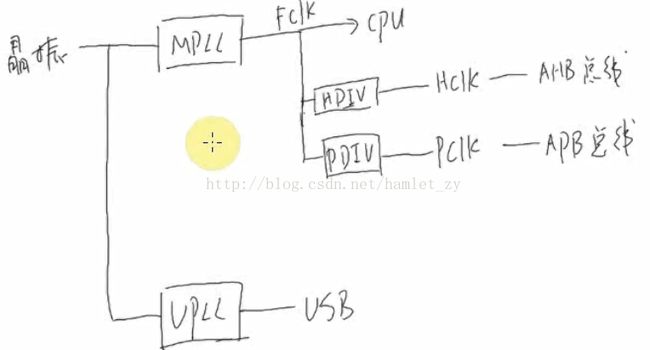

2、三种时钟:FCLK用于cpu核、HCLK用于AHB总线上的设备、PCLK用于APB总线上的设备。

其中AHB(Advanced High Performance Bus)总线:用于接高性能模块,例如CPU、DMA。

APB(Advanced Peripheral Bus)总线:用于接低带宽的周边外设,例如I2C、UART。

3、S3C2440有两个PLL,分别是MPLL(mainPLL)、UPLL(usbPLL):

(1)MPLL用于设置FCLK 、HCLK 、PCLK

(2)UPLL专门用于USB设备。

4、The S3C2440A has two Phase Locked Loops(PLLs) 锁相环: one for FCLK, HCLK, and PCLK, and the other dedicated for USB block (48Mhz).

PLL锁相环 ,将12M晶振,分频给 fclock hclock 和 pclock 分别为 400m 136m 68m

5、OM[3:2]是一个选择器,选择使用晶振作为时钟源,或者是外部时钟作为时钟源。 具体看Table7-1图。

晶振产生的时钟源通过MPLL分频后,得到FCLK送给CPU,FLCK通过HDIV分频后得到HCLK送给AHB总线上的设备,同理,FCLK通过PDIV分频送给APB总线上的设备。

通过设置HDIVN寄存器和PDIVN来得到HCLK和PCLK。

6、

具体过程:

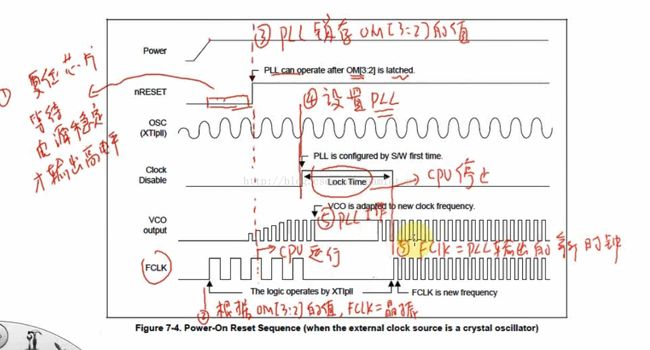

开发板上电后,FCLK = 晶振的12M(前提是设置成晶振为时钟源), nRESET等待电源稳定,才输出高电平,这时,PLL会锁存OM引脚的值,然后就可以设置Lock Time的值了,在LockTime时间内,FCLK停止工作,cpu也停止工作,等过了这段时间,FCLK会等于PLL输出的新的时钟频率。

PLL的工作时间为LockTime开始到LockTime结束,这段LockTime时间内,就是PLL分频的过程,LockTime结束后(PLL也结束),FCLK会等于新的时钟频率。

7、

FCLK=400m、HCLK=100m、PCLK=50m

设置MPLLCON寄存器 :让FCLK=400 ,

设置CLKDIVN寄存器 -----> HDIVN=FCLK/4 :让HCLK=100,

设置CLKDIVN寄存器 -----> PDIVN=FCLK/8 :让PCLK=50,

8、步骤:

1、设置CLKDIVN寄存器,使 FCLK=4HCLK=8PCLK

(CLKDIVN 地址0x4C000014 值应为 0b101 = 0x5 ---》 400 100 50)

2、设置,使 FCLK=400M

(PLL CONTROL REGISTER 256页: 92<<12 | 1<<4 | 1<<0)

12.0000MHz 400.00 MHz -》》》》MDIV: 92(0x5c)

PDIV: 1

SDIV:1

注意:

1. CLKDIVN should be set carefully not to exceed the limit of HCLK and PCLK.

2. If HDIVN is not 0, the CPU bus mode has to be changed from the fast bus mode to the asynchronous

bus mode using following instructions(S3C2440 does not support synchronous bus mode).

MMU_SetAsyncBusMode

mrc p15,0,r0,c1,c0,0