【原创】【SPI】SPI通信协议介绍

1、这是个什么玩意

接上篇接着介绍,协议主要就是保证双方能够正常的通信并理解对方的“话”。而本篇介绍的这个SPI协议是为了保证SPI接口的两头双方能够正常通信。具体的说,就是针对那几根物理线如何操作,物理线无非就是涉及高低电平,两条(及两条以上的)线之间需要配合的时序,具体看下面。

2、有毛用啊

不多说了,如上。

3、怎么用啊

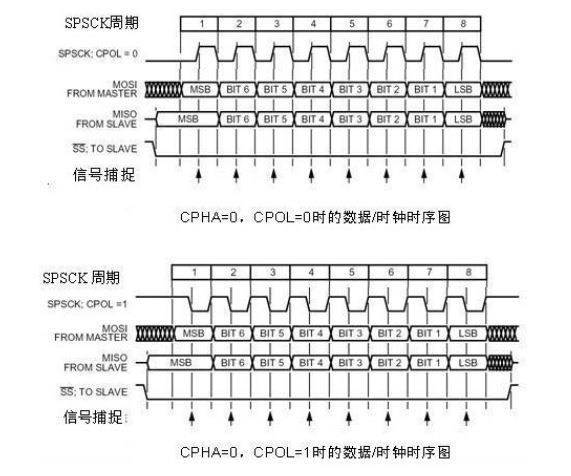

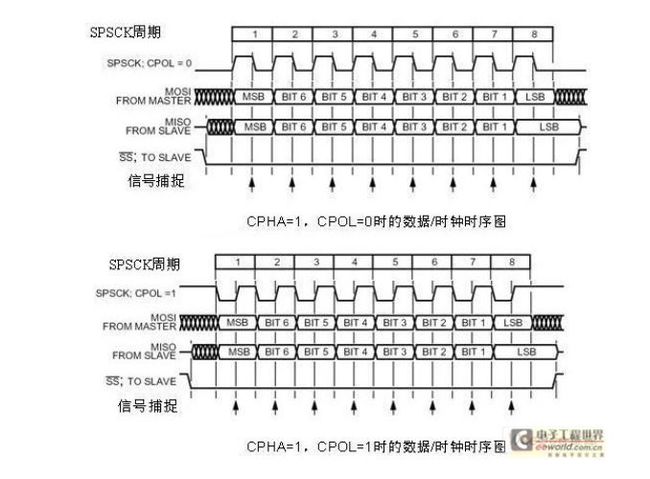

SPI有四种工作模式,取决于两个参数:(这两个参数其实就是控制了CLK这一根线,SPI通信不像UART或IIC那样有专门的通信周期,有专门的通信起始信号和结束信号。所以SPI协议能够通过控制时钟信号线在没有数据交流的时候保持的状态,要么是高电平,要么是低电平)

SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。

SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

该图参考http://blog.csdn.net/guomutian911/article/details/72813067,在此感谢。

之前说过,由于SPI没有一个统一的规范,所以在时序上描述存在一定的差异,具体以datasheet为准。

还有就是这四种模式的优缺点目前我还未知,请大牛详解。

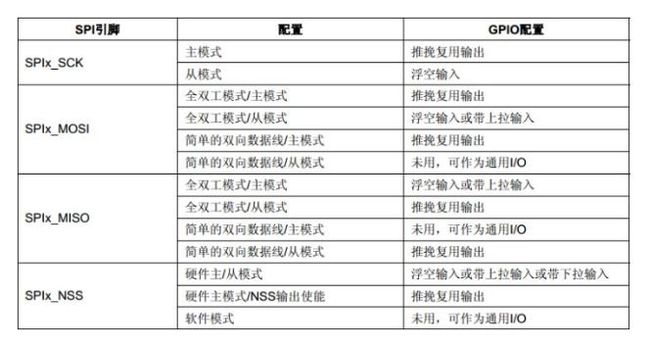

STM32系列芯片的很多SPI接口都是和GPIO共用,SPI的初始化分为2大块,就是SPI所使用的I/O口的初始化和SPI功能的初始化。对于SPI同步串口要用到的引脚,根据数据的方向,要设置GPIO_Mode_IN_FLOATING或者GPIO_Mode_AF_PP复用推免输出。其他的和GPIO引脚设置一样。

1.管脚因为复用的,故先配置好管脚、并打开spi时钟。下图参考于https://zhuanlan.zhihu.com/p/27489167,在此感谢,该篇写的也非常好,可以继续学习下。

2.设置spi的工作模式通过 SPI1_CR1 来设置,设置SPI1主机模式,设置数据格式8位,然后通过 CPOL 和 CPHA 位来设置 SCK时钟极性及采样方式。并设置 SPI1 的时钟频率(最大18Mhz),以及数据的格式(MSB 在前还是 LSB在前)。

3.使能SPI.

具体SPI主要配置项如下:

SPI_Direction:SPI通讯方向,可配置双线全双工、双线只接收、单线只接收、单线只发送模式;SPI_Mode:SPI的工作模式,即工作在主机模式或从机模式。若工作在从机模式,则SCK信号由外部提供;

SPI_DataSize:通讯的数据帧大小,可选8位或16位;

SPI_CPOL:时钟极性,配置空闲状态时的SCK电平;

SPI_CPHA:时钟相位,配置数据采样时刻,可配置在每个时钟周期的第1个或第2个边沿进行采样;

SPI_NSS:配置NSS引脚的使用模式,可配置为硬件模式或软件模式。软件模式即是普通的GPIO口,人工拉高或置低其电平;

SPI_BaudRatePrescaler:波特率分频因子,分频后的时钟即为SPI的SCK信号线的时钟频率;

SPI_FirstBit:串行通讯中总会牵扯到MSB(高位)先行还是LSB(低位)先行的问题,可以用这个结构体成员进行配置;

SPI_CRCPolynomial:CRC校验,若使用CRC,则可计算CRC的值。

四,成为大神的用法

多调试,多解决问题,推荐博客http://blog.csdn.net/guomutian911/article/details/72813067,该博客记录了一些SPI的问题,在此推荐给大家。通常比较常见的问题是CLK的频率太快,导致接收数据不对或不完整。主器件时钟CLK主、从器件时钟CLK从和同步串行时钟SCK,其中SCK是对CLK主的分频,CLK从和CLK主是异步的。要使SCK无差错无遗漏地被从器件所检测到,从器件的时钟CLK从必须要足够快。