1. 基于RISC-V架构的开源处理器及SoC研究综述

https://mp.weixin.qq.com/s/qSD-q8y0_MY8R0MBA85ZZg

原文链接:

https://blog.csdn.net/leishangwen/article/details/55006662

https://blog.csdn.net/leishangwen/article/details/55006804

https://blog.csdn.net/leishangwen/article/details/55006855

在RISC-V发布之前,实际上已经有几种开源指令级架构,包括SPARC V8、OpenRISC,其中SUN发布的开源多核多线程处理器OpenSparcT1、OpenSparcT2,以及欧空局的LEON3采用的就是SPARC V8,OpenRISC也有同名的开源处理器

32位架构由RV32表示,其每个通用寄存器的宽度为32比特;64位架构由RV64表示,其每个通用寄存器的宽度为64比特

RV32G表示RV32IMAFD,

RV64G表示RV64IMAFD,

C压缩指令的指令编码长度为16比特,而普通的非压缩指令的长度为32比特

E 嵌入式, 仅需要支持16个通用整数寄存器

D 必须支持F

整数寄存器0被预留为常数0,其他的31个(I架构)或者15个(E架构)为普通的通用整数寄存器

D/F 浮点模块,则需要另外一个独立的浮点寄存器组,包含32个通用浮点寄存器。如果仅使用F模块的浮点指令子集,则每个通用浮点寄存器的宽度为32比特;如果使用了D模块的浮点指令子集,则每个通用浮点寄存器的宽度为64比特

开源CPU- RISC-V 架构

标量处理器——Rocket

Rocket是采用Chisel(Constructing Hardware in an Scala Embedded Language)编写的

UCB设计的一款64位、5级流水线、单发射顺序执行处理器,主要特点有:

支持MMU,支持分页虚拟内存,所以可以移植Linux操作系统

具有兼容IEEE 754-2008标准的FPU

具有分支预测功能,具有BTB(Branch Prediction Buff)、BHT(Branch History Table)、RAS(Return Address Stack)

超标量乱序执行处理器——BOOM

BOOM(Berkeley Out-of-Order Machine)是UCB设计的一款64位超标量、乱序执行处理器,支持RV64G,也是采用Chisel编写,利用Chisel的优势,只使用了9000行代码,流水线可以划分为六个阶段:取指、译码/重命名/指令分配、发射/读寄存器、执行、访存、回写。

借助于Chisel,BOOM是可参数化配置的超标量处理器,可配置的参数包括:

取指、译码、提交、指令发射的宽度

重排序缓存ROB(Re-Order Buffer)、物理寄存器的大小

取指令缓存、RAS、BTB、加载、存储队列的深度

有序发射还是无序发射

L1 cache的路数

MSHRs(Miss Status Handling Registers)的大小

是否使能L2 Cache

处理器家族——SHAKTI

SHAKTI[4]是印度理工学院的一个计划,目标是设计一系列适合不同应用环境的、基于RISC-V的开源处理器,以及一些IP核,以便搭建SoC。这些处理器是E-Class、C-Class、I-Class、M-Class、S-Class、H-Class、T-Class、N-Class,目前已经开源的是前三个,使用Bluespec System Verilog编写

嵌入式应用处理器——ORCA

PicoRV32是由VectorBlox公司设计的一款32位标量处理器,目标是应用于嵌入式领域,采用VHDL编写,实现了RV32IM,也可以移除其中的M扩展,也就是移除乘法除法扩展,从而减少芯片占用资源,甚至可以移除与定时器有关的指令,从而仅仅实现RV32E

其他开源处理器

(1)RI5CY

RI5CY是由苏黎世联邦理工大学和波罗尼亚大学联合设计的一款小巧的4级流水线开源处理器,实现了RV32IC,以及RV32M中乘法指令mul,其目标是作为并行超低功耗处理器项目PULP(Parallel Ultra Low Power)的处理器核,所以RI5CY在RISC-V的基础上增加了许多扩展,包括硬件循环、乘累加、高级算术指令等。采用UMC的65nm工艺进行流片,RI5CY主频可以达到654MHz,动态功耗是17.5uW/MHz[6]。采用SystemVerilog编写。

(2)RIDECORE

RIDECORE (RIsc-v Dynamic Execution CORE) 是由东京工业大学设计发布的一款超标量乱序执行处理器,实现了RV32IM,6级流水线,分别是取指、译码、指令分配、发射、执行、提交,可以同时取两条指令、对两条指令译码、提交两条指令。采用的是Gshare分支预测机制。

(3)Hwacha

Hwacha是由UCB开发的一款向量处理器,UCB将Hwacha作为RISC-V的一个非标准扩展Xhwacha,已经以28nm和45nm的工艺流片多次,主频在1.5GHz以上,目前还在研发中,正在修改OpenCL的编译器,以适合Hwacha,UCB计划以开源的形式发布其代码。

(4)f32c

f32c是由萨格勒布大学设计发布的32位、5级流水线、标量处理器,原本实现的是MIPS指令集,后来添加实现了RISC-V指令集,处理器包括分支预测、直接映射缓存,同时发布的还有SDRAM控制器、SRAM控制器、视频FrameBuffer、SPI控制器、UART、GPIO等IP,使用VHDL编写代码。使用f32c处理器核,萨格勒布大学发布了FPGArduino项目,该项目将一块FPGA开发板变为一个Arduino板,并且可以使用Arduino IDE进行程序编译下载。

(5)Z-scale/V-scale

Z-scale是UCB发布的针对嵌入式环境的32位、3级流水线、单发射标量处理器,实现了RV32IM,指令总线和数据总线都是AHB-Lite。Z-scale采用是Chisel编写代码,利用Rocket中的代码,仅增加了604行代码就实现了Z-scale。V-scale是Z-scale对应的Verilog版本。

(6)sodor

sodor是UCB发布的针对教学的32位开源处理器系列,采用Chisel编码实现,可以很容易的得到对应的C++模拟器。sodor系列有五种处理器,分别是单周期处理器、2级流水线处理器、3级流水线处理器、5级流水线处理器、可执行微码的处理器。

(7)PicoRV32

PicoRV32是由RISC-V开发者Clifford Wolf设计发布的一款大小经过优化的开源处理器,实现了RV32IMC,并且根据不同环境可配置为实现RV32E、RV32I、RV32IC、RV32IM、RV32IMC。内置一个可选择的中断控制器。其特点是小巧,在Xilinx7系列芯片上占用750-2000个LUT,速度可以达到250-400MHz。PicoRV32采用Verilog编写代码。

(8)Tom Thumb

Tom Thumb是由RISC-V开发者maikmerten设计发布的一款32位、6级流水线开源处理器,实现了RV32I,目标是尽量减少FPGA的资源占用,在Cyclone IV系列FPGA上大约占用资源1200 LEs。采用VHDL编写代码。

(9)FlexPRET

FlexPRET[7]是由UCB设计发布的5级流水线、多线程处理器,目标是使用在实时嵌入式应用中,线程数量可配置为1-8。为了提高嵌入式处理器的资源利用率,每个硬件线程被标记为硬实时(hard real-time thread)或者软实时(soft real-time thread),硬实时线程按照固定的频率被调度,如果当前没有硬实时线程可调度,再调度软实时线程。使用Chisel编写代码。

(10)YARVI

YARVI(Yet Another RISC-V Implementation)是由RISC-V开发者Tommy Thorn设计发布的一款简单的、32位开源处理器,实现了RV32I,使用Verilog作为开发语言。其出发点不在于性能,而是要能够清晰、准确的实现RV32I。

开源SOC

Rocket-Chip

UCB为了方便用户学习,同时也为了便于重复使用已设计好的硬件模块,在GitHub上建立了Rocket-Chip Generator的项目,其中包括了Chisel、GCC、Rocket处理器,以及围绕Rocket的一系列总线单元、外设、缓存等,并且采用了参数化的配置方法,从而可以方便的创建不同性能要求的基于Rocket处理器的SoC。采用Chisel编写,主要的子模块如下。

Chisel:UCB设计的开源硬件编程语言。

Hardfloat:参数可配置的、兼容IEEE 754-2008标准的浮点单元。

Riscv-tools:开发工具,包括GCC、Newlib,以及移植的Linux。

Rocket:Rocket处理器,包括L1 Cache。

Uncore:实现了需要与Rocket紧密连接的功能单元,比如L2 Cache、L1 Coherence Hub等。

Juntions:实现了不同协议的接口之间的转换。

Rocketchip:顶层模块,同时也实现了内部总线TileLink向外部总线AXI或者AHB的转换。

前文介绍的BOOM、Z-scale都可以通过配置Rocket-Chip的不同参数得到。

LowRISC

LowRISC是由剑桥大学为主的一些研发人员成立的非营利性组织,主要是设计发布基于RISC-V指令集的64位开源SoC,其成员有树莓派的合作者,所以其目标是希望将设计的SoC做成类似于树莓派那样价格便宜、功能丰富、拥有大量用户的开源硬件。LowRISC发布的SoC的名称也是LowRISC,是在Rocket-Chip的基础上改进开发的,采用System Verilog编写改进部分的代码。主要特点是:

(1)Tagged Memory:给每一个存储位置都增加了一个Tag,目前是双字(64bit)对应一个Tag(4bit),目的是防止控制流劫持攻击,同时也有其他的一些用处,比如:垃圾回收、设置watchpoint等。为了实现Tagged Memory,LowRISC为RISC-V增加了两条指令用来读写Tag。2015年4月发布的0.1版本中具有该功能。

(2)Untethered:早期的Rocket-Chip需要依赖于一个通用处理器的协助才能够启动,才能够访问串口、网口、SD卡等外设,Untethered LowRISC通过实现(Memory mapping I/O)、片上NASTI interconnect等功能,解决了上述问题。2015年11月发布的0.2版本中具有该功能。

(3)Trace Debugging:引入了Open SoC Debug,支持Trace Debugging,可以收集指令执行记录,便于离线或者在线分析。2016年7月发布的0.3版本中具有该功能。

PULPino

PULPino是苏黎世联邦理工大学和波罗尼亚大学联合发布的基于RISC-V的开源处理器,其处理器核RI5CY在前文已述,苏黎世联邦理工大学和波罗尼亚大学本来设计的项目是PULP,这是一个多核SoC项目,考虑到这个项目太复杂,有许多IP、自定义工具集,不方便开源,所以开发者决定先开源一个单核SoC项目,即PULPino。PULPino直接使用了PULP项目的许多IP。

PULPino具有一个AXI互连总线,另外还有一个APB总线,用来连接低速外设,比如:GPIO、UART、I2C控制器、SPI Master控制器等。调试模块支持Advanced Debug Unit。PULPino包括一个Boot ROM,其中可以写入BootLoader,从而实现在启动的时候从外部Flash读入程序并执行。

RISC-V VHDL

RISC-V VHDL是俄罗斯的GNSS Sensor公司发布的基于Rocket的开源SoC,其前身是莫斯科物理技术学院的一个项目。该项目的处理器核直接就用的是Rocket,可以配置为只有L1Cache,也可以配置为包括L2Cache,在此基础上,提供了大量的IP核,采用类似LEON3的GRLIB库的方式,所有的IP核都是即插即用,RISC-V VHDL提供了一个AXI总线,IP核都挂载在该总线上。IP核包括:UART、GPIO、中断控制器、以太网控制器,此外还支持DSU(Debug Support Unit),均采用VHDL编写代码。

RISC-V VHDL中大多数IP核都是开源的,唯一商业的是GNSSLIB,这是一个与定位导航有关的库,也是RISC-V VHDL的特色。

2. RISC-V 文档

“RISC-V架构文档”分为“指令集文档”(riscv-spec-v2.2.pdf)和“特权架构文档”(riscv-privileged-v1.10.pdf)-https://riscv.org/specifications/

3. RISC-V 架构之魂

https://blog.csdn.net/zoomdy/article/details/79580772

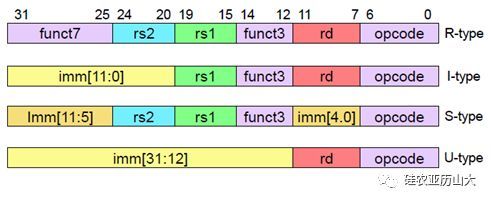

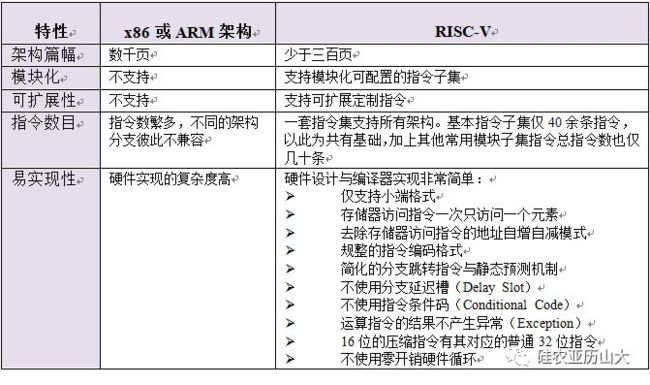

规整的指令编码

简洁的存储器访问指令

RISC-V架构使用专用的存储器读(Load)指令和存储器写(Store)指令访问存储器(Memory),其他的普通指令无法访问存储器,这种架构是RISC架构的常用的一个基本策略存储器访问的基本单位是字节(Byte)。

RISC-V的存储器读和存储器写指令支持一个字节(8位),半字(16位),单字(32位)为单位的存储器读写操作,如果是64位架构还可以支持一个双字(64位)为单位的存储器读写操作

RISC-V架构的存储器读和存储器写指令不支持地址自增自减的模式

松散存储器模型(Relaxed Memory Model),松散存储器模型对于访问不同地址的存储器读写指令的执行顺序不作要求

高效的分支跳转指令

RISC-V架构有两条无条件跳转指令(Unconditional Jump),jal与jalr指令。指令jal可用于进行子程序调用,跳转链接寄存器(Jump and Link-Register)指令jalr指令能够用于子程序返回指令

RISC-V架构有6条带条件跳转指令(Conditional Branch),这种带条件的跳转指令跟普通的运算指令一样直接使用2个整数操作数

对于没有配备硬件分支预测器的低端CPU,为了保证其性能,RISC-V的架构明确要求其采用默认的静态分支预测机制,即:如果是向后跳转的条件跳转指令,则预测为“跳”;如果是向前跳转的条件跳转指令,则预测为“不跳”

RISC-V架构特地定义了所有的带条件跳转指令跳转目标的偏移量(相对于当前指令的地址)都是有符号数

简洁的子程序调用

保存现场”和“恢复现场”放弃“Load Multiple”和“Store Multiple”指令可以大幅简化CPU的硬件设计

高性能超标量处理器由于硬件动态调度能力很强,可以有强大的分支预测电路保证CPU能够快速的跳转执行,从而可以选择使用公用的程序库(专门用于保存和恢复现场)的方式减少代码量,但是同时达到高性能。

无条件码执行

譬如在指令编码的头几位表示的是条件码(Conditional Code),只有该条件码对应的条件为真时,该指令才被真正执行。

RISC-V架构则放弃使用这种带“条件码”指令的方式,对于任何的条件判断都使用普通的带条件分支跳转指令。

无分支延迟槽

分支延迟槽就是指在每一条分支指令后面紧跟的一条或者若干条指令不受分支跳转的影响,不管分支是否跳转,这后面的几条指令都一定会被执行

RISC-V架构则放弃了分支延迟槽,

无零开销硬件循环

其思想是通过硬件的直接参与,通过设置某些循环次数寄存器(Loop Count),然后可以让程序自动地进行循环,每一次循环则Loop Count自动减1,这样持续循环直到Loop Count的值变成0,则退出循环。

简洁的运算指令

RISC-V架构的一个特殊之处是对任何的运算指令错误(包括整数与浮点指令)均不产生异常,而是产生某个特殊的默认值,同时,设置某些状态寄存器的状态位。

优雅的压缩指令子集

基本整数指令子集(字母I表示 )规定的指令长度均为等长的32位,这种等长指令定义使得仅支持整数指令子集的基本RISC-V CPU非常容易设计。但是等长的32位编码指令也会造成代码体积(Code Size)相对较大的问题

RISC-V定义了一种可选的压缩(Compressed)指令子集,由字母C表示,也可以由RVC表示。RISC-V具有后发优势,从一开始便规划了压缩指令,预留了足够的编码空间,16位长指令与普通的32位长指令可以无缝自由地交织在一起,处理器也没有定义额外的状态。

每一条16位长的指令都能一一找到其对应的原始32位指令

特权模式

ISC-V架构定义了三种工作模式,又称特权模式(Privileged Mode):

-

Machine Mode:机器模式,简称M Mode。

-

Supervisor Mode:监督模式,简称S Mode。

-

User Mode:用户模式,简称U Mode。

RISC-V架构定义M Mode为必选模式,另外两种为可选模式。通过不同的模式组合可以实现不同的系统。

RISC-V架构也支持几种不同的存储器地址管理机制,包括对于物理地址和虚拟地址的管理机制,使得RISC-V架构能够支持从简单的嵌入式系统(直接操作物理地址)到复杂的操作系统(直接操作虚拟地址)的各种系统。

CSR寄存器

RISC-V架构定义了一些控制和状态寄存器(Control and Status Register,CSR),用于配置或记录一些运行的状态。CSR寄存器是处理器核内部的寄存器,使用其自己的地址编码空间和存储器寻址的地址区间完全无关系。

CSR寄存器的访问采用专用的CSR指令,包括CSRRW、CSRRS、CSRRC、CSRRWI、CSRRSI以及CSRRCI指令。

中断和异常

中断和异常机制往往是处理器指令集架构中最为复杂而关键的部分。RISC-V架构定义了一套相对简单基本的中断和异常机制,但是也允许用户对其进行定制和扩展。

矢量指令子集

RISC-V架构目前虽然还没有定型矢量(Vector)指令子集

RISC-V架构将使用可变长度的矢量,而不是矢量定长的SIMD指令集(譬如ARM的NEON和Intel的MMX),从而能够灵活的支持不同的实现。追求低功耗小面积的CPU可以选择使用长度较短的硬件矢量进行实现,而高性能的CPU则可以选择较长的硬件矢量进行实现,并且同样的软件代码能够彼此兼容。

自定制指令扩展

RISC-V预留了大量的指令编码空间用于用户的自定义扩展,同时,还定义了四条Custom指令可供用户直接使用,每条Custom指令都有几个比特位的子编码空间预留,因此,用户可以直接使用四条Custom指令扩展出几十条自定义的指令