- C++ 11 Lambda表达式和min_element()与max_element()的使用_c++ lamda函数 min_element((1)

2401_84976182

程序员c语言c++学习

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上CC++开发知识点,真正体系化!由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新如果你需要这些资料,可以戳这里获取#include#include#includeusingnamespacestd;boolcmp(int

- FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)

阿牛的药铺

算法移植部署fpga开发verilog

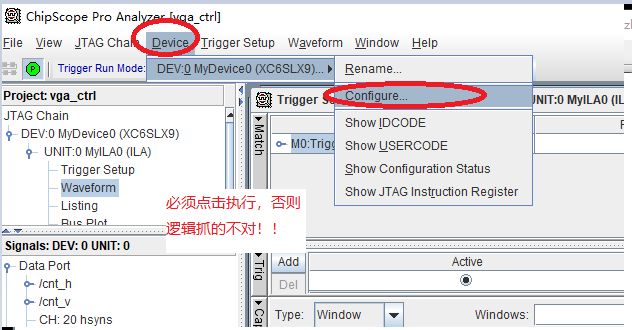

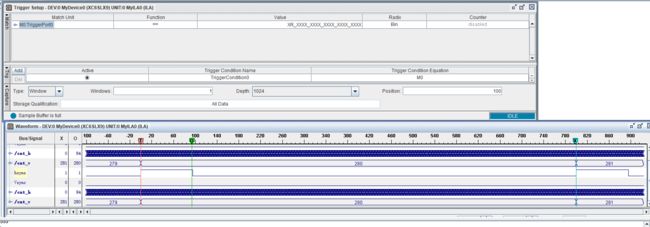

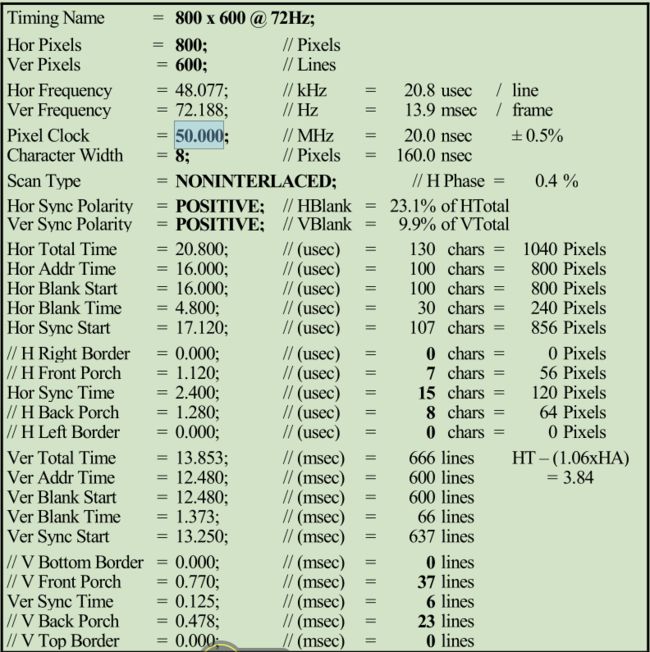

FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)引言:为什么这个FPGA入门路线能帮你快速上岗?本文设计了一条**"Verilog语法→工具链操作→光学项目实战→岗位技能对标"的阶梯式学习路径。不同于泛泛而谈的FPGA教程,我们聚焦光学类产品开发**核心能力(时序接口设计、图像处理算法移植、高速接口应用),通过3个递进式项目(从LED闪烁到图像边缘检测),

- PyTorch & TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)

阿牛的药铺

算法移植部署pytorchtensorflowfpga开发

PyTorch&TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)引言:为什么算法移植工程师必须掌握框架基础?针对光学类产品算法FPGA移植岗位需求(如可见光/红外图像处理),深度学习框架是算法落地的"桥梁"——既要用PyTorch/TensorFlow验证算法可行性,又要将训练好的模型(如CNN、目标检测)转换为FPGA可部署的格式(ONNX、TFLite)。本文采用"

- 基于链家网的二手房数据采集清洗与可视化分析

Mint_Datazzh

项目selenium网络爬虫

个人学习内容笔记,仅供参考。项目链接:https://gitee.com/rongwu651/lianjia原文链接:基于链家网的二手房数据采集清洗与可视化分析–笔墨云烟研究内容该课题的主要目的是通过将二手房网站上的存量与已销售房源,构建一个二手房市场行情情况与房源特点的可视化平台。该平台通过HTML架构和Echarts完成可视化的搭建。因此,该课题的主要研究内容就是如何利用相关技术设计并实现这样

- 算法学习笔记:17.蒙特卡洛算法 ——从原理到实战,涵盖 LeetCode 与考研 408 例题

在计算机科学和数学领域,蒙特卡洛算法(MonteCarloAlgorithm)以其独特的随机抽样思想,成为解决复杂问题的有力工具。从圆周率的计算到金融风险评估,从物理模拟到人工智能,蒙特卡洛算法都发挥着不可替代的作用。本文将深入剖析蒙特卡洛算法的思想、解题思路,结合实际应用场景与Java代码实现,并融入考研408的相关考点,穿插图片辅助理解,帮助你全面掌握这一重要算法。蒙特卡洛算法的基本概念蒙特卡

- 分布式学习笔记_04_复制模型

NzuCRAS

分布式学习笔记架构后端

常见复制模型使用复制的目的在分布式系统中,数据通常需要被分布在多台机器上,主要为了达到:拓展性:数据量因读写负载巨大,一台机器无法承载,数据分散在多台机器上仍然可以有效地进行负载均衡,达到灵活的横向拓展高容错&高可用:在分布式系统中单机故障是常态,在单机故障的情况下希望整体系统仍然能够正常工作,这时候就需要数据在多台机器上做冗余,在遇到单机故障时能够让其他机器接管统一的用户体验:如果系统客户端分布

- 算法学习笔记:15.二分查找 ——从原理到实战,涵盖 LeetCode 与考研 408 例题

呆呆企鹅仔

算法学习算法学习笔记考研二分查找

在计算机科学的查找算法中,二分查找以其高效性占据着重要地位。它利用数据的有序性,通过不断缩小查找范围,将原本需要线性时间的查找过程优化为对数时间,成为处理大规模有序数据查找问题的首选算法。二分查找的基本概念二分查找(BinarySearch),又称折半查找,是一种在有序数据集合中查找特定元素的高效算法。其核心原理是:通过不断将查找范围减半,快速定位目标元素。与线性查找逐个遍历元素不同,二分查找依赖

- EMQX 社区版单机和集群部署

pcj_888

MQTTMQTTEMQ

EMQ支持Docker,宿主机,k8s部署;支持单机或集群部署。以下给出EMQX社区版单机和集群部署方法1.Docker单机部署官方推荐最小配置:2核4G下载容器镜像dockerpullemqx/emqx:5.3.2启动容器dockerrun-d--nameemqx\-p1883:1883\-p8083:8083\-p8883:8883\-p8084:8084\-p18083:18083\emqx

- 入门html这篇文章就够了

ξ流ぁ星ぷ132

html前端

HTML笔记文章目录HTML笔记html介绍什么是htmlhtml的作用HTML标签介绍常用标签标签and标签and标签u标签del删除线br标签用于换行pre标签,预处理标签span标签div标签sub标签andsup标签hr标签h1,h2...h6标签:HTML5中的语义标签:特殊字符img标签a标签第一种用法:超链接第二种用法:锚点video标签表格标签:form标签input标签selec

- [特殊字符] 实时数据洪流突围战:Flink+Paimon实现毫秒级分析的架构革命(附压测报告)——日均百亿级数据处理成本降低60%的工业级方案

Lucas55555555

flink大数据

引言:流批一体的时代拐点据阿里云2025白皮书显示,实时数据处理需求年增速达240%,但传统Lambda架构资源消耗占比超运维成本的70%。某电商平台借助Flink+Paimon重构实时数仓后,端到端延迟从分钟级压缩至800ms,计算资源节省5.6万核/月。技术红利窗口期:2025年ApachePaimon1.0正式发布,支持秒级快照与湖仓一体,成为替代Iceberg的新范式一、痛点深挖:实时数仓

- OKHttp3源码分析——学习笔记

Sincerity_

源码相关Okhttp源码解析读书笔记httpclientcache

文章目录1.HttpClient与HttpUrlConnection的区别2.OKHttp源码分析使用步骤:dispatcher任务调度器,(后面有详细说明)Request请求RealCallAsyncCall3.OKHttp架构分析1.异步请求线程池,Dispather2.连接池清理线程池-ConnectionPool3.缓存整理线程池DisLruCache4.Http2异步事务线程池,http

- 盲超分的核心概念

小冷爱读书

数学建模盲超分超分重建

一、盲超分的本质与数学建模1.退化过程的数学表达低分辨率图像(LR)可看作高分辨率图像(HR)经过退化模型后的结果::观测到的低分辨率图像:待恢复的高分辨率图像:模糊核(BlurKernel)⊗:卷积操作↓:下采样(步长为):加性噪声(如高斯噪声、泊松噪声等)盲超分的核心问题:在未知、、的情况下,从估计。2.为什么传统超分方法会失效?传统方法(如SRCNN、EDSR)假设退化是固定的(如双三次下采

- vue3面试题(个人笔记)

武昌库里写JAVA

面试题汇总与解析课程设计springbootvue.jsjava学习

vue3比vue2有什么优势?性能更好,打包体积更小,更好的ts支持,更好的代码组织,更好的逻辑抽离,更多的新功能。描述Vue3生命周期CompositionAPI的生命周期:onMounted()onUpdated()onUnmounted()onBeforeMount()onBeforeUpdate()onBeforeUnmount()onErrorCaptured()onRenderTrac

- Python学习笔记5|条件语句和循环语句

iamecho9

Python从0到1学习笔记python学习笔记

一、条件语句条件语句用于根据不同的条件执行不同的代码块。1、if语句基本语法:if布尔型语句1:代码块#语句1为True时执行的代码示例:age=int(input("请输入你的年龄:"))ifage>=18:print("你已成年")2、if-else语句如果if条件不成立,则执行else代码块:if布尔型语句1:代码块#语句1为True时执行的代码else:代码块#语句1为False时执行的代

- swagger【个人笔记】

撰卢

笔记java

文章目录swagger导入mave坐标在配置类(WebMvcConfiguration)中加入knife4j相关配置设置静态资源映射,主要是让拦截器放行swagger常用注解@Api(tags="\[描述这个类的作用]")@ApiModel(description="\[描述这个类的作用]")@ApiModelProPerty("描述这个类的作用")@ApiOperation("\[描述方法的作用

- 【个人笔记】负载均衡

撰卢

笔记负载均衡运维

文章目录nginx反向代理的好处负载均衡负载均很的配置方式均衡负载的方式nginx反向代理的好处提高访问速度进行负载均衡保证后端服务安全负载均衡负载均衡,就是把大量的请求按照我们指定的方式均衡的分配给集群中的每台服务器负载均很的配置方式upstreamwebservers{server192.168.100.128:8080server192.168.100.129:8080}server{lis

- FPGA 设计中的 “Create HDL Wrapper“ 和 “Generating Output Products“ 的区别

行者..................

fpga开发

CreateHDLWrapper(创建HDL包装器)目的:为顶层设计模块(通常是BlockDesign/IPIntegrator设计)创建一个HDL包装文件功能:将图形化/框图设计的BlockDesign转换为可综合的HDL代码(Verilog或VHDL)创建一个顶层模块,将所有IP核和连接实例化使用场景:当使用IPIntegrator创建BlockDesign后需要将图形化设计转换为HDL代码以

- 低温冷启动 & 高温热启动

hahaha6016

fpga开发

低温冷启动1.在低温下,晶体管的阈值电压可能升高,导致时序路径变慢,从而可能引起建立时间(setuptime)违规。另外,也可能出现保持时间(holdtime)违规,因为低温下信号传播速度可能变快(但通常低温下延迟增加,所以建立时间问题更常见)。2.droppinglogiccore意味着在低温下某个逻辑核心(可能是一个特定的模块或IP核)无法正常启动或工作,导致功能失效3.cellname,这通

- 在 Obsidian 中本地使用 DeepSeek — 无需互联网!

知识大胖

NVIDIAGPU和大语言模型开发教程人工智能deepseek

简介您是否想在Obsidian内免费使用类似于ChatGPT的本地LLM?如果是,那么本指南适合您!我将引导您完成在Obsidian中安装和使用DeepSeek-R1模型的确切步骤,这样您就可以在笔记中拥有一个由AI驱动的第二大脑。推荐文章《24GBGPU中的DeepSeekR1:UnslothAI针对671B参数模型进行动态量化》权重1,DeepSeek类《在RaspberryPi上运行语音识别

- 5G标准学习笔记14 - CSI--RS概述

刘孬孬沉迷学习

5G学习笔记信息与通信

5G标准学习笔记14-CSI–RS概述大家好~,这里是刘孬孬,今天带着大家一起学习一下5GNR中一个非常非常重要的参考信号------------------CSI-RS信号,CSI-RS不是持续发送,UE只能在网络明确配置了CSI-RS的情况下才能使用其进行信道测量。前言对于CSI-RS,肯定还离不开前面所说的CSI(channelstateinformation),前面也讲过CSI对于MIMO

- 5G标准学习笔记06-基于AI/ML波束管理

刘孬孬沉迷学习

5G学习笔记

5G标准学习笔记06-基于AI/ML波束管理前言前面对于孬孬学习了波束管理的概述,下面要进一步来看一下传统波束管理和现在3GPP中推动的AL/ML波束管理之前的区别联系。一、传统波束管理方法流程传统BM流程主要包括以下步骤:波束扫描(BeamSweeping):gNB通过顺序发送多个窄波束(SSB或CSI-RS),覆盖整个服务区域,UE测量每个波束的信号质量(如L1-RSRP或L1-SINR)。波

- 5G标准学习笔记03- CSI 反馈增强概述

刘孬孬沉迷学习

5G笔记学习

5G标准学习笔记03-CSI反馈增强概述大家好,最近在研究AI/ML3gpp标准NR空口的有关内容,后面可能会给大家介绍一下对应的有关内容AI/ML在3GPP标准中的研究进展在AI/ML在NR空口的应用中,对应标准主要聚焦了3个case进行讨论研究分别是:CSI反馈增强;波束管理;定位精度增强;这三个内容可能比较涉及RAN1/2的具体内容,后面会基于这个进行一定的介绍。今天主要是主要介绍CSI反馈

- 运维笔记<4> xxl-job打通

GeminiJM

运维javaxxl-job

新的一天,来点新的运维业务,今天是xxl-job的打通其实在非集群中,xxl-job的使用相对是比较简单的,相信很多人都有使用的经验这次我们的业务场景是在k8s集群中,用xxl-job来做定时调度加上第一次倒腾,也是遇到了不少问题,在这里做一些记录1.xxl-job的集群安装首先是xxl-job的集群安装先贴上xxl-jobsql初始化文件的地址:xxl-job/doc/db/tables_xxl

- 两台pc如何高速度传输大文件

费城之鹰

其他两台电脑高速传输文件局域网不适用U盘传输资料网线直连两台电脑传资料

今天笔记本跑一个大一点的项目,8G的内存直接100%,i5的CPU直接75%并且在超频工作了,原本1.6Ghz的频率直接飙到了3.8Ghz,由于项目性质原因,采用的是公司配的笔记本,但是年初采购的联想E480,还在三包时间段内,公司不允许拆机增加内存,只能换一台新的台式机,听起来挺爽,有新设备,但是办公区域不准使用U盘这一类的存储设备,这就蛋疼了,大半年了项目代码,资料全在这个不够用的笔记本里,问

- 学习笔记(33):matplotlib绘制简单图表-绘制混淆矩阵热图

宁儿数据安全

#机器学习学习笔记matplotlib

学习笔记(33):matplotlib绘制简单图表-绘制混淆矩阵热图一、绘制混淆矩阵热图代码解析1.1、导入必要的库importmatplotlib.pyplotaspltfromsklearn.metricsimportconfusion_matriximportseabornassnsmatplotlib.pyplot:Python中最常用的绘图库,用于创建各种图表confusion_matr

- 玩转Docker | 使用Docker部署NotepadMX笔记应用程序

心随_风动

玩转Dockerdocker笔记eureka

玩转Docker|使用Docker部署NotepadMX笔记应用程序前言一、NotepadMX介绍工具简介主要特点二、系统要求环境要求环境检查Docker版本检查检查操作系统版本三、部署NotepadMX服务下载NotepadMX镜像编辑部署文件创建容器检查容器状态检查服务端口安全设置四、访问NotepadMX服务访问NotepadMX首页设置访问验证编辑笔记总结前言在如今快节奏的工作与学习中,一

- 【前端】异步任务风控验证与轮询机制技术方案(通用笔记版)

一、背景场景在某类生成任务中,例如用户点击“执行任务”按钮后触发一个较耗时的后端操作(如生成报告、渲染图像、转码视频等),由于其调用了模型、渲染服务或需要较长处理时间,为了防止接口被频繁恶意调用,系统需要加入风控验证机制。此外,因任务处理为异步,前端无法立即获得最终结果,因此需通过轮询方式定期查询任务状态,等待任务完成后展示结果。二、整体流程说明1.用户点击“执行任务”按钮:前端调用风控接口/ap

- 数据分析案例-电脑笔记本价格数据可视化分析3

艾派森

数据分析信息可视化python数据分析数据挖掘电脑

♂️个人主页:@艾派森的个人主页✍作者简介:Python学习者希望大家多多支持,我们一起进步!如果文章对你有帮助的话,欢迎评论点赞收藏加关注+目录1.项目背景2.数据集介绍3.技术工具

- LLaMA 学习笔记

AI算法网奇

深度学习基础人工智能深度学习

目录LLaMA模型结构:模型微调手册:推理示例:指定位置加载模型测试ok:模型下载:llama-stack下载modelscope下载LLaMA优化技术RMSNormSwiGLU激活函数旋转位置编码(RoPE)LLaMA模型结构:llama3结构详解-CSDN博客模型微调手册:大模型微调LLaMA详细指南(准备环境、数据、配置微调参数+微调过程)_llama微调-CSDN博客显存占用:FP16/B

- BOOT_KEY按键(学习笔记)

小高Baby@

学习笔记

先来让我们了解一下GPIO是什么吧,它在单片机中也有很重要的作用,接下来我们来看看吧。esp32C3是QFN32封装(一种集成电路(IC)封装类型),GPIO引脚一共有22个,从GPIO-0到GPIO-21。从理论上来说,所有的IO引脚都可以复用为任何外设功能,但有些引脚用作连接芯片内部FLASH或者外部FLASH功能时,官方不建议用作其它用途。esp32c3的GPIO,可以用作输入、输出,可以配

- PHP,安卓,UI,java,linux视频教程合集

cocos2d-x小菜

javaUIlinuxPHPandroid

╔-----------------------------------╗┆

- zookeeper admin 笔记

braveCS

zookeeper

Required Software

1) JDK>=1.6

2)推荐使用ensemble的ZooKeeper(至少3台),并run on separate machines

3)在Yahoo!,zk配置在特定的RHEL boxes里,2个cpu,2G内存,80G硬盘

数据和日志目录

1)数据目录里的文件是zk节点的持久化备份,包括快照和事务日

- Spring配置多个连接池

easterfly

spring

项目中需要同时连接多个数据库的时候,如何才能在需要用到哪个数据库就连接哪个数据库呢?

Spring中有关于dataSource的配置:

<bean id="dataSource" class="com.mchange.v2.c3p0.ComboPooledDataSource"

&nb

- Mysql

171815164

mysql

例如,你想myuser使用mypassword从任何主机连接到mysql服务器的话。

GRANT ALL PRIVILEGES ON *.* TO 'myuser'@'%'IDENTIFIED BY 'mypassword' WI

TH GRANT OPTION;

如果你想允许用户myuser从ip为192.168.1.6的主机连接到mysql服务器,并使用mypassword作

- CommonDAO(公共/基础DAO)

g21121

DAO

好久没有更新博客了,最近一段时间工作比较忙,所以请见谅,无论你是爱看呢还是爱看呢还是爱看呢,总之或许对你有些帮助。

DAO(Data Access Object)是一个数据访问(顾名思义就是与数据库打交道)接口,DAO一般在业

- 直言有讳

永夜-极光

感悟随笔

1.转载地址:http://blog.csdn.net/jasonblog/article/details/10813313

精华:

“直言有讳”是阿里巴巴提倡的一种观念,而我在此之前并没有很深刻的认识。为什么呢?就好比是读书时候做阅读理解,我喜欢我自己的解读,并不喜欢老师给的意思。在这里也是。我自己坚持的原则是互相尊重,我觉得阿里巴巴很多价值观其实是基本的做人

- 安装CentOS 7 和Win 7后,Win7 引导丢失

随便小屋

centos

一般安装双系统的顺序是先装Win7,然后在安装CentOS,这样CentOS可以引导WIN 7启动。但安装CentOS7后,却找不到Win7 的引导,稍微修改一点东西即可。

一、首先具有root 的权限。

即进入Terminal后输入命令su,然后输入密码即可

二、利用vim编辑器打开/boot/grub2/grub.cfg文件进行修改

v

- Oracle备份与恢复案例

aijuans

oracle

Oracle备份与恢复案例

一. 理解什么是数据库恢复当我们使用一个数据库时,总希望数据库的内容是可靠的、正确的,但由于计算机系统的故障(硬件故障、软件故障、网络故障、进程故障和系统故障)影响数据库系统的操作,影响数据库中数据的正确性,甚至破坏数据库,使数据库中全部或部分数据丢失。因此当发生上述故障后,希望能重构这个完整的数据库,该处理称为数据库恢复。恢复过程大致可以分为复原(Restore)与

- JavaEE开源快速开发平台G4Studio v5.0发布

無為子

我非常高兴地宣布,今天我们最新的JavaEE开源快速开发平台G4Studio_V5.0版本已经正式发布。

访问G4Studio网站

http://www.g4it.org

2013-04-06 发布G4Studio_V5.0版本

功能新增

(1). 新增了调用Oracle存储过程返回游标,并将游标映射为Java List集合对象的标

- Oracle显示根据高考分数模拟录取

百合不是茶

PL/SQL编程oracle例子模拟高考录取学习交流

题目要求:

1,创建student表和result表

2,pl/sql对学生的成绩数据进行处理

3,处理的逻辑是根据每门专业课的最低分线和总分的最低分数线自动的将录取和落选

1,创建student表,和result表

学生信息表;

create table student(

student_id number primary key,--学生id

- 优秀的领导与差劲的领导

bijian1013

领导管理团队

责任

优秀的领导:优秀的领导总是对他所负责的项目担负起责任。如果项目不幸失败了,那么他知道该受责备的人是他自己,并且敢于承认错误。

差劲的领导:差劲的领导觉得这不是他的问题,因此他会想方设法证明是他的团队不行,或是将责任归咎于团队中他不喜欢的那几个成员身上。

努力工作

优秀的领导:团队领导应该是团队成员的榜样。至少,他应该与团队中的其他成员一样努力工作。这仅仅因为他

- js函数在浏览器下的兼容

Bill_chen

jquery浏览器IEDWRext

做前端开发的工程师,少不了要用FF进行测试,纯js函数在不同浏览器下,名称也可能不同。对于IE6和FF,取得下一结点的函数就不尽相同:

IE6:node.nextSibling,对于FF是不能识别的;

FF:node.nextElementSibling,对于IE是不能识别的;

兼容解决方式:var Div = node.nextSibl

- 【JVM四】老年代垃圾回收:吞吐量垃圾收集器(Throughput GC)

bit1129

垃圾回收

吞吐量与用户线程暂停时间

衡量垃圾回收算法优劣的指标有两个:

吞吐量越高,则算法越好

暂停时间越短,则算法越好

首先说明吞吐量和暂停时间的含义。

垃圾回收时,JVM会启动几个特定的GC线程来完成垃圾回收的任务,这些GC线程与应用的用户线程产生竞争关系,共同竞争处理器资源以及CPU的执行时间。GC线程不会对用户带来的任何价值,因此,好的GC应该占

- J2EE监听器和过滤器基础

白糖_

J2EE

Servlet程序由Servlet,Filter和Listener组成,其中监听器用来监听Servlet容器上下文。

监听器通常分三类:基于Servlet上下文的ServletContex监听,基于会话的HttpSession监听和基于请求的ServletRequest监听。

ServletContex监听器

ServletContex又叫application

- 博弈AngularJS讲义(16) - 提供者

boyitech

jsAngularJSapiAngularProvider

Angular框架提供了强大的依赖注入机制,这一切都是有注入器(injector)完成. 注入器会自动实例化服务组件和符合Angular API规则的特殊对象,例如控制器,指令,过滤器动画等。

那注入器怎么知道如何去创建这些特殊的对象呢? Angular提供了5种方式让注入器创建对象,其中最基础的方式就是提供者(provider), 其余四种方式(Value, Fac

- java-写一函数f(a,b),它带有两个字符串参数并返回一串字符,该字符串只包含在两个串中都有的并按照在a中的顺序。

bylijinnan

java

public class CommonSubSequence {

/**

* 题目:写一函数f(a,b),它带有两个字符串参数并返回一串字符,该字符串只包含在两个串中都有的并按照在a中的顺序。

* 写一个版本算法复杂度O(N^2)和一个O(N) 。

*

* O(N^2):对于a中的每个字符,遍历b中的每个字符,如果相同,则拷贝到新字符串中。

* O(

- sqlserver 2000 无法验证产品密钥

Chen.H

sqlwindowsSQL ServerMicrosoft

在 Service Pack 4 (SP 4), 是运行 Microsoft Windows Server 2003、 Microsoft Windows Storage Server 2003 或 Microsoft Windows 2000 服务器上您尝试安装 Microsoft SQL Server 2000 通过卷许可协议 (VLA) 媒体。 这样做, 收到以下错误信息CD KEY的 SQ

- [新概念武器]气象战争

comsci

气象战争的发动者必须是拥有发射深空航天器能力的国家或者组织....

原因如下:

地球上的气候变化和大气层中的云层涡旋场有密切的关系,而维持一个在大气层某个层次

- oracle 中 rollup、cube、grouping 使用详解

daizj

oraclegroupingrollupcube

oracle 中 rollup、cube、grouping 使用详解 -- 使用oracle 样例表演示 转自namesliu

-- 使用oracle 的样列库,演示 rollup, cube, grouping 的用法与使用场景

--- ROLLUP , 为了理解分组的成员数量,我增加了 分组的计数 COUNT(SAL)

- 技术资料汇总分享

Dead_knight

技术资料汇总 分享

本人汇总的技术资料,分享出来,希望对大家有用。

http://pan.baidu.com/s/1jGr56uE

资料主要包含:

Workflow->工作流相关理论、框架(OSWorkflow、JBPM、Activiti、fireflow...)

Security->java安全相关资料(SSL、SSO、SpringSecurity、Shiro、JAAS...)

Ser

- 初一下学期难记忆单词背诵第一课

dcj3sjt126com

englishword

could 能够

minute 分钟

Tuesday 星期二

February 二月

eighteenth 第十八

listen 听

careful 小心的,仔细的

short 短的

heavy 重的

empty 空的

certainly 当然

carry 携带;搬运

tape 磁带

basket 蓝子

bottle 瓶

juice 汁,果汁

head 头;头部

- 截取视图的图片, 然后分享出去

dcj3sjt126com

OSObjective-C

OS 7 has a new method that allows you to draw a view hierarchy into the current graphics context. This can be used to get an UIImage very fast.

I implemented a category method on UIView to get the vi

- MySql重置密码

fanxiaolong

MySql重置密码

方法一:

在my.ini的[mysqld]字段加入:

skip-grant-tables

重启mysql服务,这时的mysql不需要密码即可登录数据库

然后进入mysql

mysql>use mysql;

mysql>更新 user set password=password('新密码') WHERE User='root';

mysq

- Ehcache(03)——Ehcache中储存缓存的方式

234390216

ehcacheMemoryStoreDiskStore存储驱除策略

Ehcache中储存缓存的方式

目录

1 堆内存(MemoryStore)

1.1 指定可用内存

1.2 驱除策略

1.3 元素过期

2 &nbs

- spring mvc中的@propertysource

jackyrong

spring mvc

在spring mvc中,在配置文件中的东西,可以在java代码中通过注解进行读取了:

@PropertySource 在spring 3.1中开始引入

比如有配置文件

config.properties

mongodb.url=1.2.3.4

mongodb.db=hello

则代码中

@PropertySource(&

- 重学单例模式

lanqiu17

单例Singleton模式

最近在重新学习设计模式,感觉对模式理解更加深刻。觉得有必要记下来。

第一个学的就是单例模式,单例模式估计是最好理解的模式了。它的作用就是防止外部创建实例,保证只有一个实例。

单例模式的常用实现方式有两种,就人们熟知的饱汉式与饥汉式,具体就不多说了。这里说下其他的实现方式

静态内部类方式:

package test.pattern.singleton.statics;

publ

- .NET开源核心运行时,且行且珍惜

netcome

java.net开源

背景

2014年11月12日,ASP.NET之父、微软云计算与企业级产品工程部执行副总裁Scott Guthrie,在Connect全球开发者在线会议上宣布,微软将开源全部.NET核心运行时,并将.NET 扩展为可在 Linux 和 Mac OS 平台上运行。.NET核心运行时将基于MIT开源许可协议发布,其中将包括执行.NET代码所需的一切项目——CLR、JIT编译器、垃圾收集器(GC)和核心

- 使用oscahe缓存技术减少与数据库的频繁交互

Everyday都不同

Web高并发oscahe缓存

此前一直不知道缓存的具体实现,只知道是把数据存储在内存中,以便下次直接从内存中读取。对于缓存的使用也没有概念,觉得缓存技术是一个比较”神秘陌生“的领域。但最近要用到缓存技术,发现还是很有必要一探究竟的。

缓存技术使用背景:一般来说,对于web项目,如果我们要什么数据直接jdbc查库好了,但是在遇到高并发的情形下,不可能每一次都是去查数据库,因为这样在高并发的情形下显得不太合理——

- Spring+Mybatis 手动控制事务

toknowme

mybatis

@Override

public boolean testDelete(String jobCode) throws Exception {

boolean flag = false;

&nbs

- 菜鸟级的android程序员面试时候需要掌握的知识点

xp9802

android

熟悉Android开发架构和API调用

掌握APP适应不同型号手机屏幕开发技巧

熟悉Android下的数据存储

熟练Android Debug Bridge Tool

熟练Eclipse/ADT及相关工具

熟悉Android框架原理及Activity生命周期

熟练进行Android UI布局

熟练使用SQLite数据库;

熟悉Android下网络通信机制,S