高端PCB设计相关知识整理

PCB的设计布局布线实际上是一门很复杂而且大部分靠经验来做的学问,很多东西也有点玄乎,但有很多经验性的结论和公式还是可以参考的

保证原创,一天不一定写的完

CH.1 更加严重的电磁干扰

首先基本上微电子发展趋势永远是集成化程度越来越高,不可避免带来元器件密度很大,而前十几年出现的SMT(Surface Mounted Technology)和COB(Chip on Board)技术和SMC/SMD/裸片的出现,给了继续提高集成度的可能。

一个典型的贴片机

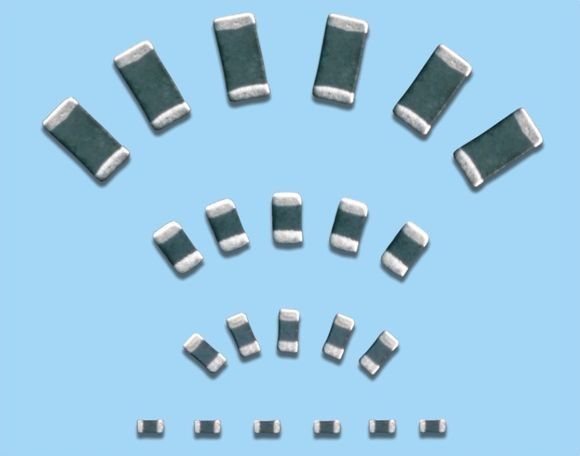

SMD热敏电阻,体积是普通电阻的十几分之一

但随之而来的,就是比普通集成电路更为严重的元器件之间相互的电磁干扰

当然实际中不仅如此,红外炉再流焊是一种常用的SMT焊接技术,但元器件的布局又会影响焊接质量,加之射频电路的EMC又要求每个模块都尽量不产生电磁辐射,并且具有相当的抗EMI能力。

而且根据经验,射频电路的性能还会与CPU处理板相互影响,因此在PCB设计的时候,会更加棘手。

但一般来说,设计的时候都有以下要求

·所有的元器件尽可能同一方向排列,避免互相干扰,同时要注意PCB进入熔锡系统的方向,,以免出现虚焊漏焊

·元器件至少要保留一定的空间,典型值为0.5mm

·通常来说,双面板中SMD/SMC元件和分立元件要分两面放置

当然这仅仅是很基础的一些方面,通常来说,强电信号和弱电信号必须分开,模拟和数字信号也要分开。

还有一个基本常识是要求完成同一功能的电路尽可能安排在一起,至少不能离的很远,以减小信号环路面积,防止劣化。

对于有些对电磁干扰敏感的元件(比如传感器)要按照敏感程度来区分,尽量避免板上干扰源

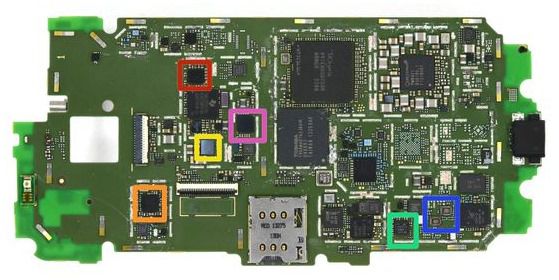

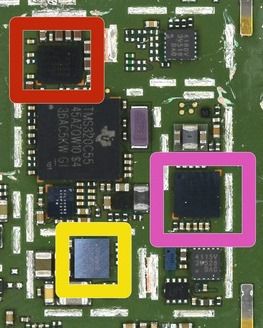

PCB来自motorola公司的MOTO X

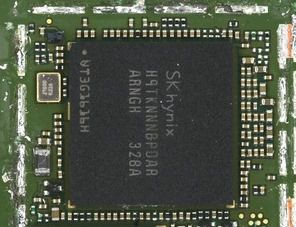

来自海力士的内存,注意SMD电容/电阻的布局和方向。

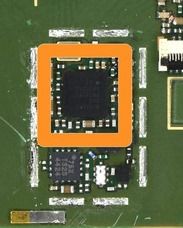

来自高通公司的 WCN3680 802.11ac Combo Wi-Fi/Bluetooth/FM芯片,会产生较大电磁泄露,因此设计人员给予单独的屏蔽罩,并且单独放置在PCB的一边,进一步减小对于其他电磁敏感元件的影响。

带有德州仪器标志的是C55x系列DSP芯片

棕红色是Codec,音频编解码器

红色NXP TFA9890 D类音频放大器

之后用一个屏蔽罩做EMI屏蔽。

这几个部件功能都是接近,都是负责音频处理,所谓的信号环路最小原则,与射频部分和CPU模块的距离也明显更远。

摩托罗拉和诺基亚是少数几个能设计出教科书式的PCB设计厂家

更为广泛来说,屏蔽罩是一个麦克斯韦笼,这是最为简单也是最为有效的一种方法,缺点是会增加成本,不仅仅是物料,代工厂的收费是以加工时间为度量,加工时间长则收费高,因此也有部分厂家不愿采用。

如果在部分情况下,不可能使用屏蔽罩,也有一些方法来解决,最为常见的是增加滤波/抗干扰电路,并且加强对于电源的去耦,优化地线电源线的布局等,但这种方法一般来说,会增加电路的复杂程度,并带来通常意料不到的问题。

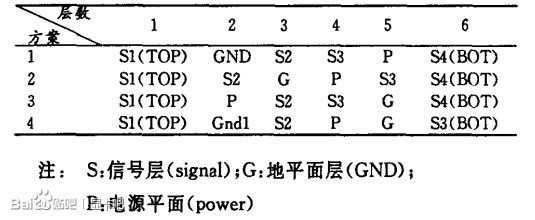

通常来说,PCB的设计第一步是根据实际情况选择PCB的形状,下一步就是层(layer)的设置,层设置不合理的结果是毁灭性的,通常PCB的层又分为电源层、底线层和信号层,而层的选择中,层的相对位置、地平面/电源的分割、PCB的布线、接口电路的处理又有这非常大影响。

层的选择第一步是层数,层数的选择不宜太多也不宜太少,太多则信号线过于密集,成本太高;太少则不能达到设计要求,对于电磁兼容的要求,通常也是比较好的方式是通过适当的增加地平面来解决。

对于电源层一般需要解决多种电源/电源的供电问题,需要内电层分割。

信号层则比较复杂,(走线问题单独介绍)首先就是走线密度,太密则相互串扰,太疏则信号线不够,并且重要信号譬如时钟和复位信号需要单独屏蔽和隔离。

在考虑过层数量问题孩子后,就是层排列,也有部分基础原则:

·电源平面与相应地平面相邻:由于电源和地本身存在自阻抗,可以形成耦合电容,这个时候在PCB板上设置退耦电容,可以达到去耦的效果,降低电源阻抗,相当于滤波。

·相邻层的信号不要跨分割区,就是信号环路最小原则。

·关键信号(高频高速或者时钟)要于地平面相邻,可减少电磁泄露,也相当于地给信号做屏蔽。

比较常见的6层PCB布局方案:

CH.2 越来越难的散热设计

对于常规的PCB来说,一般来说散热遵循常规是热点分散原则,即「发热最大的器件放置在最佳散热位置」,并且减小元件与板之间的热阻。但这种方法近年来却逐渐表现疲软,尤其是在手机上,归根结底,虽然工艺更好,算法更好,平台功耗只升不降,所以也逐渐有其他方法来解决。

一般来说,在设计散热的时候的大致思路是估计发热器件的功耗,估算其需要的面积,在这个面积中不能放置其他发热元件,随后才是设计散热。

在手机中,发热器件除了CPU、RAM之外,大部分都是功放、收发器、基带处理器、电源管理芯片、电压芯片以及DC-DC电感,其中功放、CPU、基带处理器都是发热大户。

在这里首先要知道的一个经验值是自然对流冷去的热流密度为0.8mW/mm²,即对于芯片来说,每平方毫米单纯靠空气对流可以对应0.8mW所带来的热量。

以这个值做参考,计算大概需要的面积(芯片功耗可在datasheet中查找,厂家是一定会给的)。

随后就是放置元件,一般来说,发热旗舰不应该放置在PCB的边缘和角落放置,更不该在其背面放置发热器件。

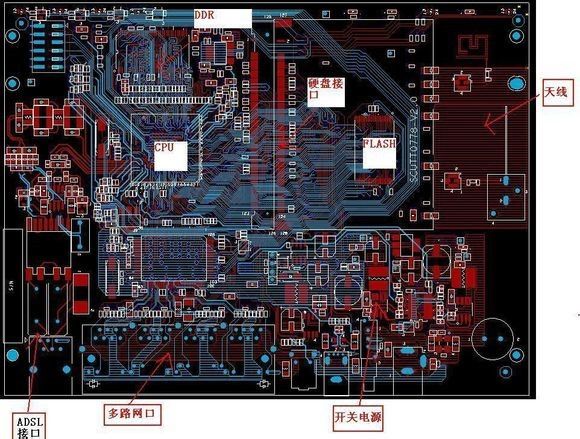

Samsung Galaxy SII i9100

不太成功的设计,发热器件过于集中

LG E960 Nexus 4

应该是最早的「中框散热+三层」式设计,如今这个设计被比较广泛的采用,尤其是发热较大的设备。

这个设计在vivo xplay、MX3、米3都能看出一点影子来

CH.3 还是要靠人的走线

PCB的走线如果说全让人来做,几乎是不可能的事情。

所幸现在EDA和CAD的功能越发强大,但一般来说,计算机设计出来走线,通常只是「能用」而已,与「优秀」还有一定的距离。

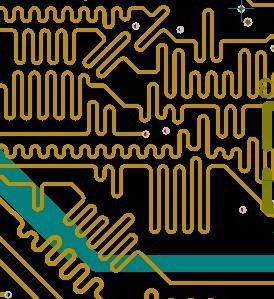

通常而言,走线的最基本要求是「不相容信号尽可能相互远离」的原则,即数字模拟、高速低速、强电弱电、高压低压之间尽可能远离,同时「避免长距离平行走线」

,以防耦合。

对于信号线,一般不允许出现分支,这样通常会破坏导线特性阻抗的一致性,并且在分叉点产生谐波和发射(类似于河流中的漩涡),使得信号辐射出去,带来更多问题。

另一个更加基本的原则是「135°」原则,即信号线在走线的时候拐角不能采用90°直角转弯,这样会产生寄生电容,对于高速高频电路和数字电路影响尤为严重,会减缓上升时间、造成信号的反射、产生EMI,所以基本看任何一个PCB,走线都大概如此:

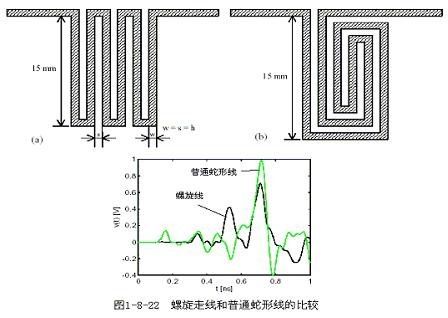

(图中另一种常见走线方式是蛇形走线,这种走线作用是用来调节延时,满足系统时序设计要求,在数字电路中非常常见,但没有滤波或抗干扰的能力,只可能降低信号质量,因此近年多采用螺旋形走线)

螺旋形的走线是上图右侧

根据贴吧内容整理,原帖地址:http://tieba.baidu.com/p/2583004223