STM32系统时钟配置

STM32启动后的第一步对于开发者来说就是系统时钟(RCC)的配置了,STM32系统默认用户外接8M晶振,经过倍频后,系统可以跑到72M。时钟的配置过程或者是初始化过程(当用户不配置时,使用默认外接8M晶振的配置)大体是这样的:

备注: 启动文件:

startup_stm32f10x_cl.s 互联型的器件,STM32F105xx,STM32F107xx

startup_stm32f10x_hd.s 大容量的STM32F101xx,STM32F102xx,STM32F103xx

startup_stm32f10x_hd_vl.s 大容量的STM32F100xx

startup_stm32f10x_ld.s 小容量的STM32F101xx,STM32F102xx,STM32F103xx

startup_stm32f10x_ld_vl.s 小容量的STM32F100xx

startup_stm32f10x_md.s 中容量的STM32F101xx,STM32F102xx,STM32F103xx

startup_stm32f10x_md_vl.s 中容量的STM32F100xx

startup_stm32f10x_xl.s FLASH在512K到1024K字节的STM32F101xx,STM32F102xx,STM32F103xx

产品分类:

- Low-density Value line devices are STM32F100xx microcontrollers where the

Flash memory density ranges between 16 and 32 Kbytes.

- Low-density devices are STM32F101xx, STM32F102xx and STM32F103xx

microcontrollers where the Flash memory density ranges between 16 and 32 Kbytes.

- Medium-density Value line devices are STM32F100xx microcontrollers where

the Flash memory density ranges between 64 and 128 Kbytes.

- Medium-density devices are STM32F101xx, STM32F102xx and STM32F103xx

microcontrollers where the Flash memory density ranges between 64 and 128 Kbytes.

- High-density devices are STM32F101xx and STM32F103xx microcontrollers where

the Flash memory density ranges between 256 and 512 Kbytes.

- XL-density devices are STM32F101xx and STM32F103xx microcontrollers where

the Flash memory density ranges between 512 and 1024 Kbytes.

- Connectivity line devices are STM32F105xx and STM32F107xx microcontrollers.

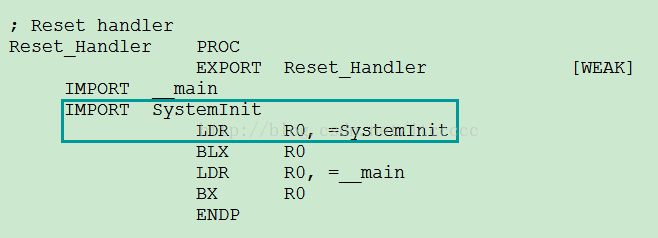

1、在STM32启动文件startup_stm32f10x_md.s的汇编代码中调用SystemInit()函数,而此函数是在system_stm32f10x.c文件中定义的;

注:如果用keil的启动文件,可能不会调用SystemInit()函数,需要自己在程序中调用。

startup_stm32f10x_md.s:

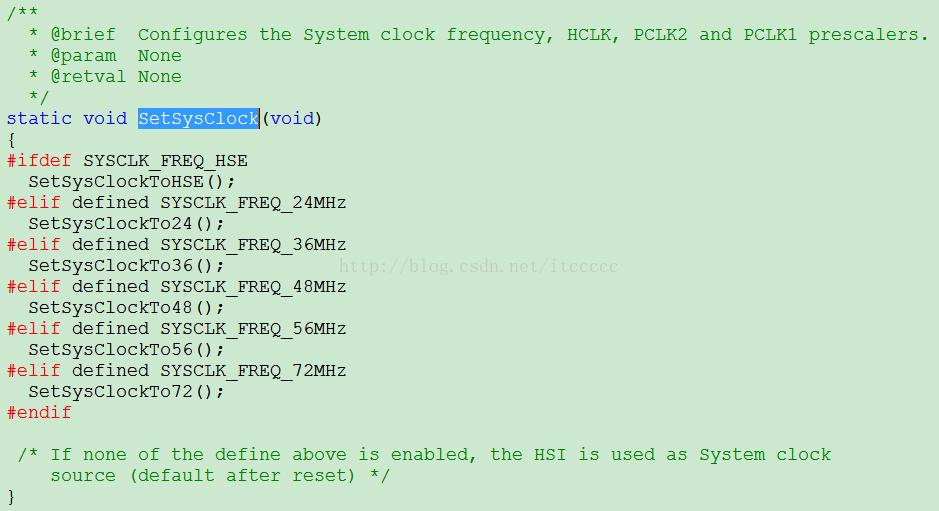

2、在SystemInit()函数中通过对相关寄存器的一系列配置后,调用了本文件(system_stm32f10x.c)中的SetSysClock()函数

system_stm32f10x.c:

/**

* @brief Setup the microcontroller system

* Initialize the Embedded Flash Interface, the PLL and update the

* SystemCoreClock variable.

* @note This function should be used only after reset.

* @param None

* @retval None

*/

void SystemInit (void)

{

//...省略一部分内容

#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)

#ifdef DATA_IN_ExtSRAM

SystemInit_ExtMemCtl();

#endif /* DATA_IN_ExtSRAM */

#endif

/* Configure the System clock frequency, HCLK, PCLK2 and PCLK1 prescalers */

/* Configure the Flash Latency cycles and enable prefetch buffer */

SetSysClock();

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM. */

#else

SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH. */

#endif

}SetSysClock:

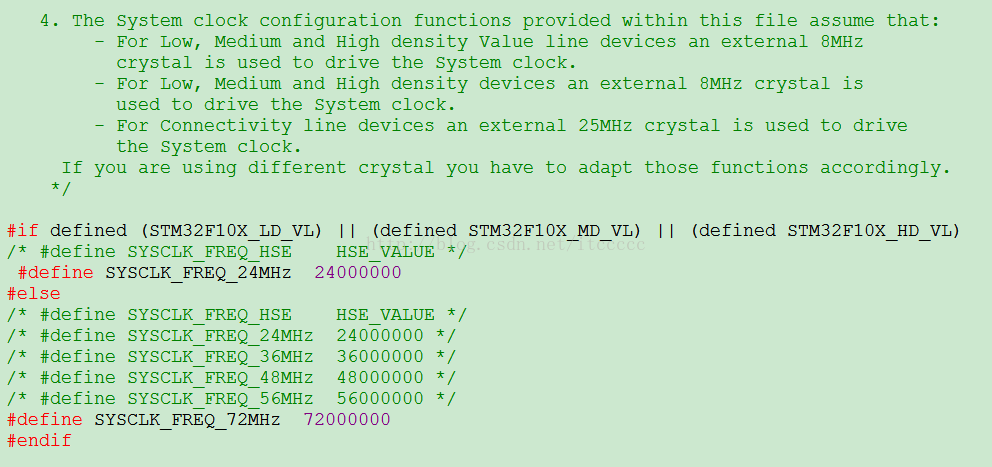

在此函数中通过判断之前定义过的宏,来决定调用设置系统不同时钟频率的函数,而这些宏是在此文件前面根据STM32不同的产品来定义的(对于低、中、高密度的产品使用外部8M晶振,对于互联型产品使用外部25M晶振),当然用户可以指定系统运行的速度24M、36M、48M、56M、72M,或自定义HSE_VALUE值,系统默认使用72M;

3、根据第2步所述,系统将在SetSysClock()函数中调用SetSysClockTo72()函数,在SetSysClockTo72()函数中通过一系列对相关寄存器的配置,来完成系统时钟的配置。SetSysClockTo72:

/**

* @brief Sets System clock frequency to 72MHz and configure HCLK, PCLK2

* and PCLK1 prescalers.

* @note This function should be used only after reset.

* @param None

* @retval None

*/

static void SetSysClockTo72(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/* Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/* Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

/* Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/* Flash 2 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

#ifdef STM32F10X_CL

/* Configure PLLs ------------------------------------------------------*/

/* PLL2 configuration: PLL2CLK = (HSE / 5) * 8 = 40 MHz */

/* PREDIV1 configuration: PREDIV1CLK = PLL2 / 5 = 8 MHz */

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV5);

/* Enable PLL2 */

RCC->CR |= RCC_CR_PLL2ON;

/* Wait till PLL2 is ready */

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

/* PLL configuration: PLLCLK = PREDIV1 * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL9);

#else

/* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

#endif /* STM32F10X_CL */

/* Enable PLL */

RCC->CR |= RCC_CR_PLLON;

/* Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{ /* If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

}

}备注: 启动文件:

startup_stm32f10x_cl.s 互联型的器件,STM32F105xx,STM32F107xx

startup_stm32f10x_hd.s 大容量的STM32F101xx,STM32F102xx,STM32F103xx

startup_stm32f10x_hd_vl.s 大容量的STM32F100xx

startup_stm32f10x_ld.s 小容量的STM32F101xx,STM32F102xx,STM32F103xx

startup_stm32f10x_ld_vl.s 小容量的STM32F100xx

startup_stm32f10x_md.s 中容量的STM32F101xx,STM32F102xx,STM32F103xx

startup_stm32f10x_md_vl.s 中容量的STM32F100xx

startup_stm32f10x_xl.s FLASH在512K到1024K字节的STM32F101xx,STM32F102xx,STM32F103xx

产品分类:

- Low-density Value line devices are STM32F100xx microcontrollers where the

Flash memory density ranges between 16 and 32 Kbytes.

- Low-density devices are STM32F101xx, STM32F102xx and STM32F103xx

microcontrollers where the Flash memory density ranges between 16 and 32 Kbytes.

- Medium-density Value line devices are STM32F100xx microcontrollers where

the Flash memory density ranges between 64 and 128 Kbytes.

- Medium-density devices are STM32F101xx, STM32F102xx and STM32F103xx

microcontrollers where the Flash memory density ranges between 64 and 128 Kbytes.

- High-density devices are STM32F101xx and STM32F103xx microcontrollers where

the Flash memory density ranges between 256 and 512 Kbytes.

- XL-density devices are STM32F101xx and STM32F103xx microcontrollers where

the Flash memory density ranges between 512 and 1024 Kbytes.

- Connectivity line devices are STM32F105xx and STM32F107xx microcontrollers.