S5PV210开发 -- Nand和e-MMC区别以及系统更新

如需转载请注明出处:https://blog.csdn.net/qq_29350001/article/details/78402135

通过上两篇文章我们完成了对开发板的烧写,接下来聊一下 Nand 和 iNand。为什么要聊这个呢?

我购买的开发板 Flash:支持512MB nand flash/4GB inand 可选,标配 4GB inand;它们除了结构上的不同,还跟系统更新有关啦,上两篇因为我的开发板是 iNand 所以一般用的是 fastboot 更新的。而 Nand 还可以通过 read、write、erase 指令进行更新。

前面有写过一篇 Nand 的文章,参看:S5PV210开发 -- nand 详解

一、iNand 详解

==============================================

个人思考:

下面介绍 iNand 部分的内容,我不知道出处是何处,我网上搜索到 iNand 相关的知识基本都是这些。

我有点懵逼了,iNand 是 Sandisk 公司符合 eMMC 协议的一种芯片系列名称。

可以查看 sandisk 闪迪官网

iNAND 嵌入式存储解决方案适用于 e.MMC 和 e.MCP 接口,可为智能手机、平板电脑和其他移动设备提供更快的系统响应能力、更出色的多任务处理性能,以及更长的电池寿命。高容量、高性能的 iNAND 嵌入式闪存驱动器是向终端用户提供领先的成像和应用性能的基础。

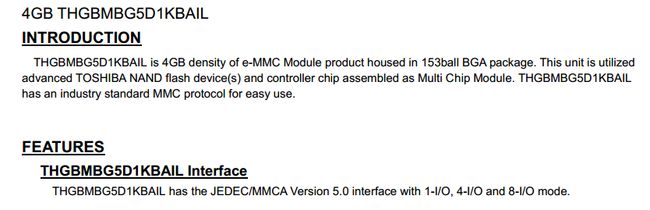

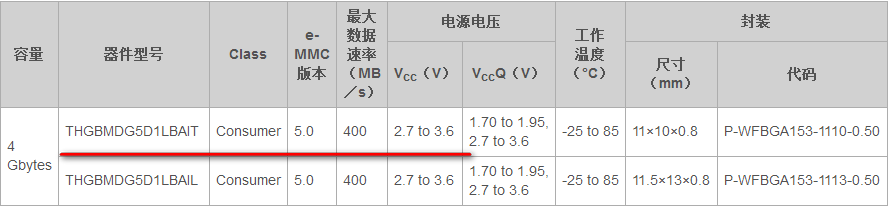

而我看了有下我买的开发板处 e-MMC 芯片型号是 THGBMBG5D1KBAIT

芯片手册下载:THGBMBG5D1KBAIL datasheet

可以查看 东芝官网

针对那些对大容量MLC NAND闪存感兴趣的用户,我们推荐封装内带有集成控制器芯片的NAND闪存产品。

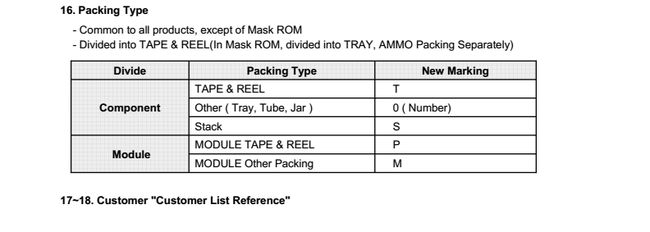

在使用不带集成控制器芯片的NAND存储器解决方案时,用户需要将坏块管理、错误代码校正(ECC)、逻辑-物理地址转换和磨损均衡(一种在存储器阵列内平均分布重写次数的技术)等处理操作嵌入存储系统中。

因此,我们推荐在同一个封装内加入集成控制器芯片的NAND闪存解决方案。

由于在技术规格和ECC要求上的变化,几乎每一代工艺的NAND闪存在操作方面都会随之发生相应的变化,特别是对MLC NAND闪存而言。东芝专门针对每一代NAND闪存开发的集成控制器芯片能够为这些必要操作提供解决方案。使用带有集成控制器芯片的NAND闪存解决方案,可以更轻松地构建主机内存应用系统。

东芝提供 e-MMC 和 UFS,这是集成控制器于同一封装的一系列大容量 NAND 闪存。

这些NAND解决方案提供了ECC和其它控制功能,这是东芝所优化的应用于每一代NAND的技术。

eMMC 和UFS 降低了主机处理器的工作量,简化了产品开发,缩短了上市时间,增加了存储器产品的易用性。

存储卡接口:e-MMC

e-MMC 是指一系列具有ECC、耗损均衡和坏块管理等控制功能的NAND闪存(NAND)。e-MMC 也提供符合JEDEC/MMCA版本 4.5/5.0/5.1的高速存储卡接口,从而消除了用户对于直接控制NAND的需求。所以,e-MMC 可轻松用作嵌入式多媒体卡(MMC)存储器。

UFS

东芝具有集成控制器的NAND闪存(NAND)能提供纠错、耗损均衡、坏块管理等功能。它们具有符合JEDEC/UFS版本2.1的接口,从而消除了用户对NAND特定控制的要求。这简化了闪存存储在嵌入式应用中的集成。

说这么多有啥用啊,其实我就想这些开发板用户手册上说,开发板是 nand flash 平台还是 inand 平台

这种说法是不是不太恰当呢?首先开发板上用的根本不是 iNand 系列的芯片。

Flash:支持512MB nand flash/4GB inand 可选,标配 4GB inand;

这句话也是错误的吧,4GB 的是东芝的 THGBMBG5D1KBAIT 型号的 e-MMC 芯片,所以说 e-MMC 会不会好些。

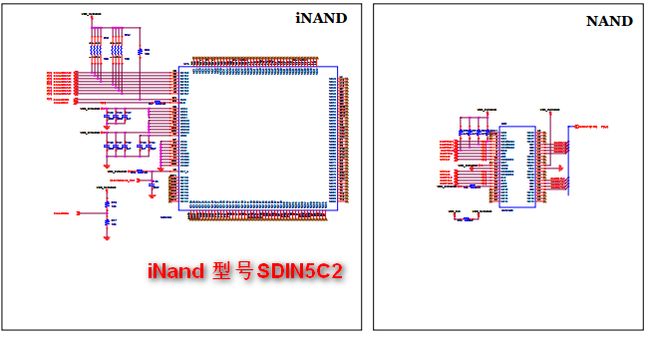

直到我看了官网提供的核心板原理图,才了解为什么它们说 iNand 了。

型号是 SDIN5C2 即 SanDisk 公司的 iNAND 支持 e-MMC 4 引导操作模式。

THGBMBG5D1KBAIT 和 SDIN5C2 封装是一样,是可替代的。

而上面所谓的 iNand 应该就是基于 SDIN5C2 来说的。

开发板手册上的叫法没有改回来,不过还是显得不太严谨。

原理图和相关芯片手册,下载:相关资料

最后需要谨记,下面介绍的 iNand 是 Sandisk 公司符合 eMMC 协议的一种芯片系列名称。

==============================================

我们先看看 iNand

参看:iNAND Technical Overview

参看:S5PV210系列 (裸机十五)之 iNand

(1)iNand 介绍

iNand/eMMC/SDCard/MMCCard的关联

(1)最早出现的是 MMC 卡,卡片式结构,按照 MMC 协议设计。(相较于NandFlash芯片来说,MMC卡 有 2 个优势:第一是卡片化,便于拆装;第二是统一了协议接口,兼容性好。)

(2)后来出现 SD卡,兼容 MMC 协议。SD卡 较 MMC 有一些改进,譬如写保护、速率、容量等。

(3)SD卡 遵守 SD 协议,有多个版本。多个版本之间向前兼容。

(4)iNand/eMMC 在 SD 卡的基础上发展起来,较 SD卡 的区别就是将 SD卡 芯片化了(解决卡的接触不良问题,便于设备迷你化)。

(5)iNand 和 eMMC 的关联:eMMC 是协议,iNand 是 Sandisk 公司符合 eMMC 协议的一种芯片系列名称。

iNand/eMMC的结构框图及其与NandFlash的区别

(1) iNand 内部也是由存储系统和接口电路构成(和 Nand 结构特性类似,不同之处在于接口电路功能不同)。

(2) iNand 的接口电路挺复杂,功能很健全。譬如:

第一,提供 eMMC 接口协议,和 SoC 的 eMMC 接口控制器通信对接。

第二,提供块的 ECC 校验相关的逻辑,也就是说 iNand 本身自己完成存储系统的 ECC 功能,SoC 使用 iNand 时自己不用写代码来进行 ECC 相关操作,大大简化了 SoC 的编程难度。( NandFlash 分 2 种:SLC 和 MLC,SLC 更稳定,但是容量小价格高;MLC 容易出错,但是容量大价格低)

第三,iNand 芯片内部使用 MLC Nand 颗粒,所以性价比很高。

第四,iNand 接口电路还提供了 cache 机制,所以 inand 的操作速度很快。

iNand / eMMC 的物理接口和 SD 卡物理接口的对比

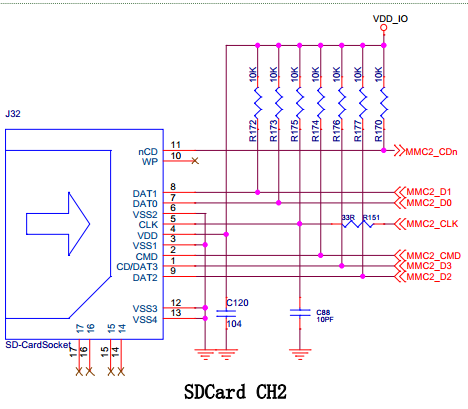

(1) S5PV210 芯片本身支持 4 通道的 SD/MMC,在 X210 中实际是在 SD/MMC0通道接了 iNand 芯片,而 SD/MMC2 接了 SD 卡( SD/MMC3 也接了 SD卡 )。

(2)对比 inand 和 SD卡 接线,发现:这两个接线几乎是一样的,唯一的区别就是SD卡 IO 线有 4 根,而 iNand 的 IO 线有 8 根。

(3)这个告诉我们,我们在实际操作 iNand芯片 时和操作 SD卡 时几乎是一样的(物理接线几乎一样,软件操作协议几乎一样)。

结论:

iNand / eMMC 其实就是芯片化的 SD/MMC 卡,软件操作和 SD 卡相同。

分析 iNand 芯片的操作代码时,其实就是以前的 SD卡 的操作代码。一些细节的区别就是为了区分各种不同版本的 SD卡、iNand 的细节差异。

(2)SD卡/iNand操作

这部分可以参看:SD卡物理层规范简化版 SD 卡部分这里只做了解,以后还会详讲的。

硬件接口:DATA、CLK、CMD

(1) iNand 的 IO 线有 8 根,支持 1、4、8 线并行传输模式;SD 卡 IO 线有 4 根,支持 1、4 线并行传输模式。

(2) CMD 线用来传输命令、CLK 线用来传输时钟信号。

(3)接口有 CLK 线,工作时主机 SoC 通过 CLK 线传输时钟信号给 SD卡/iNand 芯片,说明:SD/iNand 是同步的,SD/iNand 的工作速率是由主机给它的CLK频率决定的。

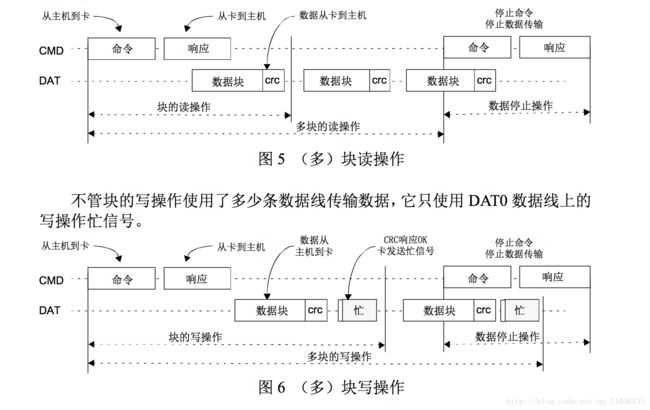

命令响应的操作模式

(1) SD 协议事先定义了很多标准命令(CMD0、CMD1·····),每个命令都有它的作用和使用条件和对应的响应。SD 卡工作的时候就是一个一个的命令周期组合起来的,在一个命令周期中,主机先发送 CMD 给 SD 卡,然后 SD卡 解析这个命令并且执行这个命令,然后 SD 卡根据结果回发给主机 SoC 一个响应。(有些命令是不需要响应的,这时 SD 卡不会给主机回发响应,主机也不用等待响应)。标准的命令+响应的周期中,主机发完一个命令后应该等待 SD卡 的响应而不是接着发下一条命令。

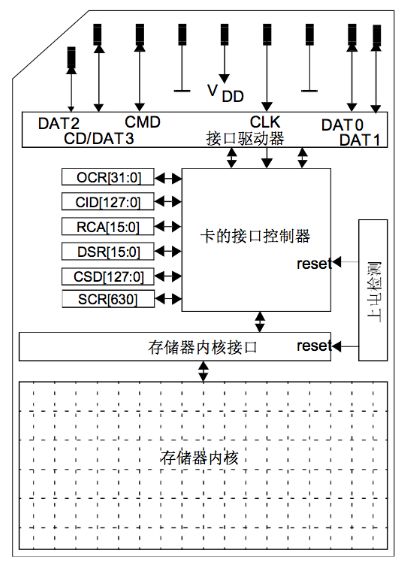

SD/iNand的体系结构图

(1) SD 卡内部有一个接口控制器,这个控制器类似于一个单片机,这个单片机的程序功能就是通过 CMD 线接收外部主机 SoC 发给 SD卡 的命令码,然后执行这个命令并且回发响应给主机 SoC。这个单片机处理命令及回发响应遵循的就是SD 协议。这个单片机同时可以控制 SD卡 内部的存储单元,可以读写存储单元。

SD / iNand 的寄存器(重点是 RCA 寄存器)

(1)注意这里说的是 SD卡 内部的寄存器,而不是主机 SoC 的 SD 控制器的寄存器。(很多外置芯片内部都是有寄存器的,这些寄存器可以按照一定的规则访问,访问这些寄存器可以得知芯片的一些信息)。

(2) RCA(relative address,相对地址寄存器)。我们在访问 SD卡 时,实际上 SD卡内部每个存储单元的地址没有绝对数字,都是使用相对地址。相对地址由 SD卡自己决定的,存放在 RCA 寄存器中。

SoC 的 SD/MMC/iNand 控制器简介

(1)不同的 SoC 可能在 SD/MMC/iNand 等支持方面有差异,但是如果支持都是通过内部提供 SD 控制器来支持的。

(2)S5PV210 的 SD卡 控制器在 Section8.7 部分

(2)SD/iNand代码实战分析

// SD协议规定的命令码

#define CMD0 0

#define CMD1 1

#define CMD2 2

#define CMD3 3

#define CMD6 6

#define CMD7 7

#define CMD8 8

#define CMD9 9

#define CMD13 13

#define CMD16 16

#define CMD17 17

#define CMD18 18

#define CMD23 23

#define CMD24 24

#define CMD25 25

#define CMD32 32

#define CMD33 33

#define CMD38 38

#define CMD41 41

#define CMD51 51

#define CMD55 55

// 卡类型

#define UNUSABLE 0

#define SD_V1 1

#define SD_V2 2

#define SD_HC 3

#define MMC 4

// 卡状态

#define CARD_IDLE 0 // 空闲态

#define CARD_READY 1 // 准备好

#define CARD_IDENT 2

#define CARD_STBY 3

#define CARD_TRAN 4

#define CARD_DATA 5

#define CARD_RCV 6

#define CARD_PRG 7 // 卡编程状态

#define CARD_DIS 8 // 断开连接

// 卡回复类型

#define CMD_RESP_NONE 0 // 无回复

#define CMD_RESP_R1 1

#define CMD_RESP_R2 2

#define CMD_RESP_R3 3

#define CMD_RESP_R4 4

#define CMD_RESP_R5 5

#define CMD_RESP_R6 6

#define CMD_RESP_R7 7

#define CMD_RESP_R1B 8命令码 CMD 和 ACMD

(1) SD卡 工作在命令 + 响应的模式下。

(2) SD协议 的命令分 2 种:CMDx 和 ACMDx。CMD 是单命令命令,就是单独发一个 CMD 即可表示一个意思。ACMD 是一种扩展,就是发 2 个 CMD 加起来表示一个意思。可以认为 ACMDx = CMDy + CMDz( y 一般是55)

卡类型识别 SD or MMC?

(1) MMC 协议、SD 协议、eMMC 协议本身是一脉相承的,所以造成了一定的兼容性,所以当我们 SoC 控制器工作时连接到 SoC 上的可能是一个 MMC 卡、也可能是 SD 卡、也可能是 iNand 芯片。主机 SoC 需要去识别这个卡到底是什么版本的卡

(2) SoC 如何区分卡种类?因为不同版本的卡内部协议不同的,所以对卡识别命令的响应也是不同的。SoC 通过发送一些命令、听取响应就可以根据不同的响应判定卡的版本。

卡状态

(1) SD卡 内部的接口控制器类似于一个单片机,这个单片机其实是一个状态机。所以 SD卡 任何时候都属于某一种状态(空闲状态、准备好状态、读写状态、出错状态····都是事先定义好的),在这种状态下能够接受的命令是一定的,接受到命令之后执行一定的操作然后根据操作结果会跳转为其他状态。如果主机发过来的命令和当前状态不符状态机就不响应,如果收到命令和当前状态相符就会执行相应操作,执行完之后根据结果跳转为其他状态。

卡回复类型

(1)一般来说,SD 卡的命令都属于:命令 + 响应的模式。也有极少数的 SD 卡命令是不需要回复的。

(2)卡回复有 R1、R7、R1B 等 8 种类型,每种卡回复类型都有自己的解析规则。然后卡在特定状态下响应特定命令时有可能回复哪种响应都是 SD 协议事先规定好的,详细细节要查阅协议文档。

linux内核风格的寄存器定义

(1)定义一个基地址,然后定义要访问的寄存器和基地址之间的偏移量,在最终访问寄存器时地址就等于基地址+偏移量。

(2)提供的代码中宏定义是不完整的,很多宏定义只能从字面意思来理解对应,无法通过语法完全获得

SD/iNand相关的GPIO初始化

#if (HSMMC_NUM == 0)

#define HSMMC_BASE (0xEB000000)

#elif (HSMMC_NUM == 1)

#define HSMMC_BASE (0xEB100000)

#elif (HSMMC_NUM == 2)

#define HSMMC_BASE (0xEB200000)

#elif (HSMMC_NUM == 3)

#define HSMMC_BASE (0xEB300000)

#else

#error "Configure HSMMC: HSMMC0 ~ HSMM3(0 ~ 3)"

#endifSD/iNand的时钟设置

(1)SD卡本身工作需要时钟,但是自己又没有时钟发生单元,依靠主机SoC的控制器通过SD接口中的CLK线传一个时钟过来给SD卡内部使用。所以主机SD卡控制器先初始化好自己的时钟,然后将自己的时钟传给SD卡。

(2)因为此时刚开始和SD卡通信,主机不清楚SD卡属于哪个版本(高版本和低版本的SD卡的读写速率不同,高版本的可以工作在低版本的速率下,低版本的SD卡不能工作在高版本速率下),所以先给SD卡发400KHz的低速率时钟,SD卡拿到这个时钟后就能工作了。然后在后面和SD卡进行进一步通信时去识别SD卡的版本号,识别后再根据SD卡的版本进一步给它更合适的时钟。

static void Hsmmc_ClockOn(uint8_t On)

{

uint32_t Timeout;

if (On) {

__REGw(HSMMC_BASE+CLKCON_OFFSET) |= (1<<2); // sd时钟使能

Timeout = 1000; // Wait max 10 ms

while (!(__REGw(HSMMC_BASE+CLKCON_OFFSET) & (1<<3))) {

// 等待SD输出时钟稳定

if (Timeout == 0) {

return;

}

Timeout--;

Delay_us(10);

}

} else {

__REGw(HSMMC_BASE+CLKCON_OFFSET) &= ~(1<<2); // sd时钟禁止

}

}

static void Hsmmc_SetClock(uint32_t Clock)

{

uint32_t Temp;

uint32_t Timeout;

uint32_t i;

Hsmmc_ClockOn(0); // 关闭时钟

Temp = __REG(HSMMC_BASE+CONTROL2_OFFSET);

// Set SCLK_MMC(48M) from SYSCON as a clock source

Temp = (Temp & (~(3<<4))) | (2<<4);

Temp |= (1u<<31) | (1u<<30) | (1<<8);

if (Clock <= 500000) {

Temp &= ~((1<<14) | (1<<15));

__REG(HSMMC_BASE+CONTROL3_OFFSET) = 0;

} else {

Temp |= ((1<<14) | (1<<15));

__REG(HSMMC_BASE+CONTROL3_OFFSET) = (1u<<31) | (1<<23);

}

__REG(HSMMC_BASE+CONTROL2_OFFSET) = Temp;

for (i=0; i<=8; i++) {

if (Clock >= (48000000/(1<(3)iNand的优点

1、提高性能

1)减少SOC的工作量,节约SOC资源。如果使用MLC做存储,SOC要参与FLASH的坏块管理、ECC校正等管理,会牺牲部分SOC性能,而使用iNAND的话,FLASH的管理工作都有iNAND完成,SOC只在需要时对iNAND进行读写,其他时候完全可以不需要理会iNAND。

2)读写速度快

(1)iNAND内置Cache模块,如果要存储小于4K的小容量文件时,Cache能够帮助用户将速度提高至MLC的10倍左右,并且Cache模块不需要用户控制,只要存储小容量文件,Cache自动启动,非常方便。

(2)iNAND可以将内置的MLC FLASH模拟成为为SLC,是iNAND具有SLC的读写速度及其他性能,从而提高读写速度。

3)产品更可靠稳定iNAND内置掉电保护、Wear leveling等SANDISK专利技术,可以帮助客户提高FLASH的读写寿 命,以及防止系统忽然掉电损坏系统文件,降低产品返修率。

2、降低系统成本

首先因为iNANDZ中选用的FLASH一般都是市场上最新、最先进制程的FLASH,所以iNAND具有一定的价格优势。

其次,iNAND不同容量的封装一致,客户如果某款机型有不同容量的几个型号,那么它PCB只需要做一套即可,可以帮助客户简化工作、提高效率,比如苹果iPHONE有8G、16G等容量产品,他的PCB只需要一套,生产时候贴上对用的iNAND即可。

3、方便采购

采购iNAND时候只需要注意使用的容量,不需要管制程、架构。而很多CPU对普通NAND FLASH不是完全兼容,假如某款CPU最多支持51nm制程的FLASH,如果FLASH厂家产品升级,该客户就可能遇到采购困难等问题,而且市场上也有三星、现代、美 光等公司的产品,他们都是完全遵照JEDEC委员会的标准,产品完全兼容。

4、使用简单,加快贵司产品研发进度

1)对软件工程师而言,FLASH制程改变,其对应驱动也需要随之变化,其程序移植、代码升级都要重新调试,而iNAND的产品驱动完全一样,一次调试成功就无后顾之忧;

2)对应硬件工程师也可能会因为新FLASH要重新布板,增加工作强度,而iNAND不管多大容量,封装都一样,如果贵司产品容量升级,可以直接在原先的PCB上换上更高容量的iNAND即可。

二、e-MMC

iNand 讲完了,用一句话概述。iNAND 是 SanDisk 公司研发的存储芯片,可以简单的看成SD卡或MMC卡芯片化。用户完全可以默认他是SD卡或者MMC卡。

接下来再看一下 e-MMC

参看:eMMC Flash Memory » What is eMMC?

(1)什么是 e-MMC

“e-MMC”是“embedded Multi-Media Card”的简称,即嵌入式多媒体存储卡。它是指集成在同一芯片上的闪存和闪存控制器。 eMMC解决方案至少包括三个组件--MMC(多媒体卡)接口,闪存和闪存控制器 - 并提供行业标准的BGA封装。

今天的嵌入式应用,如数码相机,智能手机和平板电脑几乎总是将其内容存储在闪存中。在过去,这需要一个专用的控制器来管理由应用程序CPU驱动的数据读写。然而,随着半导体技术发展到允许大大增加的存储密度,控制器从闪存芯片外部管理这些功能变得无效。因此,eMMC被开发为将控制器捆绑到闪存中的标准化方法。随着eMMC的改进,该标准还提供了安全擦除和修剪和高优先级中断等功能,以满足高性能和安全性的需求。因此,尽管eMMC标准是为了提高高密度芯片存储高分辨率视频的数据速率和吞吐量而创建的,但新一代在为更多的应用做更多的工作,每一代标准都将为更丰富的终端增添新的功能-用户体验。

eMMC广泛接受的标准是JEDD-A441:JEDEC于2011年6月出版的JESD84-A441:Embedded MultiMediaCard(e?MMC)产品标准v4.5中定义的v4.5。最近JEDEC还发布了JESD84-B45:嵌入式多媒体卡e-MMC),2011年6月eMMC v4.5的电气标准(4.5版)。但是最新的eMMC规范(5.1版)允许传输速率高达每秒400兆字节(MBps),这与使用SATA连接的固态驱动器相当。

这里提供几个标准协议一供参看,下载:eMMC 协议标准

eMMC在哪里使用?

eMMC适用于高性能应用,例如便携式消费类电子产品。智能手机,数字平板电脑,多媒体播放器,PDA,导航系统和数码相机。因此,eMMC可以用于移动设备,增强的存储解决方案以及作为传统存储介质(即,HDD)的替换。

eMMC的好处是什么?

将闪存控制器集成在同一封装中的eMMC体系结构简化了应用接口设计,并将主机处理器从低级闪存管理中解放出来。这通过简化非易失性存储器接口设计和资格认证流程,从而有利于产品开发人员,从而缩短上市时间,并有助于支持未来的闪存设备产品。

换句话说,eMMC内存在快速的“即插即用”包中隐藏了闪存技术的复杂性。显然,这减少了开发人员的时间和精力。

其次,eMMC通过将嵌入式控制器集成到存储器芯片中,为移动电话等设备的高速数据传输提供了易于使用的存储解决方案,从而无需开发所有类型NAND存储器的接口软件。它还通过垂直堆叠多个存储器功能来消除对存储器扩展槽的需要,导致存储器件的占用面积非常小。

此外,这种设计使得可以从更广泛的基础中选择子组件的供应商,从而增加收入,缩短产品上市时间。

eMMC所需的软件支持是什么?

eMMC v4.41标准提供性能,安全性和可靠性特性,如高优先级中断和安全擦除。这些功能(如安全擦除和安全修剪)需要来自文件系统的超出驱动程序的软件支持,否则应用程序调用将无法通过文件系统到达存储介质。任何计划迁移到eMMC的组织都需要从内部或外部渠道提供此类软件支持。

随着eMMC应用市场预计在2013年将扩大到超过7亿台,需要由Datalight制造的闪存驱动器和文件系统专门支持eMMC标准,以充分利用其提供的安全功能。

(2)e-MMC 和 其他 flash 比较

原始Flash与eMMC和UFS /什么是管理NAND

eMMC NAND和UFS内存都是“管理NAND”的好例子。这些大容量存储设备包含NAND闪存以及其他相关的控制器和接口电路。在下面的比较中,我们将在谈到非管理NAND时参考Raw Flash。

独立控制器

NOR和NAND闪存原本不需要单独的硬件闪存控制器,电路设计可以将此功能关闭到软件。硬件闪存控制器的主要特征之一是纠错和编码(ECC)。软件控制器解决方案只能合理地处理几个校正和检测,这远远低于较新的MLC NAND闪存所需的20位或更多位。 NAND闪存的新设计通常需要一个硬件闪存控制器。

系统设计师遇到的一个问题是将硬件闪存控制器功能与NAND闪存的要求相匹配。这个问题由于材料清单的更改而加剧 - 更新的闪存部件通常需要更多的ECC。这可能意味着对设计的更多更改,媒体接口例程的修改和增加的故障风险。

eMMC和UFS都包含一个内置的控制器模块,通过设计,它可以处理底层NAND的ECC要求。处理ECC策略的固件(多次重试,何时标记块不好等)内置于eMMC和UFS媒体;必须在软件层中提供原始闪存。

可能的性能影响的一个小问题是错误流量。使用单独的控制器,任何Flash媒体错误将通过较长的电路路径传输,并涉及主处理器的决策; eMMC和UFS都在内部使用专用处理器来处理。还有各种基于ONFI EZ-NAND规格的内置误差校正的原始闪存介质。品牌名称包括美光的ClearNAND和东芝的SmartNAND。在这些部件中,磨损均衡由外部软件解决方案提供。

构成因素

NOR和NAND闪存都可从各种制造商处获得。确切的形状因素和引脚排列变化很大,这可能给嵌入式系统设计人员带来第二个源头痛。目前的eMMC和UFS媒体设计有几种标准形式和所有供应商都可以使用。

一个额外的外形尺寸,具有更小的更坚固的针数,是工业eMMC。原始闪存中有一个等效的SPI NOR和NAND。这些较小的封装更容易设计成小型的电路板空间,并且放弃很少甚至没有性能。

特征集

原始闪存通常具有供应商特定的功能集,以及常见的接口例程。供应商特定的命令通常为设计人员提供额外的性能或特殊功能,其代价是限制第二来源。

eMMC和UFS的访问例程通过一个通用的命令接口进行标准化,因此基本的驱动程序可以读取,写入和擦除该部件。像raw flash一样,供应商有大量可选的Jedec规范功能来实现,并且依靠这个实现也可以限制第二个源列表。此外,固件性能未指定,供应商各不相同。

(3)有哪些品牌的 e-MMC

(4)UFS与eMMC比较

华为闪存门事件,正好可以为我们提供一下 eMMC 和 UFS 的比较。

参看:华为说eMMC与UFS差不多?我们实测一下

参看:UFS与eMMC性能差距到底有多大?

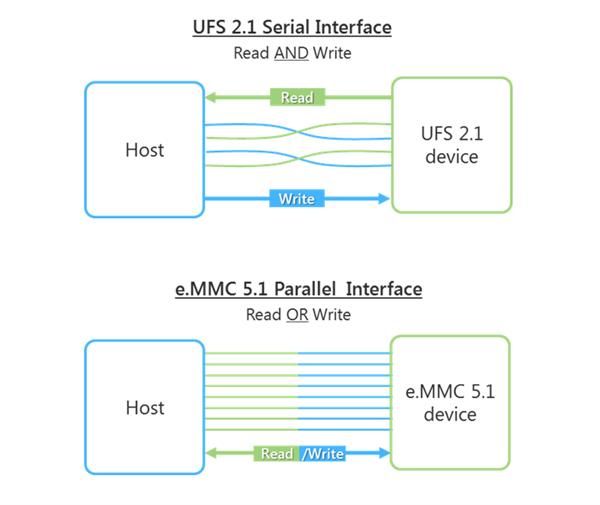

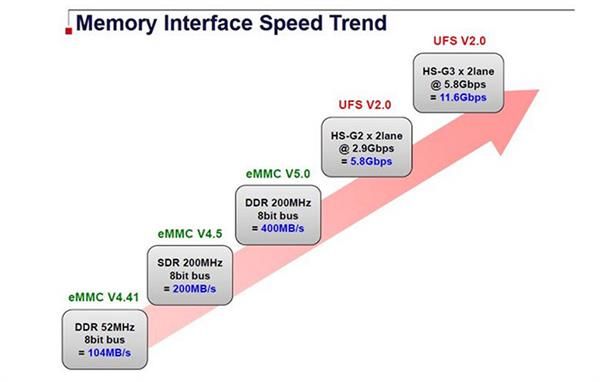

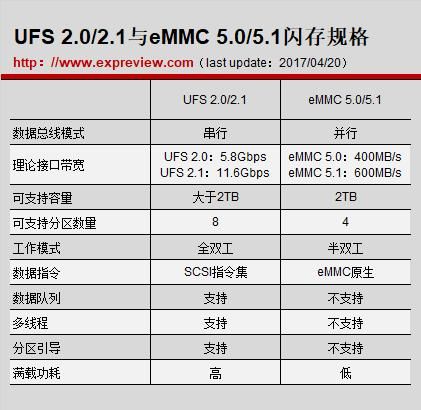

eMMC全称是embedded Multi Media Card,中文翻译为“嵌入式多媒体存储卡”,采用并行数据传输技术,主控和存储单元之间拥有8个数据通道,它们可以同步工作,工作模式为半双工,每个通道允许读写传输,但是同一时间只能读/写。

UFS全称是Universal Flash Storage,中文翻译为“通用闪存存储”,采用串行数据传输技术,只有两个数据通道但速率超越eMMC,工作模式为全双工模式,同一条通道允许读写传输,而且读写能够同时进行,传输效率效率提高。不论是数据传输技术,还是工作模式,UFS都全面领先于eMMC。

下面用几张图来说明:

(5)了解更多

想了解更多的话参看下面的链接,这里就不多讲了。

参看:NAND and eMMC: All You Need to Know About Flash Memory

参看:eMMC (embedded MultiMediaCard)

参看:EMMC 介绍

三、nand flash

这部分网上也是内容也是大同小异。

参看:NandFlash和iNand

参看:NandFlash和iNand

参看:S5PV210系列 (裸机十四)之 NandFlash

做了三分钟思考,这些内容是复制粘贴呢,还是复制粘贴呢,就复制粘贴吧。O(∩_∩)O哈哈~

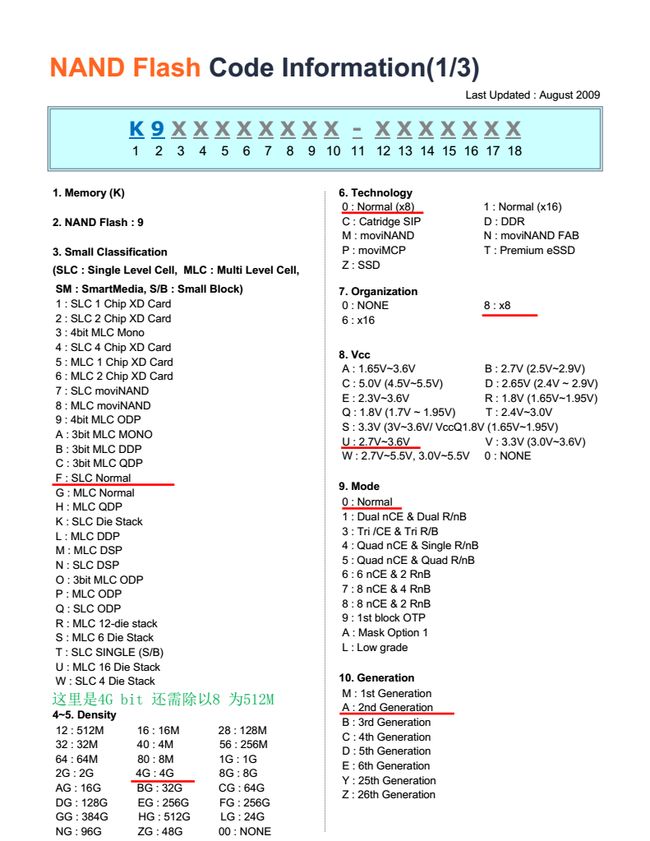

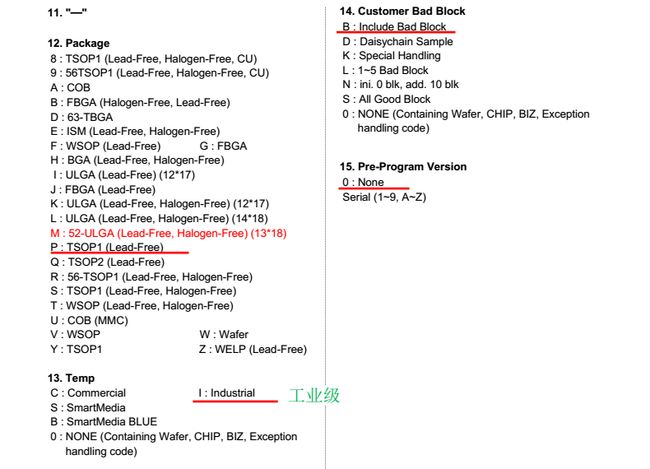

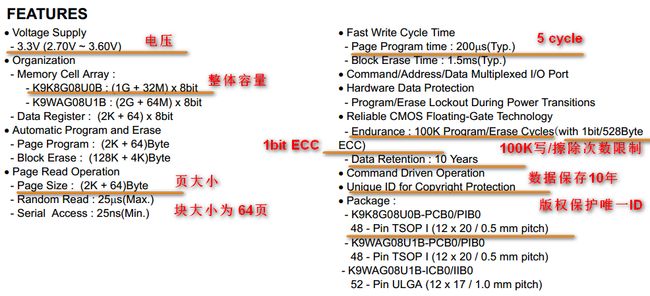

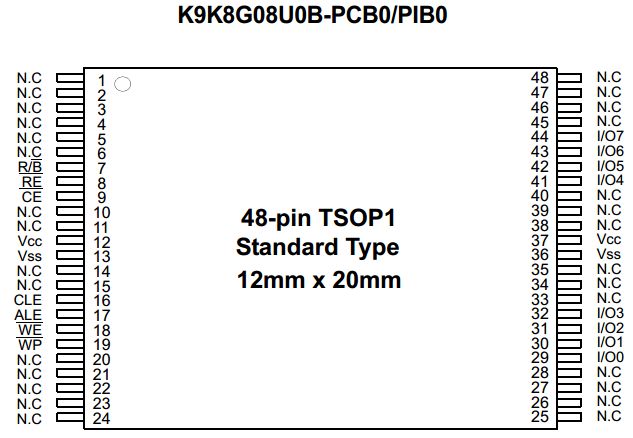

(1)nand 型号和命名

这里重点讲的是三星闪存命名规则、容量、类型。举个例子,采用的 Nand 型号为 K9K8G08U0B-PIB0

参看:三星Nand-Flash命名规则

上面我们只是从命名规则上分析了一下 K9K8G08U0B-PIB0 芯片,接下来要它的芯片手册上怎么说的。

参看:K9K8G08U0B datasheet

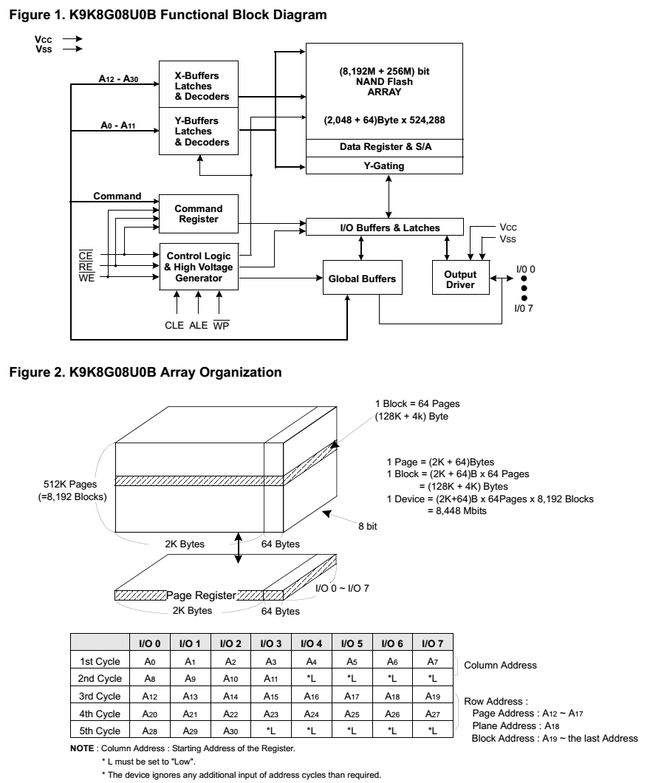

(2)nand 功能框图

(3)NandFlash 的结构

Nand 的单元组织:block 与 page( 大页 Nand 与小页 Nand )

(1) Nand 的页和以前讲过的块设备(尤其是硬盘)的扇区是类似的。扇区最早在磁盘中是 512 字节,后来也有些高级硬盘扇区不是 512 字节而是 1024 字节/ 2048 字节/4096字节等。Nand也是一样,不同的Nand的页的大小是不同的,也有512字节/1024字节/2048字节/4096字节等。

(2)一个block等于多少page也是不定的,不同的Nand也不同。一个Nand芯片有多少block也是不定的,不同的Nand芯片也不同。

总结:Nand的组织架构挺乱的,接口时序也不同,造成结构就是不同厂家的Nand芯片,或者是同一个厂家的不同系列型号存储容量的nand接口也不一样。所以nand有一个很大的问题就是一旦升级容量或者换芯片系列则硬件要重新做、软件要重新移植。

带内数据和带外数据(ECC与坏块标记)

(1)Nand的每个页由2部分组成,这2部分各自都有一定的存储空间。譬如K9F2G08中为2K+64字节。其中的2K字节属于带内数据,是我们真正的存储空间,将来存储在Nand中的有效数据就是存在这2K范围内的(我们平时计算nand的容量时也是只考虑这2KB);64字节的带外数据不能用来存储有效数据,是作为别的附加用途的(譬如用来存储ECC数据、用来存储坏块标志等····)

(2)什么是ECC:(error correction code,错误校验码)。因为nand存储本身出错(位反转)概率高(Nand较Nor最大的缺点就是稳定性),所以当我们将有效信息存储到Nand中时都会同时按照一定算法计算一个ECC信息(譬如CRC16等校验算法),将ECC信息同时存储到Nand这个页的带外数据区。然后等将来读取数据时,对数据用同样的算法再计算一次ECC,并且和从带外数据区读出的ECC进行校验。如果校验通过则证明Nand的有效数据可信,如果校验不通过则证明这个数据已经被损坏(只能丢弃或者尝试修复)。

(3)坏块标志:Nand芯片用一段时间后,可能某些块会坏掉(这些块无法擦除了,或者无法读写了),nand的坏块非常类似于硬盘的坏道。坏块是不可避免的,而且随着Nand的使用坏块会越来越多。当坏块还不算太多时这个Nand都是可以用的,除非坏块太多了不划算使用了才会换新的。所以我们为了管理Nand发明了一种坏块标志机制。Nand的每个页的64字节的带外数据中,我们(一般是文件系统)定义一个固定位置(譬如定位第24字节)来标记这个块是好的还是坏的。文件系统在发现这个块已经坏了没法用了时会将这个块标记为坏块,以后访问nand时直接跳过这个块即可。

Nand 的地址时序

(1) nand 的地址有多位,分 4/5 周期通过 IO 引脚发送给 Nand 芯片来对 Nand 进行寻址。寻址的最小单位是字节,但是读写的最小单位是页。

(2) nand 的地址在写代码时要按照 Nand 要求的时序和顺序去依次写入。

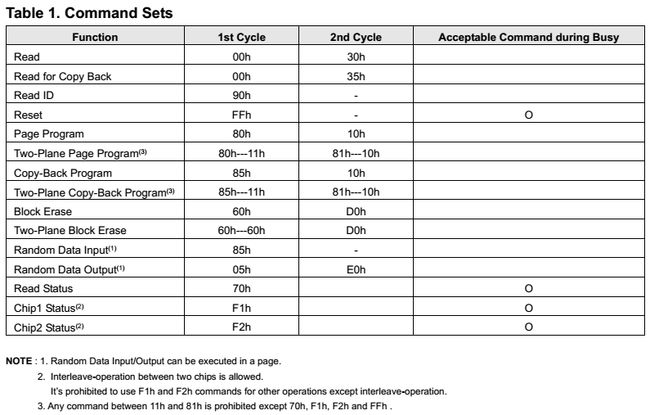

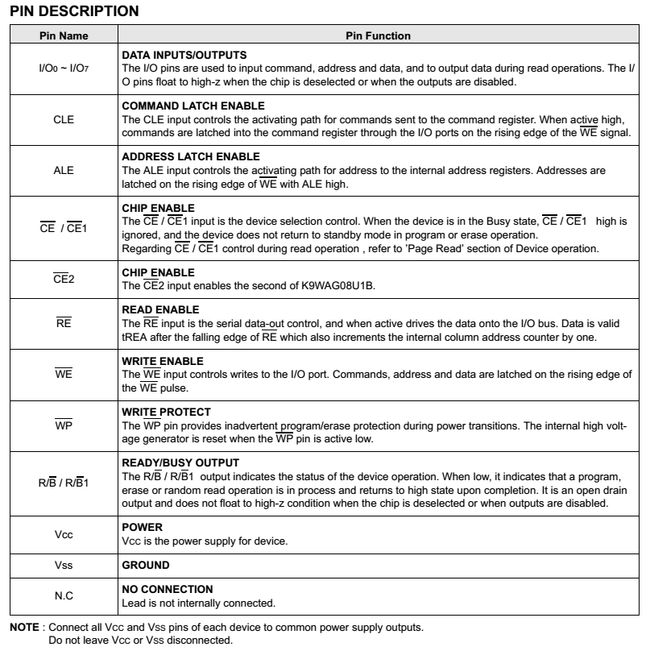

Nand 的命令码

(1)外部 SoC 要想通过 Nand 控制器来访问 Nand(实质就是通过 Nand 接口),就必须按照 Nand 接口给 nand 发送命令、地址、数据等信息来读写 Nand。

(2) Nand 芯片内部的管理电路本身可以接收外部发送的命令,然后根据这些命令来读写 Nand 内容与外部 SoC 交互。所以我们对 nand 进行的所有操作(擦除、读、写···)都要有命令、地址、数据的参与才能完成,而且必须按照 Nand 芯片规定的流程来做。

(3)NandFlash 的常见操作及流程分析

坏块检查

(1) Flash 使用之前要先统一擦除(擦除的单位是块)。Flash 类设备擦除后里面全是 1,所以擦干净之后读出来的值是 0xff。

(2)检查坏块的思路就是:先块擦除,然后将整块读出来,依次检测各自节是否为0xff,如果是则表明不是坏块,如果不是则表明是坏块。

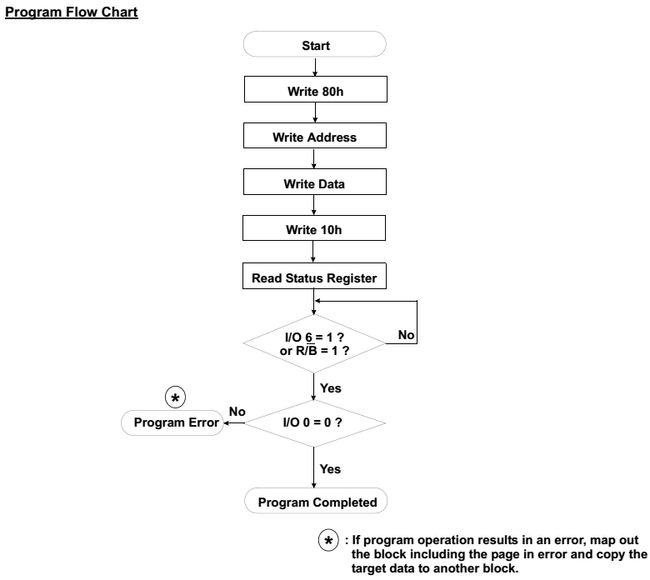

页写(program)操作

(1)写之前确保这个页是被擦除干净的。如果不是擦除干净的(而是脏的、用过的)页,写进去的值就是错的,不是你想要的结果。

(2)写操作(write)在 flash 的操作中就叫编程( program )

(3) SoC 写 Flash 时通过命令线、IO 线依次发送写命令、写页地址、写数据等进入 NandFlash。

(4)写的过程:SOC 通过 Nand 控制器和 Nand 芯片完成顺序对接,然后按照时序要求将一页数据发给 Nand 芯片内部的接口电路。接口电路先接收收据到自己的缓冲区,然后再集中写入 Nand 芯片的存储区域中。Nand 接口电路将一页数据从缓冲区中写入 Nand 存储系统中需要一定的时间,这段时间 Nand 芯片不能再响应 SOC 发过来的其他命令,所以 SoC 要等待 Nnad 接口电路忙完。等待方法是SoC 不断读取状态寄存器(这个状态寄存器有2种情况:一种是SoC的Nand控制器自带的,另一种是SoC通过发命令得到命令响应得到的),然后通过检查这个状态寄存器的状态位就能知道Nand接口电路刚才写的那一页数据写完了没、写好了没。直到SoC收到正确的状态寄存器响应才能认为刚才要写的那一页数据已经ok。(如果SoC收到的状态一直不对,可以考虑重写或者认为这一页所在的块已经是坏块,或者整个 Nand 芯片已经挂掉了)。

(5)正常情况下到了第四步就已经完了。但是因为Nand的读写有不靠谱情况,因此我们为了安全会去做ECC校验。ECC校验有硬件式校验和软件式校验2种。软件式校验可以采用的策略有很多,其中之一(Nand芯片手册上推荐的方式是):将刚才写入的1页数据读出来,和写入的内容进行逐一对比。如果读出的和写入的完全一样,说明刚才的写入过程正确完成了;如果读出来的和写入的不完全一样那就说明刚才的写入有问题。

(6)硬件式ECC:SoC的Nand控制器可以提供硬件式ECC(这个也是比较普遍的情况)。硬件式ECC就是在Nand的控制器中有个硬件模块专门做ECC操作。当我们操作Nand芯片时,只要按照SoC的要求按时打开ECC生成开关,则当我们写入Nand芯片时SoC的Nand控制器的ECC模块会自动生成ECC数据放在相应的寄存器中,然后我们只需要将这生成的ECC数据写入Nand芯片的带外数据区即可;在将来读取这块Nand芯片时,同样要打开硬件ECC开关,然后开始读,在读的过程当中硬件ECC会自动计算读进来的一页数据的ECC值并将之放到相应的寄存器中。然后我们再读取带外数据区中原来写入时存入的ECC值,和我们刚才读的时候得到的ECC值进行校验。校验通过则说明读写正确,校验不通过则说明不正确(放弃数据或者尝试修复)。

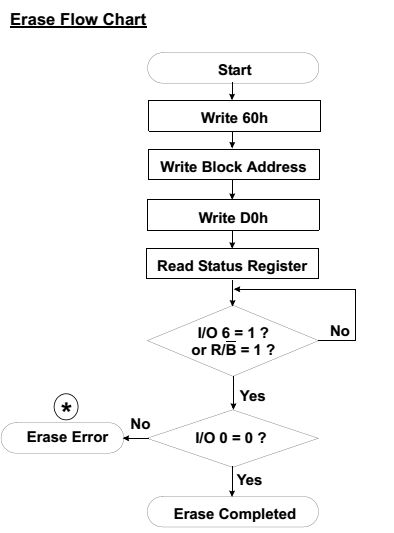

擦除(erase)操作

(1)擦除时必须给块对齐的地址。如果给了不对齐的地址,结果是不可知的(有些Nand芯片没关系,它内部会自动将其对齐,而有些Nand会返回地址错误)。

(2)读写时给的地址也是一样,要求是页对齐地址。如果给了不对齐的,也是有可能对有可能错。

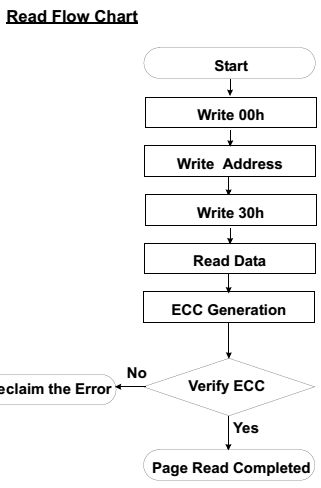

页读(read)操作

四、系统更新

培训的时候一般都是用的 nand flash,所以烧写的时候会用到 上面刚讲的那几个指令。

这部分 Hi3516a 烧写,其实讲的已经很清楚了。参看:Hi3516A开发--板卡烧写 流程是一样的。

那我们来看看 S5PV210 怎么更新。

(1)查看一下都有哪些 uboot 指令

这个很尴尬了,手头没有nand flash的 uboot。只能看我inand的...

进入uboot,执行 help

x210 # help

? - alias for 'help'

autoscr - run script from memory

base - print or set address offset

bdinfo - print Board Info structure

boot - boot default, i.e., run 'bootcmd'

bootd - boot default, i.e., run 'bootcmd'

bootelf - Boot from an ELF image in memory

bootm - boot application image from memory

bootp - boot image via network using BootP/TFTP protocol

bootvx - Boot vxWorks from an ELF image

cmp - memory compare

coninfo - print console devices and information

cp - memory copy

crc32 - checksum calculation

dcache - enable or disable data cache

dhcp - invoke DHCP client to obtain IP/boot params

dnw - initialize USB device and ready to receive for Windows server (specific)

echo - echo args to console

erase - erase FLASH memory

exit - exit script

ext2format - disk format by ext2

ext2load- load binary file from a Ext2 filesystem

ext2ls - list files in a directory (default /)

ext3format - disk format by ext3

fastboot- use USB Fastboot protocol

fatformat - disk format by FAT32

fatinfo - print information about filesystem

fatload - load binary file from a dos filesystem

fatls - list files in a directory (default /)

fdisk - fdisk for sd/mmc.

flinfo - print FLASH memory information

go - start application at address 'addr'

help - print online help

icache - enable or disable instruction cache

iminfo - print header information for application image

imls - list all images found in flash

imxtract- extract a part of a multi-image

itest - return true/false on integer compare

loadb - load binary file over serial line (kermit mode)

loads - load S-Record file over serial line

loady - load binary file over serial line (ymodem mode)

loop - infinite loop on address range

md - memory display

mm - memory modify (auto-incrementing)

MMC sub systemprint MMC informationmovi - sd/mmc r/w sub system for SMDK board

mtest - simple RAM test

mw - memory write (fill)

nfs - boot image via network using NFS protocol

nm - memory modify (constant address)

ping - send ICMP ECHO_REQUEST to network host

printenv- print environment variables

protect - enable or disable FLASH write protection

rarpboot- boot image via network using RARP/TFTP protocol

reset - Perform RESET of the CPU

reginfo - print register information

reset - Perform RESET of the CPU

run - run commands in an environment variable

saveenv - save environment variables to persistent storage

sdfuse - read images from FAT partition of SD card and write them to booting device.

setenv - set environment variables

sleep - delay execution for some time

test - minimal test like /bin/sh

tftpboot- boot image via network using TFTP protocol

version - print monitor version如此可以看到 nand 和 erase 等指令。

详细查看各个指令用法可使用 help+指令名 来查看。举个栗子:

x210 # help erase

erase start end

- erase FLASH from addr 'start' to addr 'end'

erase start +len

- erase FLASH from addr 'start' to the end of sect w/addr 'start'+'len'-1

erase N:SF[-SL]

- erase sectors SF-SL in FLASH bank # N

erase bank N

- erase FLASH bank # N

erase all

看到 loady 我想起来,还可以通过串口烧写这个之前讲过,参看:Hi3516A开发-- 板卡串口烧写

(2)执行 print 查看配置信息

x210 # print

bootargs=console=ttySAC2,115200 root=/dev/mmcblk0p2 rw init=/linuxrc rootfstype=ext3

bootcmd=movi read kernel 30008000; movi read rootfs 30B00000 300000; bootm 30008000 30B00000

mtdpart=80000 400000 3000000

bootdelay=3

baudrate=115200

ethaddr=00:40:5c:26:0a:5b

ipaddr=192.168.1.88

serverip=192.168.1.102

gatewayip=192.168.0.1

netmask=255.255.0.0

Environment size: 346/16380 bytes

然后设置serverip(即tftp服务器的ip)、ipaddr(单板ip)和ethaddr(单板的MAC地址)。使其与主机在同一网段且不与其他设备冲突即可。

setenv serverip xx.xx.xx.xx

setenv ipaddr xx.xx.xx.xx

setenv ethaddr xx:xx:xx:xx:xx:xx

setenv netmask xx.xx.xx.xx

setenv gatewayip xx.xx.xx.xx

save

设置启动参数,这个也讲过,参看:DM368开发 -- uboot 使用 讲的够详细的了,这里不重复了。

(3)更新

这里用到 tftp 了,还是讲过。参看:Hi3516A开发--环境搭建工具 推荐使用Windows下的tftpd32。

更新 uboot

u-boot.bin烧写nand 0~2M

tftp 20008000 u-boot.bin

nand erase 0 200000

nand write 20008000 0 200000

更新内核

烧写kernel到nand 5M~10M

tftp 20008000 zImage.bin

nand erase 500000 500000

nand write 20008000 500000 500000

更新根文件系统

烧写根文件系统:rootfs_android2.3_v1.0_20120725.bin(111M)

tftp 40008000 rootfs_android2.3_v1.0_20120725.bin

nand erase a00000

nand write.yaffs 40008000 a00000 0x6fa38c0

由于Nand Flash的物理特性决定,要向Nand Flash中写数据之前,必须先擦除。

这部分其实应该在系统移植部分再讲的。这里留一个疑问这里的 200800 是什么地址,这个下一篇文章再讲。

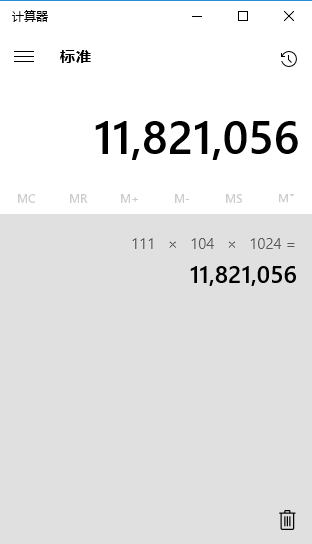

再有这里的烧写位置的计算,比如这个 nand write.yaffs 40008000 a00000 0x6fa38c0

首先你要知道这句话是啥意思:

将DDR地址为0x40008000 上的数据写入到nandflash 地址0xa00000上,写入长度为0x6fa38c0

注意:这里容易搞混的就是最后一个 是写入长度,即文件大小。而不是从0xa00000 再加 111M 的地址。

然后是进制转换问题了,参看:Hi3516A开发--内存换算

比如 111M 转换成十六进制是什么:

考虑到数据的对齐补齐,有时会多预留一些空间的。

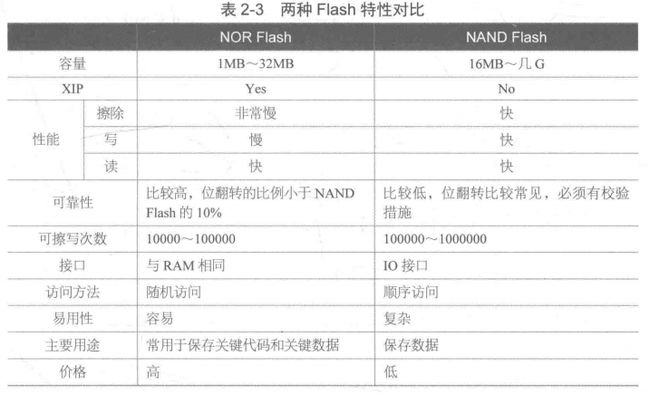

五、NOR flash 和 Nand flash 比较

NOR Flash 和 Nand Flash 是现在市场上两种主要的非易失闪存技术。Inter 公司于 1988 年首先开发出 NOR Flash 技术;1989 年,东芝公司开发出 Nand Flash 技术。

Nand Flash 和 NOR Flash 的主要区别:

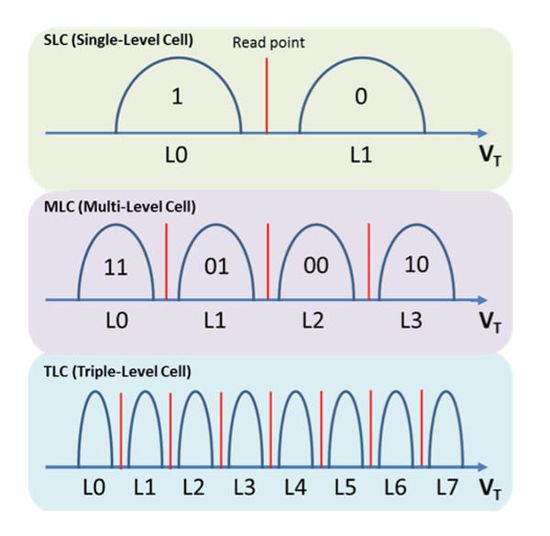

六、SLC、MLC、TLC 比较

参看:为啥一直都被骂 TLC闪存到底是啥?

参看:苹果新品?到底iPhone6S会用TLC还是MLC

参看:NAND and eMMC: All You Need to Know About Flash Memory

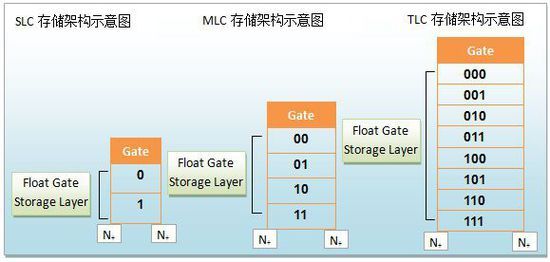

NAND闪存的类型有SLC、MLC和TLC这三种,SLC不论性能还是可靠性都是都是最好的,但成本也是最高的;MLC闪存性能、可靠性次之,它的性能、可靠性与成本上是相当均衡的,是目前的绝对主力;TLC则是在2012年之后三星才把它带入SSD市场的,之前主要是用在U盘以及存储卡上面,在三星先行了两年之后今年其他厂商终于跟上了,大量的TLC SSD开始推向市场。

SLC = Single-Level Cell,即1 bit per cell,只存在0和1两个充电值,结构简单但是执行效率高。SLC闪存的优点是传输速度更快,功率消耗更低和存储单元的寿命更长。然而,由于每个存储单元包含的信息较少,其每百万字节需花费较高的成本来生产,由于成本过高你基本上只会在高端的企业级SSD上见到它,流入到消费级平台上的基本都是非原封的。

MLC = Multi-Level Cell,即2 bit per cell,有00,01,10,11四个充电值,因此需要比SLC更多的访问时间,不过每个单元可以存放比SLC多一倍的数据。MLC闪存可降低生产成本,但与SLC相比其传输速度较慢,现在大多数消费级SSD都是使用MLC做的。

TLC = Trinary-Level Cell,即3 bit per cell,每个单元可以存放比MLC多1/2的数据,共八个充电值,所需访问时间更长,因此传输速度更慢。TLC优势价格便宜,每百万字节生产成本是最低的,但是寿命短,通常用在U盘或者存储卡这类移动存储设备上。

三者比较:

从结果上来看,各种闪存的物理结构是相同的,但是控制上一个比一个复杂,SLC每个Cell能储存1个数据,有两种电位变化,MLC每个Cell能储存2个数据,有四种电位变化,TLC每个Cell可以储存3个数据,有8种电位变化,MLC和TLC每个Cell单元中有多个信号,是通过控制不同的电压来实现的,施加不同的电压就会有更多的电位变化,NAND闪存单元就可以容纳不同的信号组合。

简单地说SLC的性能最优,价格超高。一般用作企业级或高端发烧友。MLC性能够用,价格适中为消费级SSD应用主流,TLC综合性能最低,价格最便宜。但可以通过高性能主控、主控算法来弥补、提高TLC闪存的性能。

七、继续阅读芯片手册

打开 K9K8G08 芯片手册,查看引脚封装排序和引脚说明。

八、总结

这篇文章写的东西有点多了,而且跟题目好像也不搭,哈哈。就这我还是挑着写的,很多东西没有讲的太细。

其中 nand 部分好多内容还没有讲。比如 nand 的控制寄存器、时序控制等。以后会从新开一篇文章再讲的。

如需转载请注明出处:https://blog.csdn.net/qq_29350001/article/details/78402135

![]()