(转)晶振负载电容外匹配电容计算与晶振振荡电路设计经验总结

|本文转自:晶振负载电容外匹配电容计算与晶振振荡电路设计经验总结 - 竹夭的日志 单片机论坛 http://www.51hei.com/bbs/blog-191639-10272.html

对应MCU、ROMan">WiFi或USB HUB一般需外部提供时钟信号,需要外挂一颗晶振,常有客户问到,如何结合晶振的负载电容计算外匹配电容容值以及在晶振振荡电路设计时需注意哪些事项,所以小编对此做一个归纳总结,如有不正确之处,欢迎指正。

(1)晶振负载电容定义

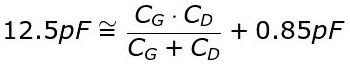

晶体元件的负载电容是指在电路中跨接晶体两端的总的外界有效电容,是晶振要正常震荡所需要的电容。如果从石英晶体插脚两端向振荡电路方向看进去的全部有效电容为该振荡电路加给石英晶体的负载电容。石英晶体的负载电容的定义如下式:

其中:

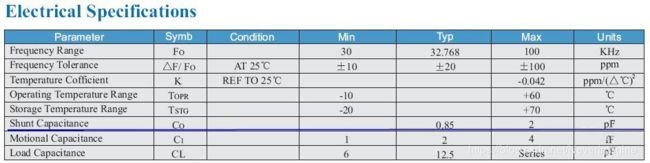

CS为晶体两个管脚之间的寄生电容(又名晶振静态电容或Shunt Capacitance),在晶体的规格书上可以找到具体值,一般0.2pF~8pF不等。如图1是某32.768KHz的电气参数,其寄生电容典型值是0.85pF(在表格中采用的是Co)。

图1、某晶体的电气参数

CG指的是晶体振荡电路输入管脚到GND的总电容,其容值为以下三个部分的和。

● 需加外晶振主芯片管脚芯到GND的寄生电容 Ci

● 晶体震荡电路PCB走线到到GND的寄生电容CPCB

● 电路上外增加的并联到GND的外匹配电容 CL1

CD指的是晶体振荡电路输出管脚到GND的总电容。容值为以下三个部分的和。

● 需加外晶振主芯片管脚芯到GND的寄生电容, Co

● 晶体震荡电路PCB走线到到gnd的寄生电容,CPCB

● 电路上外增加的并联到GND的外匹配电容, CL2

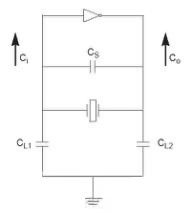

图2中标示出了CG,CD,CS的的组成部分。

图2、晶体振荡电路的概要组成

(2)晶体负载电容和频偏之间的关系

负载电容(load capacitance)主要影响负载谐振频率和等效负载谐振电阻,它与石英谐振器一起决定振荡器的工作频率,通过调整负载电容,一般可以将振荡器的工作频率调到标称值。应用时我们一般外接电容,便是为了使晶振两端的等效电容等于或接近负载电容,对于要求高的场合还要考虑ic输入端的对地电容,这样便可以使得晶振工作的频率达到标称频率。

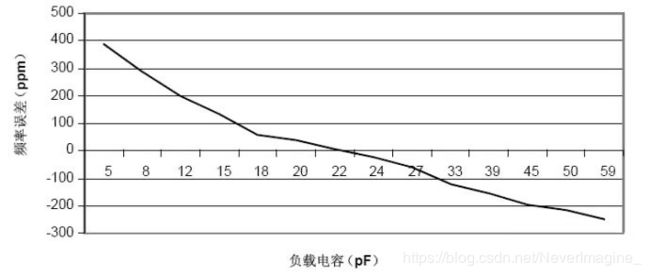

负载电容常用的标准值有12.5 pF,16 pF,20 pF,30pF,负载电容和谐振频率之间的关系不是线性的,负载电容变小时,频率偏差量变大;负载电容提高时,频率偏差减小。图3是一个晶体的负载电容和频率的误差的关系图。

图3、晶振误差— 负载电容(22 pF 负载电容)

(3)晶振负载电容外匹配电容CL1及CL2计算

如图3所示,如果晶振两端的等效电容与晶振标称的负载电容存在差异时,晶振输出的谐振频率将与标称工作的工作频率产生一定偏差(又称之为频偏),所以合理匹配合适的外加电容使晶振两端的等效电容等于或接近负载电容显得十分重要。

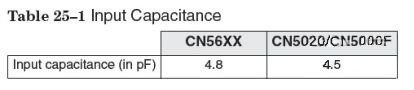

假设我们需要计算的电路参数如下所述。芯片管脚的输入电容如图4 CN56XX所示,Ci=4.8pF;所需要采用的晶体规格如图1所示,标称负载电容CL=12.5pF,晶体的寄生电容CS=0.85pF。

图4、CN56XX

我们可以得到下式:

为了保持晶体的负载平衡,在实际应用中,一般要求CG=CD,所以进一步可以得到下式:

根据CG的组成部分,可以得到:

CG=Ci+CPCB+CL1=23.3pF

晶体布线时都会要求晶体尽量靠近振荡电路,所以CPCB一般比较小,经验值大约0.5pF左右;Ci=4.8pF。所以最终的计算结果如下:(CL2的计算过程类似)

CL1=CL2=18pF

例外情况:

现在有很多芯片内部已经增加了补偿电容(internal capacitance),所以在设计的时候,只需要选按照芯片datasheet推荐的负载电容值的选择晶体即可,不需要额外再加电容。但是因为实际设计的寄生电路的不确定性,最好还是预留CL1/CL2的位置。

以上的计算都是基于CG=CD的前提,的确有一些意外情况,比如cypress的带RTC的nvsram的时钟晶体要求两边不对称,但是幸运的是,cypress给出了详细的计算过程以及选型参考。

(4)晶振振荡原理及设计原则

各种逻辑芯片的晶振引脚可以等效为电容三点式振荡器. 晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联. 在晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十 M 欧之间. 很多芯片的引脚内部已经包含了这个电阻, 引脚外部就不用接了. 这个电阻是为了使反相器在振荡初始时处与线性状态, 反相器就如同一个有很大增益的放大器, 以便于起振。

石英晶体也连接在晶振引脚的输入和输出之间, 等效为一个并联谐振回路, 振荡频率应该是石英晶体的并联谐振频率. 晶体旁边的两个电容接地, 实际上就是电容三点式电路的分压电容, 接地点就是分压点. 以接地点即分压点为参考点, 振荡引脚的输入和输出是反相的, 但从并联谐振回路即石英晶体两端来看, 形成一个正反馈以保证电路持续振荡. 在芯片设计时, 这两个电容就已经形成了, 一般是两个的容量相等, 容量大小依工艺和版图而不同, 但终归是比较小, 不一定适合很宽的频率范围.

外接时大约是数 PF 到数十 PF, 依频率和石英晶体的特性而定. 需要注意的是: 这两个电容串联的值是并联在谐振回路上的, 会影响振荡频率. 当两个电容量相等时, 反馈系数是 0.5, 一般是可以满足振荡条件的, 但如果不易起振或振荡不稳定可以减小输入端对地电容量, 而增加输出端的值以提高反馈量。

设计考虑事项:

1、使晶振、外部电容器(如果有)与 IC之间的信号线尽可能保持最短。当非常低的电流通过IC晶振振荡器时,如果线路太长,会使它对 EMC、ESD 与串扰产生非常敏感的影响。而且长线路还会给振荡器增加寄生电容。

2、尽可能将其它时钟线路与频繁切换的信号线路布置在远离晶振连接的位置。

3、当心晶振和地的走线

4、将晶振外壳接地

如果实际的负载电容配置不当,第一会引起线路参考频率的误差.另外如在发射接收电路上会使晶振的振荡幅度下降(不在峰点),影响混频信号的信号强度与信噪. ,当波形出现削峰,畸变时,可增加负载电阻调整(几十K到几百K).要稳定波形是并联一个1M左右的反馈电阻。