按照《数字计算机电子学》Digital Computer Electronics)中SAP-1的设计,使用proteus仿真了SAP-1(simple as possible)计算机。能完成这个工作,首先要感谢网友杨志雄先生对我的帮助,他帮我解决了很多电路和使用proteus的问题。

一. 系统架构

按冯·诺依曼型结构,计算机由运算器、控制器、存储器、输入设备、输出设备组成。运算器和控制器组合称为中央处理部件或CPU。

CPU的基本功能,是执行事先存放在主存储器中的程序。而控制器的任务,是识别、解释和控制(其他所有部件)执行程序中的每一条指令,并使整个系统运行在高度同步协调的状态。运算器的功能是完成算术和逻辑运算。存储器用来存储程序和数据。

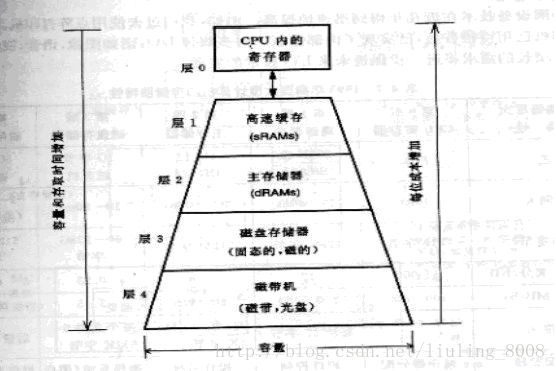

为了解决实际问题,需要计算机执行人们为解改问题而编制的程序。为存储和执行程序,要求系统有足够的存储空间和可以接受的执行时间。从解题的角度看,作为系统的一个重要组成部分的存储器,必须在存储容量和存取速度方面达到系统总体设计的要求。理想的存储器,应当是大容量、高速度、低成本。为了发挥各种不同类型存储器的长处,避开其弱点,应把它们合理地组织起来,这就出现了存储系统层次结构的概念。实际计算机系统中的存储器层次结构如下图所示。

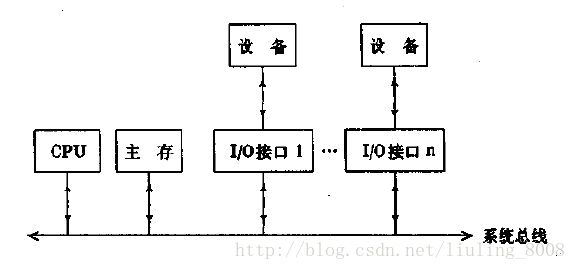

计算机中为什么要采用总线呢?主要目的是减少传输线总数以简化I/O系统的结构。例如有n个k位的部件相互要进行通信,如果不采用总线结构而直接采用传输线互连起来,那么在一般情况下,n个部件必须以所有可能的方式连接,需要的专用通路数目为[(n-1)*n]/2,而每条通路为k位,则传输线位数总数为[k*(n-1)*n]/2;若n、k很大,则传输线总位数多的惊人。构成总线的位传输线的总数称为总线宽度。采用共享总线结构,n个k位部件要相互进行通信,只需要宽度为k为的总线就可以,且与n的大小无关,这就大大节省了传输线成本。

如果计算机采用单总线结构,架构如下图:

单总线结构

SAP-1架构图:

在SAP-1中,

控制器包括:CON、PC、IR。存储器包括:MAR,PROM。运算器包括:累加器A、寄存器B,ALU。输出包括:输出寄存器O、LED显示D。输入需要在计算机运行前,使用开关将数据存储到PROM中。

其中累加器A、寄存器B属于存储系统,完全可以用PROM代替,而使用寄存器是了提高访问速度。MAR(存储器地址寄存器)缓存了PROM的地址,也是为了提高速度。IR用于缓存正在执行或即将执行的指令同样为了提高访问速度。

Ø PC(程序计数器)

PC寄存器用于存储当前指令在ROM中的地址。在SAP-1中,PC为4位计数器,计数范围为0000——1111。当计算机运行之前,PC重置为0000。

Ø IR(指令寄存器)

IR用于存放正在执行或即将执行的指令,将指令的操作码部分传送给CON,操作数部分通过总线传输到MAR。

Ø 控制单元(CON)

在SAP-1中,控制器包括。其中CON的功能包括

1. 产生时钟脉冲CLK,CLK将同步计算机中各个部件的运行。

2. 发送清除指令CLR,计算机运行之前,发送CLR给PC和IR,这样使IR的内容清空,PC重置 0000。

3. 根据IR中的操作码,产生一个12位控制信号 CP EP LM ER LI EI LA EA SU EU LB LO。(取指周期不需要操作码)

这些控制信号定义了各个寄存器在CLK的上升沿到达时的动作。例如,CP=1,代表在CLK上升沿到达时,PC将会加1。EP=1,LM=1,意味着,PC的内容会加载到MAR中。

Ø MAR(存储器地址寄存器)

在访问存储器时,缓存存储单元的地址。在SAP-1中,MAR为4位寄存器。

Ø PROM(可编程只读存储器)

存储器用于存储程序和数据。

在SAP-1中,PROM大小是16*8,意思是他有16个8位的存储单元,因此PROM的存储地址为0000——1111。程序需放在以0000开始的地址空间,数据需放在程序的后面。因为PC计数从0000开始,计算机运行后,首先从PROM的0000地址读取数据,所以程序必须存从0000开始存放。

Ø 累加器A

累加器A,是一个8位二进制寄存器,专门用来存放操作数或运算结果。在CPU执行某种运算前,两个操作数中的第一个放在累加器A中,运算完成后,累加器A中便可得到运算结果。

Ø 寄存器B

寄存器B也是一个8位二进制寄存器,该寄存器,用来存放加数或减数。

Ø ALU

ALU用于完成算术运算。在SAP-1中,SU=1时,ALU执行减法操作,A=A-B;SU=0时,ALU执行加法操作,A=A+B。为了简化ALU的设计,SAP-1中的数据是补码形式。因此PROM、A、B、O中的数据是以补码形式存放的。

Ø 输出寄存器O

当运算结束后,累加器A中存储计算结果。当EA=1,LO=1,下一个CLK上升沿到达时,寄存器A的内容通过总线到达输出寄存器O。

Ø LED显示D

D是一排8个LED灯构成的,而LED灯连接了输出寄存器O,LED将输出寄存器O的内容。当执行OUT指令后,我们将看到二进制补码形式的答案。

Ø 总线(W bus)

在SAP-1中,总线是8位的。跟总线连接的如果是部件的输出需要使用三态门,如果是部件的输入使用使能端控制是能否输入。

三态门

当ENABLE = 0时,相当于Din与Dout处于断开状态。

当ENABLE = 1时,Dout = Din。

例如,寄存器A、B、C、D之间使用总线传输数据,如下图所示。

总线

其中,A、B、C、D的输出通过三态门与总线相连。LOAD为输入使能端,LOAD=1时,输入端数据存入寄存器。LOAD=0时,不接收输入数据。为输出使能端(为三态门使能端),ENABLE=0时,寄存器与总线连接处于断开状态。ENABLE=1时,寄存器与总线处于连接状态,寄存器的输出会输出到总线上。

在本例中,如果寄存器中存储的数据为

A = 0011 B = 0110 C = 1001 D = 1100

如果需要将寄存器C的数据传送到B,只要使EC = 1, LB = 1,这样会使寄存器C的内容传送到总线,同时寄存器B的输入使用端 ENABLE = 1,会将连接到总线输入端的数据存入寄存器中。当CLK的上升沿到达时,寄存器B=1001。

二.指令

指令,是计算机硬件和软件的接口。计算机软件通过编制程序来解决问题。程序为指令序列或被翻译成指令序列。而计算机硬件的功能是执行指令序列。因此计算机硬件设计的最终目的是设计指令,并实现这些指令。

机器指令集像餐馆的菜单。如果顾客想吃饭,拿到餐馆的菜单,写出自己想吃的菜;而厨师按照顾客的菜单做菜。这样顾客就能吃到自己想吃的菜了。顾客吃到想吃的菜是计算机需要实现的功能,首先顾客写出菜单,就是编制程序,餐馆菜单中的每一道菜是一条指令,整个菜单是机器的指令集。而厨师拿到顾客的菜单,看到自己需要做的菜,然后按顺序作出这些菜。厨师就相当于硬件,按顺序执行顾客菜单指令。

在SAP-1中,只有五条指令,下面将对五条指令分别介绍。

Ø LDA(load the accumulator)

LDA将数据加载到累加器A。格式为,LDA R*(ROM地址)。例如,加载ROM中R8的数据。R8中的数据为, R8 = 1111 0000。指令为 LDA R8(地址)

Ø ADD

ADD将数据与累加器A中的数据相加,结果放在A中。

格式:ADD R*。例如,ADD R9意思是“将 R9中的数据与A中的数据相加,结果放在A中”。下面用实际数据来说明,A中的数据为2,R9中的数据为3,用二进制的形式表示为,

A = 0000 0010

R9 = 0000 0011

ADD指令的执行过程,首先, R9被加载到 B中,因此B的内容如下,

B = 0000 0011

随后,ALU完成了A+B的计算(由于ALU不需要CLK同步),

ALU = 0000 0101

然后, ALU内容被加载到累加器A中,

A = 0000 0101

这样A中最终存储了运算结果。

Ø SUB

SUB将累加器A中的数据减去PROM中的某个数据,结果放在A中。

格式:SUB R*

处理过程参考ADD

Ø OUT

OUT指令将A寄存器中的数据传输到O寄存器中。

格式: OUT

Ø HLT

HLT代表停机。

格式: HLT

在SAP-1的程序末尾必须使用HLT指令,否则计算机会崩溃,因为SAP-1将取出ROM中存储在程序后面的无意义数据进行执行,所以会得到无意义的结果。

指令编码表

如果想将上面这些指令在SAP-1中存储,执行,需要将他们用二进制编码。

| 指令名称 |

编码 |

| LDA |

0000 |

| ADD |

0001 |

| SUB |

0010 |

| OUT |

1110 |

| HLT |

1111 |

下面举例说明如何给SAP-1编程,比如计算 16 + 20 + 24 + 28 – 32的值。

可以16存储到R9中,20存储到RA中,24存储到RB中,28存储到RC中,32存储到RD中。其中R*为ROM地址,例如R9为ROM中编号为1001的地址。

ROM中存储的程序和数据如下:

程序:

R0 = 0000 1001 ( LDA 9(地址) )

R1 = 0001 1010 ( ADD A(地址) )

R2 = 0001 1011 ( ADD B(地址) )

R3 = 0001 1100 ( ADD C(地址) )

R4 = 0010 1101 ( SUB D(地址) )

R5 = 1110 **** ( OUT )

R6 = 1111 **** ( HLT )

数据

R9 = 0001 0000 ( 16十进制 )

RA = 0001 0100 ( 20十进制 )

RB = 0001 1000 ( 24十进制 )

RC = 0001 1100 ( 28十进制 )

RD = 0010 0000 ( 32十进制 )

下面的详细设计参见《 SAP-1设计与实现(2)》