Verdi 使用教程(持续更新中)

转载请标明出处:

原文发布于:浅尝辄止,未尝不可的博客

https://blog.csdn.net/qq_31019565

Verdi 使用教程

##在这篇文章基础上重新编写

(2019-03-24新增)

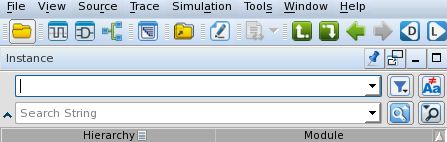

nTrace main window

menu bar commands

1.File Commands

File->Import design(命令位置)

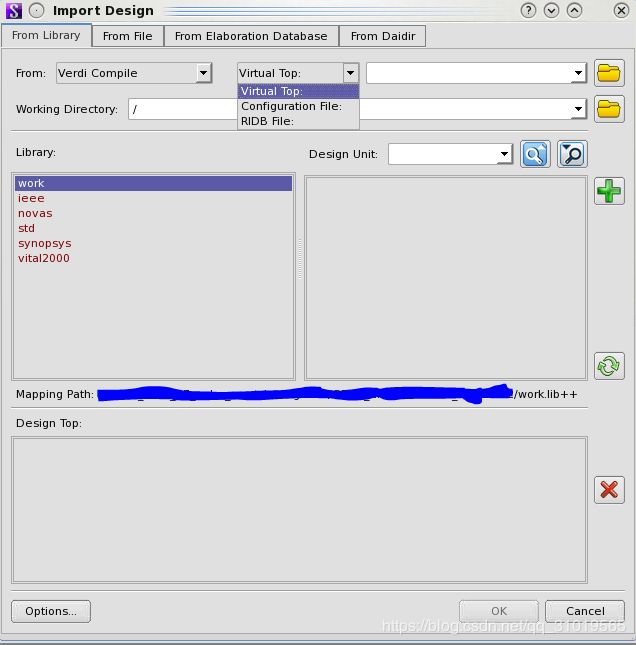

点击import design后,会出现如上的一个新的窗口。窗口会包含至少两个Lab,分别是From library 和 From file。

From library lab

Verilog和VHDL设计可以从一个预编译库进行import

From : 选择Verdi Knowledge Database(KDB)产生来源。有两个选项,Verdi Compile和VC/VCS Native Compile。如果选择Verdi Compile,则说明KDB由vericom或vhdlcom产生,novas.rc文件被使用。如果选择VC/VCS Compile,则说明KDB由VCS产生,synopsys_sim.setup文件被使用。

当在命令行中使用 -simflow 选项的时候,在Import Design窗口被打开的时候,会自动选择VC/VCS Native Compile。

Virtual Top : 这个字段可以被用来引入部分设计。而不是全部。此下拉菜单中包含三个选项,第一个是Virtual Top, 第二个是Configure File, 第三个是RIDB File.

Configure File : 是用来添加配置文件的。

Work Directory : 为库文件制定工作目录。

Library : 这一栏罗列了当前目录下所有可以用的库文件。

Design Unit :

(2019-03-24新增)

技术背景

在Design Flow中,有各种各样的Debug情景,我们也会花费大量的时间去Debug。但是在这个过程中会遇到各种各样的瓶颈,这会对Debug的效率造成影响。最直观的例子就是复杂的设计。无论是对设计的直观理解,还是设计多样化behavior所造成的Increase condition、design cause和effect scenarios,以及多Team的环境和实现方法的复杂性,都给这Debug的效率造成了不小的影响。

基于这些问题,Verdi应运而生。优势我就不赘述了,总之可用。

总目录

一、Set Up the Environment

二、Import Design

三、在Source Code View 中Debug

四、在Waveform View 中Debug

五、在Schematic View 中Debug

六、在FSM View 中Debug

七、在Temporal Flow View 中Debug

八、附录(经常用到的Preferences)

一、Set Up the Environment

内容概要:

- 在运行之前准备环境:指定路径和环境变量,Binary、License、符号库;使用Setup文件 novas.rc

- 指定Preferences。

- 理解FSDB(Fast Signal Data Base) dumping任务和作用。

二进制文件

setenv NOVAS_INST_DIR

set path = ($NOVAS_INST_DIR/bin $path)

License File

setenv NOVAS_LICENSE_FILE

或者是使用备用的LM_LICENSE_FILE,这个文件的搜索优先级小于NOVAS_LICENSE_FILE

Symbol Libraries

为什么使用符号库?

符号库提供了源代码到逻辑单元的映射,没有符号库会带来很大的不便。

使用以下方法之一创建符号库:

syn2SymDB:适用于 ASCII格式的Synopsys logic library(.lib)

map2SymDB:适用于已有的map file

结合user guide ,目录

设置符号库环境变量

setenv NOVAS_LIBS"LIB ROOT#1>

setenv NOVAS_LIBPATHS"

通过GUI设置符号库

步骤:

- 菜单栏点击Tools–>Preferences

- 在打开的子窗口中 Find一栏 查找 Schematic -->Symbol Library

- 填写Symbol Library Name

- 填写Symbol Library Path

- 保存,然后设置将被保存到novas.rc 源文件中。

使用Setup文件 novas.rc

Contains

- 为预编译设计映射信息,在物理位置映射逻辑库的名字。映射格式如下:

[Library]

logical name = physical location (ex, pack = ./work)

pack = ../library/back (ex, vital = ./work) - 用户自定义Preferences,(用法Tools–>Preferences)

指定路径

使用NOVAS_RC环境变量

setenv NOVAS_RC

直接通过命令行命令 -rcFile

搜索次序

- -rcFile

命令行选项 - NOVAS_RC环境变量

- ./novas.rc

- $HOME/novas.rc

/etc/novas.rc

Preferences

Overview

通过Tools–>Preferences打开窗口,所有设置将被保存在novas.rc文件中,在Find窗口栏中根据关键字搜索。可以参考附录说明来使用Preferences。

Fast Signal Data Base (FSDB)

FSDB文件介绍

- 压缩的二进制文件格式,包含仿真信号数据。

- 开放文件格式,其他的供应商工具可以dump波形,比如Verisity,Vera,Ikos,etc.

- 利用System Task来帮助dump。

经常使用到的系统任务

fsdbDumpfile - 指定文件名,限制FSDB文件的大小。在FSDB文件中保存最新的值,如果文件大小受到了限制,那么会自动丢弃最旧的值。

fsdbDumpvars - Dump特定实例和宽度的信号值的变化。也可以指定fsdb文件的名字,不同的FSDB文件的名字可以在每一个fsdbDumpvars命令上指定。

fsdbDumpon/fsdbDumpoff - 开关fsdb Dumping,可以指定FSDB文件的名字来开关特定的FSDB文件。

fsdbSwitchDumpFile - 转换Dumping到另一个FSDB文件。

fsdbAutoSwitchDumpfile - 限制FSDB文件的大小,并且自动转换Dumping到另一个FSDB文件。

NOTE1:以上的task是用在VHDL仿真器中的。然后加$前缀可以用在Verilog模拟器中。

NOTE2 :可以参考Linking Novas Files with Simulators and Enabling FSDB Dumping(/doc/linking_dumping.pdf)来查看更多的System Tasks。

为FSDB dumping 链接Novas对象文件

创建工具的环境变量

- setenv LM_LISCENSE_FILE

_INST_DIR - NOVAS_INST_DIR

- 使用 LD_LIBRART_PATH 在${NOVAS_INST_DIR}/share/PLI/lib指定共享对象文件和共同库。

setenv LD_LIBRART_PATH

${NOVAS_INST_PATH}/share/PLI// :

${NOVAS_INST_PATH}/share/PL/lib/

支持的仿真器有:VCS /IUS / MODELSIM

为仿真创建工作库和编译设计代码

在命令行上运行和调用FSDM dump函数

NOTE:参考

FSDB Utilities

vfast - 将VCD文件转化为FSDB文件。

fsdb2vcd - 将FSDB文件转化为VCD文件。

fsdbextract - 在已经存在的fsdb文件中提取信号,范围,时间周期,而不用重新进行仿真。

fsdbmerge - 将多个文件结合到一个里面。

fsdbreport - 针对一个特定的信号,将值得变化情况生成report。

小结

本节学习内容:

- 在运行Verdi之前如何设置环境变量

- 如何设置preferences

- 如何理解FSDB dumping 任务和utilities

二、Import Design

在命令行上载入Design

From File

verdi [Verdi options] [

在命令行上引用源文件(只适用于Verilog),Verdi 有所有Verilog命令行选项。

% verdi -f

% verdi

% verdi -ssv -v lib.v +libext+.v -ssy -y /src/abc -y /src/def top.v

-ssv 和 -ssy 对于用-v和-y指定的设计模块只需要一次。 top.v 是设计文件。

From Library

编译一次,可以加载多次

保存加载时间和全部的缓存

多语言需求,VHDL和Verilog,也可以只限定一种语言。

预编译设计到库,Verilog代码用vericom,VHDL代码用vhdlcom。

% vericom -lib

% vhdlcom -lib

然后载入编译库文件和指定的top 文件。

% verdi -lib

比如 :verdi -lib work -top system

By Replying a TCL Command File

你可以在 ./verdiLog/verdi.cmd file 中查看执行过的命令。如图所示,将图片的最后一行删除,然后运行 verdi -play

在图形化界面上载入Design

From File

首先在LInux 命令行上输入 verdi ,载入verdi 图形化界面。

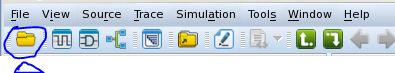

然后 通过菜单栏 File ->Import Design 或者通过 菜单栏上的Import Design符号,如图所示:

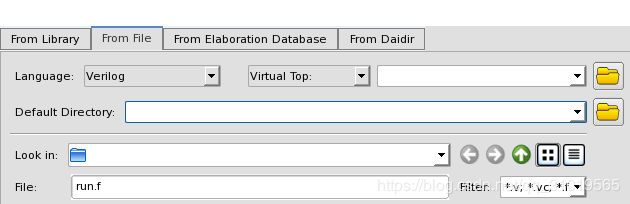

Import Design操作界面如下所示:

从界面上可以看到,可以自定 language、run file或者是个人的源文件,也支持Virtual Top文件,这里不建议使用VHDL。

Debug in Source Code View

打开Trace窗口

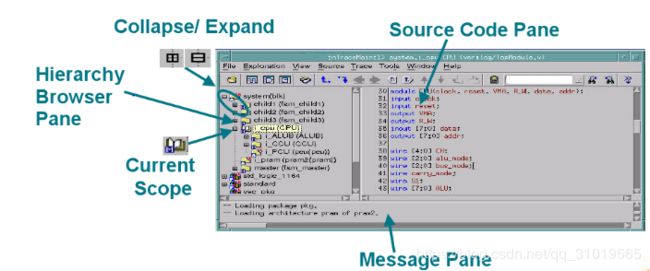

完成之前所述的Import Design以后,Verdi 会自动载入trace 窗口(可以使用verdi -f run.f),如下图所示各个部分分布。

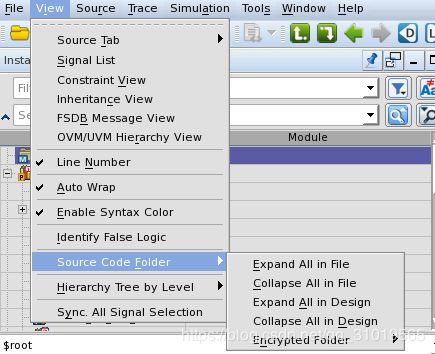

搜索或者是折叠浏览

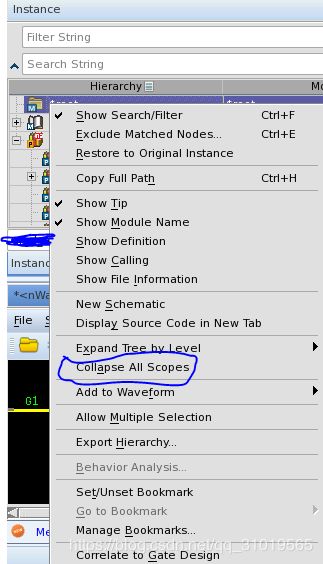

折叠浏览

如上所示,在instance Trace窗口中右击就会出现相关的命令选项,图中圈出的则为折叠浏览。

遍历源代码

查找操作

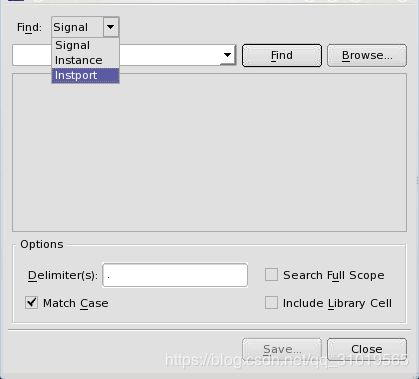

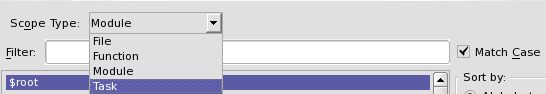

- source->find signal 查找操作,会出现以下图形界面,这是一个快速在指定范围内查找的方法。

- 在工具栏查找想要的字符串

- Source->find scope,可以直接打开Verilog module,或者VHDL

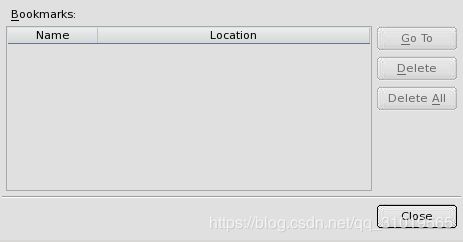

使用Source ->use bookmarks来添加书签,右击书签,选择Edit bookMarks则会出现如下界面

折叠源代码

To be continued…