服务器软件firmware的作用(BIOS、BMC、PSOC、CPLD)

写在前面:

服务器 从功能上来讲,跟我们日常学习办公使用的台式机和笔记本没有本质区别,主要也是由最为关键的三大件CPU、内存、硬盘组成,但是服务器的应用场景主要是提供给企业等角色用来支撑形形色色业务,不仅仅是用来安装浏览器访问网页、安装播放器看看电影,因此服务器会使用更强的配置,即更强劲的CPU、更大的内存、更大的硬盘存储。从外形上来说,服务器存在多种外形,如机架式、刀片式、塔式等等,最主要的区别在于服务器一般不会配置显示器、键盘、鼠标等部件用于近端操作,一般通过IP远程连接的方式访问即可。因为服务器一般情况下都会放置于单独的机房,而且风扇噪音会比家用电脑更大些。

Firmware 一般指固件,固件(Firmware)就是写入EPROM(可擦写可编程只读存储器)或EEPROM(电可擦可编程只读存储器)中的程序。

固件是指设备内部保存的设备“驱动程序”,通过固件,操作系统才能按照标准的设备驱动实现特定机器的运行动作,比如光驱、刻录机等都有内部固件。

固件是担任着一个系统最基础最底层工作的软件。而在硬件设备中,固件就是硬件设备的灵魂,因为一些硬件设备除了固件以外没有其它软件组成,因此固件也就决定着硬件设备的功能及性能。

原理:

固件(firmware)一般存储于设备中的电可擦除只读存储器EEPROM(Electrically Erasable Programmable ROM)或FLASH芯片中,一般可由用户通过特定的刷新程序进行升级的程序。一般来说,担任着一个数码产品最基础、最底层工作的软件才可以称之为固件,比如计算机主板上的基本输入/输出系统BIOS(Basic Input/output System),在以前其实更多的专业人士叫它固件。

通常这些硬件内所保存的程序是无法被用户直接读出或修改的。在以前,一般情况下是没有必要对固件进行升级操作的,即使在固件内发现了严重的Bug也必须由专业人员带着写好程序的芯片把原来机器上的更换下来。早期固件芯片一般采用了ROM设计,它的Firmware代码是在生产过程中固化的,用任何手段都无法修改。随着技术的不断发展,修改固件以适应不断更新的硬件环境成了用户们的迫切要求,所以,可重复写入的可编程可擦除只读存储器EPROM(Erasable Programmable ROM),EEPROM和flash出现了。这些芯片是可以重复刷写的,让固件得以修改和升级。

固件的其他介绍

一、BIOS

1.界面信息

主界面:

BIOS信息:包括版本、生成日期、固件版本等

主板信息:平台、处理器、PCH等

内存信息:内存容量

系统信息的设置:语言、时间

ME (Intel Management Engine) :Intel ME 是 Intel Management Engine 的简称 ,中文翻译为 英特尔管理引擎,Intel ME 是指 Intel 芯片中一个独立于CPU和操作系统的微处理器。ME里面有用于远程管理的功能,在出现严重漏洞的时可以在不受用户操控下远程管理企业计算机。

高级选项:

关于CPU、PCH、PCI以及USB等的配置

1、处理器配置:

预取

缓存技术利用局部性原理,使速度更快的上层存储器成为下层存储器的缓冲。基于技术的限制及成本的考虑,上层存储器的容量要比下层存储器小得多。数据如果存在于上层存储器中,就可以直接对其进行读写, 这种情形叫做命中,命中的统计概率叫做命中率;如果未命中就必须涉及到访问下层存储器,这种情形也叫失效。

但是随着应用规模的不断扩大缓存失效所占的比例越来越大,成为影响缓存性能的主要因素。为了提高缓存的命中率,

预取技术通过计算和访存的重叠,在Cache可能会发生失效之前发出预取请求以便在该数据真正被使用到时己提前将数据块取入Cache,从而避免Cache失效造成的处理器停顿。

2、常用参考代码

3、UPI配置

4、内存配置

5、IIO配置

Linux设备驱动之IIO子系统,是专用于模数转换器(ADC)和数模转换器(DAC)的内核子系统。

6、高级电源管理配置

CPU P状态控制

以下是ACPI规格的具体电源管理状态:

全局状态(Global system states) ·用户可见 ·分4个状态:G0, G1, G2, G3

睡眠状态(Sleeping states) ·全局状态G1(不含S5)的睡眠状态 ·分5个状态:S1,S2,S3,S4,S5

设备电源状态(Device Power states) ·用户不可见 ·只要有一个配置显示为“on”(启动)状态,另一个则显示为“off”(关闭)状态 ·分4个状态:D0,D1,D2,D3

CPU电源状态(CPU Power states) ·也叫做CPU睡眠状态 ·在全局状态G0 ·分5个状态:C0,C1,C2,C3,C4 ·将来会有C6状态(Penryn)

CPU/设备性能状态(CPU / Device Performance states) ·电压和时钟频率由工作量决定 ·P-state状态总量符合CUP/设备规格 ·例如,CPU倍频越高,P-states就越高

CPU温度监控(CPU Thermal Monitor) ·当CPU温度超过极限时,监控系统会降低CPU的性能 ·在TM1中,功过改变周期来降低CPU性能 ·在TM2种,通过改变时钟频率和核心电压(P-state)来降低CPU性能

服务器管理

关于BMC的等待时间、预设值、网络配置、用户信息以及日志等设置,还可查看BMC的自检状态、版本以及系统事件日志。

安全

设置管理员密码和用户密码

输入管理员密码则有权进入BIOS SETUP;用户密码是开机密码,可以进入启动列表或者BIOS界面。

BOOT:

1、setup prompt timeout:设置启动时屏幕提示等待时间

2、bootup numlock state:是启动时键盘上的数字锁定键的状态的意思。

3、quick boot(迅速启动)建议开启(enabled),可提高启动的速度

说明:开机每次都要检测硬件 在bios里设置quick boot,计算机在启动时不进行全面自检,从而加速系统

启动速度quiet boot(安静开机)

说明:此项目让您在开机画面上显示供货商标志。设定值为:关闭(disabled)、开启(enabled)。预设设定值为「开启」(enabled)。

4、boot mode select:选择UEFI/Legacy

5、fixed boot order priorities:固定的启动顺序优先级

6、CSM配置

CSM (兼容性支持模块):是BIOS上Boot选项里的一个下拉子项目(一些老的主板上没有此选项),与Secure Boot(安全启动)是并列项。CSM开启使得可以支持UEFI启动和非UEFI启动。若是需要启动传统MBR设备,则需开启CSM。关闭CSM则变成纯UEFI启动,且完全支持安全启动。Secure Boot(安全启动),安全启动仅适用于使用UEFI启动的操作系统。在笔记本的BIOS里,这里更多的是使用Enabled(打开)和Disabled(关闭)两个选项。在电脑自带Windows 8的情况下,Secure Boot(安全启动)默认是Enabled(打开)。从而使得CSM(兼容性支持模块)又默认是Disabled(关闭),进而导致电脑不能启动不完全支持UEFI的设备。要使得电脑能启动不完全支持UEFI的设备,就必须关闭Secure Boot,然后打开CSM。

保存退出

选择是否保存之前的各种设置,也可恢复默认设置,退出BIOS

2、BIOS阶段划分

BIOS大致可以划分为6个阶段,具体如下:1.SEC:Security(安全) (处理平台重启事件;创造一个临时的内存区(注意:这个时候内存还未初始化);在系统中作为一个可信的root;传递信息到PEI。 开发者可以不怎么关注,极少涉及)2.PEI:pre-efi initialization(预EFI初始化) ( 初始化一些永久的内存;HOBs(Hand-off Blocks)中的内存;以及在HOBs里面的FV(firmware volume)位置;传递控制权到DXE阶段。 开发者需要一定的关注,用得还是比较多的)3.DXE:driver execution environment(驱动程序执行环境) (开发者需重点关注,从名字可以看出来,服务器上硬件驱动的执行环境,与后期外设的使用,有极大的关系)4.BDS:boot device select(引导设备选择) (初始化console设备;加载设备驱动;尝试加载和执行启动项。 开发者同样需要重点关注)5.RT:run time service(运行时服务) (这个层次,基本和OS bootloader关系比较紧密,需要了解OS)6.AL:after life(transition from the os back to the environment) of system

3、BIOS与BMC的通信

在x86服务器,BIOS需要与各种硬件和芯片打交道,当然也包括BMC(Baseboard Management Controller)。

BIOS与BMC之间的通信,主要使用的是IPMI。有2个阶段,PEI和DXE(包括DXE后面的),用的是不同的IPMI函数(这点需要注意)。虽然使用的是IPMI,但是会有两个通道,分别是KCS、BT。一般使用KCS通道。请记住,BMC是不能主动与BIOS通信的;BIOS会发送IPMI命令给BMC,BMC如果成功接收的话,就会有个返回信息给BIOS,所以“看起来像是BMC可以与BIOS通信”。

如果产生了通信故障如何解决:(1)确认BIOS是否发送了IPMI命令给BMC,可以查看BMC返回的completion code;(2)确认BMC是否收到了BIOS发送的IPMI命令;(3)如果BIOS发送了IPMI命令,但是BMC未接收:可能是BMC的IPMI进程正处于忙碌状态,所以丢掉了这条IPMI命令(BIOS这边如果发送失败,可以尝试多次发送;另外,可以稍微调高点KCS通道的延时);当然,也有可能是BMC的IPMI进程挂了。(4)如果涉及到了底层协议的具体实现,一条IPMI命令通常涉及到2个底层实现函数,SendDataToBmcPort()和ReceiveBmcDataFromPort()。接收时,BIOS从KCS的I/O端口读取数据,读完后,会检测KCS寄存器中OBF状态寄存器,如果BMC没有写数据,就会计数减1,延时5ms,然后重试;当BMC一直不写数据时,计数到0,就认为BMC有故障,返回Device Error。

4、BIOS在计算机启动过程中的工作

4.1、基本概念

4.1.1 BIOS(基本输入输出系统)

BIOS直接与硬件打交道,为操作系统提供控制硬件设备的基本功能。

BIOS分为系统BIOS(主板BIOS,控制计算机启动的主要代码)、显卡BIOS和其他设备BIOS(IDE控制器、SCSI卡或网卡)

BIOS一般存放在ROM(只读存储芯片)中,在关机或掉电后,这些代码也不会消失。

4.1.2 内存地址

内存每个字节都被赋予了一个地址,以便CPU访问。最初的8086处理器能够访问的内存最大只有1MB(0~FFFFFH): 低端640KB被称为基本内存;A0000H~BFFFFH保留给显示卡显存使用;C0000H~FFFFFH则保留给BIOS使用,其中显卡BIOS一般在C0000H~C7FFFH处,IDE控制器的BIOS在C8000H~CBFFFH处,系统BIOS一般占用了最后的64KB或更多一点的空间。

4.1.3 MBR

磁盘指的是硬盘、软盘、U盘、光盘等等这种类型的设备。 对每个类型磁盘,都有MBR和分区来组成这个磁盘。 按照标准,每个磁盘可以有最多4个主分区,1个扩展分区。扩展分区上可以分多个逻辑分区。磁盘每个分区的第一个扇区是用来存放特别的信息,比如引导加载程序,而不用来存放文件等信息(每个分区的第一个扇区无法通过文件系统来访问)。 注意:MBR不属于任何分区。MBR除了存放引导加载程序,还在后64个字节中存放这个磁盘的分区表。

4.2、BIOS启动过程

4.2.1

按下电源开关,电源就开始向主板和其它设备供电;此时电压还不太稳定,主板上的 控制芯片组会向CPU发出并保持一个RESET(重置)信号,让CPU内部自动恢复到初始状态,但CPU在此刻不会马上执行指令;当芯片组检测到电源已经开始稳定供电了(当然从不稳定到稳定的过程只是一瞬间的事情),它便撤去RESET信号(如果是手工按下计算机面板上的Reset按钮来重启机器,那么松开该按钮时芯片组就会撤去RESET信号);CPU马上就从地址FFFF0H处开始执行指令。这个地址是系统BIOS的地址范围,这里放的只是一条跳转指令,跳到系统BIOS中真正的启动代码处。

4.2.2 系统BIOS的启动代码首先进行POST(Power-on self test 加电后自检)

POST主要检测系统中的一些关键设备是否能正常工作,eg:内存和显卡。

由于POST是最早进行的检测过程,此时显卡未初始化,如果系统BIOS在POST过程中发现致命错误,eg:未找到内存或内存有问题(此时只检查640k常规内存),那么系统BIOS就会直接控制喇叭发声报告错误,声音不同,错误类型不同。

在正常情况下,POST非常快,结束后会调用其它代码来进行更完整的硬件检测。

4.2.3 系统BIOS查找显卡BIOS

系统BIOS在C0000H处找到显卡BIOS之后就调用它的初始化代码,由显卡BIOS初始化显卡。此时会在屏幕上显示一些初始化信息(生产厂商、图形芯片等)。

系统BIOS会接着查找其他设备的BIOS程序,找到后同样调用这些BIOS内部的初始化代码完成设备初始化。

4.2.5

接着系统BIOS将检测CPU的类型和工作频率,测试所有的RAM,同时在屏幕上显示内存测试的进度。可在CMOS设置中自行决定使用简单耗时少或详细耗时多的测试方式。

4.2.6

内存测试通过后,系统BIOS将开始检测系统中安装的一些标准硬件设备(硬盘、CD-ROM、串口、并口和软驱等),较新版本的系统BIOS在这一过程中还要自动检测和设置内存的定时参数、硬盘参数和访问模式。

4.2.7

标准设备检测完毕后,系统BIOS内部支持即插即用的代码开始检测和配置系统中安装的即插即用设备。每找到一个设备,系统BIOS都会在屏幕上显示设备的名称、型号等,同时为该设备分配中断、DMA通道和I/O端口等资源。

4.2.8

所有硬件检测配置完毕,多数系统BIOS会清屏并在屏幕上方显示一个表格,概略列出了系统中安装的各种标准硬件设备以及他们使用的资源和一些相关工作参数。

4.2.9

接着系统BIOS将更新ESCD(Extended System Configuration Data,扩展系统配置数据)。ESCD是系统BIOS用来与操作系统交换硬件配置信息的一种手段,这些数据被存放在CMOS(一小块特殊的RAM,由主板上的电池来供电)之中。通常ESCD数据只在系统硬件配置发生改变后才会更新,所以不是每次启动机器时都能够看到“Update ESCD… Success”这样的信息。不过,某些主板的系统BIOS在保存ESCD数据时使用了与Windows 9x不相同的数据格式,于是Windows 9x在它自己的启动过程中会把ESCD数据修改成自己的格式。但在下一次启动机器时,即使硬件配置没有发生改变,系统BIOS也会把ESCD的数据格式改回来。如此循环,将会导致在每次启动机器时,系统BIOS都要更新一遍ESCD,这就是为什么有些机器在每次启动时都会显示出相关信息的原因。

4.2.10

ESCD更新完毕后,系统BIOS的启动代码将进行它的最后一项工作:即根据用户指定的启动顺序从软盘、硬盘或光驱启动MBR。系统BIOS将读取磁盘上的主引导记录MBR,并放入指定位置(0x7c00)的内存。然后BIOS把控制权交给MBR。主引导记录由两部分组成:代码和分区表。MBR代码首先检测其他代码(如查看是否有"55AA"有效标记),然后从分区表中找到第一个活动分区,读取并执行这个活动分区的分区引导记录。

以上就是计算机在打开电源开关进行冷启动时要完成的各种初始化工作。如果从Windows中选择重新启动计算机来进行热启动,那么post将被跳过,直接从第三步开始,另外第五步的检测CPU和内存测试也不会进行。

二、BMC

在介绍BMC之前需要了解一个概念,即平台管理(platform management)。平台管理表示的是一系列的监视和控制功能,操作的对象是系统硬件。比如通过监视系统的温度,电压,风扇、电源等等,并做相应的调节工作,以保证系统处于健康的状态。当然如果系统真的不正常了,也可以通过复位的方式来重新启动系统。同时平台管理还负责记录各种硬件的信息和日志记录,用于提示用户和后续问题的定位。以上的这些功能可以集成到一个控制器上来实现,这个控制器被称为基板管理控制器(Baseboard Manager Controller,简称BMC)。

BMC是一个独立的系统,它不依赖与系统上的其它硬件(比如CPU、内存等),也不依赖与BIOS、OS等(但是BMC可以与BIOS和OS交互,这样可以起到更好的平台管理作用,OS下有系统管理软件可以与BMC协同工作以达到更好的管理效果)。一般我们的电脑不会带BMC,因为用处不大,一些温度、电源等的管理,CPU来控制就够了。但是对于系统要求高的设备,比如服务器,就会用到BMC。当然因为BMC是一个独立的系统,对于某些嵌入式设备,可能不需要其它处理器,光一个BMC就能完成工作。说到底BMC本身也是一个带处理器(一般都是ARM处理器)的小系统,单独用来处理某些工作也完全是可以的。

BMC全称BaseboardManagement Controller,通俗来讲,BMC是整个服务器单板的大管家。从一款服务器上电时刻,它的所有部件都归BMC来负责和管理。BMC是一个独立于服务器系统的小型操作系统。作用是方便服务器远程管理、监控、安装、重启等。 BMC是一个集成在主板上的芯片(也有通过PCIE等各种形式插在主板上),对外表现形式只是一个标准的RJ45网口,拥有独立的IP。普通维护只需使用浏览器访问IP:PORT登录管理界面,服务器集群一般使用BMC指令进行大规模无人值守操作。一般服务器BMC网口是独立的,仔细看印有BMC字样,也有小型服务器BMC网口和通信网口是二合一的。

BMC是一款服务器AC上电起始即运行的软件,运行在服务器上一款单独的ARM芯片上,这个ARM芯片就是BMC软件的CPU,同时会芯片外围会配置自己的RAM、Flash等器件,只要服务器插上电源线,BMC软件便快速运行起来,此时有可能我们通常意义上的x86服务器侧的OS都还没有安装呢。BMC是整个服务器的大管家,主要用于服务器各个部件(CPU、内存、硬盘、风扇、机框等)的温度、电压等健康状态进行检测,同时根据各个温度采集点情况实时调整风扇转速保证服务器不产生过温、而且控制总体功耗又不能过高,如果单板部件出现任何异常则通过SNMP协议、SMTP协议、Redfish协议等多种业界通用规范讲信息及时上报给上层网管,以便运维人员及时处理,保证业务无损。

此处介绍下带外管理和带内的概念,通常情况下x86侧执行的运维管理动作被称作带内的方式,而BMC是脱离x86侧独立运行的服务器管理软件,被称作带外管理软件。 BMC可以采集任何服务器上的除x86侧运行的私有业务本身之外的任何信息,但是请注意,现在业界的BMC带外管理软件有各种解决方案,可以采集到任何你想要的信息。因为即使从带外无法获取的信息,当前业界也存在带外和带内监控结合、带外统一提供接口的方案,可以实现通过BMC获取任何想要获得信息。

从功能上来讲,BMC主要用于采集单个服务器上各种信息,同时提供给上层运维网管软件。主要有两种手段,第一种BMC会提供各种各样的接口供上层网管查询,如web、命令行等人机接口、SNMP、IPMI、Restful等机机接口;第二种是主动上报,当检测到有故障产生时,BMC可以通过SNMP trap消息、SMTP 邮件消息、Redfish http json报文等手段上报给上层网管软件的服务端,以便运维人员及时识别处理故障。一般情况下,BMC软件上报的消息中都会明确的指明具体是哪个部件产生了故障、处理建议是怎样的等等。

SNMP:简单网络管理协议(SNMP) 是专门设计用于在 IP 网络管理网络节点(服务器、工作站、路由器、交换机及HUBS等)的一种标准协议,它是一种应用层协议。SNMP 使网络管理员能够管理网络效能,发现并解决网络问题以及规划网络增长。通过 SNMP 接收随机消息(及事件报告)网络管理系统获知网络出现问题。

RESTFUL:一种网络应用程序的设计风格和开发方式,基于HTTP,可以使用XML格式定义或JSON格式定义。RESTFUL适用于移动互联网厂商作为业务使能接口的场景,实现第三方OTT调用移动网络资源的功能,动作类型为新增、变更、删除所调用资源。

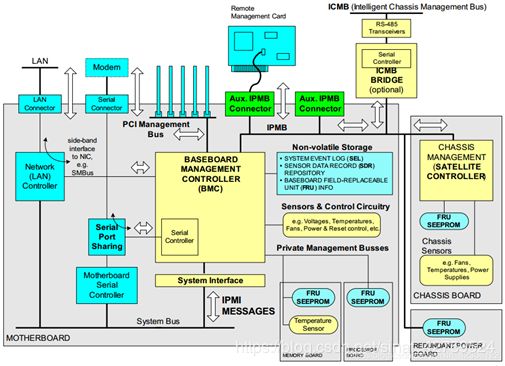

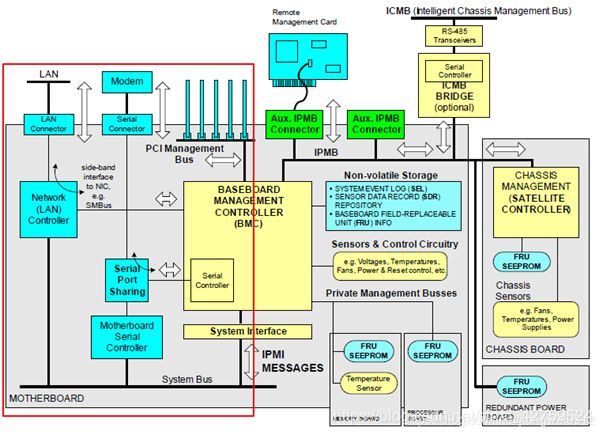

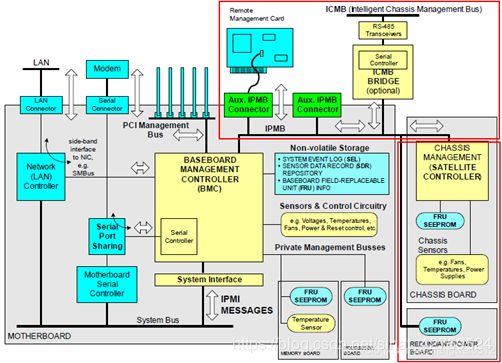

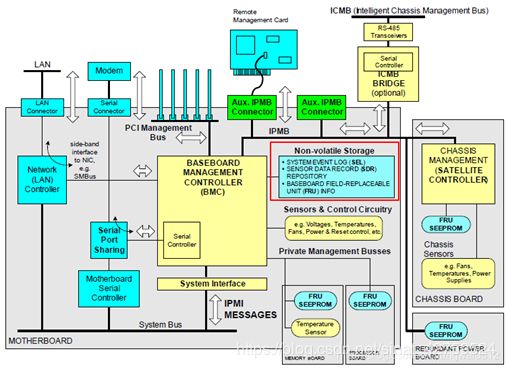

BMC通过不同的接口与系统中的其它组件连接。在**IPMB(Intelligent Platform Management Bus)**总线上连接着各个管理控制器,分别执行不同功能。IPMB总线上还连接着一些I2C器件,用来作为传感器的接口,让系统管理软件能够通过IPMB来读取传感器的数据。同时,这些传感器的具体配置信息,如告警门限、事件触发是否允许等配置都保存在一组名为SDR(Sensor Data Record)的数据里面。而传感器产生的告警事件则保存在一组叫做SEL(Sensor Event Log)的数据里面。在IPMB总线上,连接着一个ICMB(Intelligent Chassis Management Bus)桥,通过ICMB可以和远程的另一个管理平台通信。此外,在IPMB总线上,还可以外接其他的用户板,用来扩展IPMI管理平台的功能。

BMC芯片就相当于计算机中的中央处理器,通过BMC芯片上一对SMBus接口连接网络,用户可通过网络访问实现对远程服务器接管的带外管理(Out-of-band)功能,例如远程接管服务器(Pre-OS),在客户端实现对远程服务器的完全接管;通过RS-232接口连接Modem,在远程服务器宕机情况下,用户可以通过拨号访问获取SDR、SEL数据,分析诊断故障原因;BMC通过IPMB接口访问模组风扇背板、电源背板等上的SMC,实现对各种背板的温度电压风扇转速等关键参数管理;BMC通过系统接口(多用SMIC:Server Management Interface Chip),实现IPMI消息传输机制,控制LCD显示和实现上层软件与底层F/W通信,实现告警、数据采集。SDR(传感器数据存储库)、SEL系统事件日志)、FRU(Field Replacement Unit)物理实体可以是做在芯片内的存储体,也可以是外挂的E2PROM。

在x86侧OS上部署一套自研的Agent,也可以采集到我想要的各种信息,对于少量与硬件强相关的信息,我在带内OS上通过BMC接口查询补全,这种带内结合带外管理的方式不是也挺好吗?

全带外管理,是当前各大服务器厂商推出的单板运维管理的解决方案。各大服务器厂商当前均自研统一的带内Agent信息补全工具,最终汇集信息至BMC侧统一对外提供接口。理论上来说,可以满足单板运维管理的诉求。对于服务器用户来说,这是零成本的解决方案,强烈建议采用,何必自己再研发一套增加成本呢?

不过这里既然叫做BMC,那么总的来说重点还是在平台管理,所以本文主要说的是服务器中的BMC。

BMC在系统中的位置大致如下图所示:

BMC通过不同的接口与系统中的其它组件连接。LPC、I2C、SMBUS,Serial等,这些都是比较基本的接口,而IPMI,它是与BMC匹配的总线,所有的BMC都需要实现这种接口,这里需要特别的介绍。

IPMI

IPMI的全称是Intelligent Platform Management Interface,智能平台管理接口。IPMI规定了很多的东西,BMC是其中最重要的一个部分,此外还有一些”卫星“控制器通过IPMB与BMC相连,这些”卫星“控制器一般控制特定的设备。

IPMB全称Intelligent Platform Management Bus,是一种基于I2C的串行总线,它用于BMC与”卫星“控制器的通信,其上传递的是IPMI命令。

下面的图描述了与IPMI有关的各个模块:

智能平台管理接口 (IPMI) 是一种开放标准的硬件管理接口规格,定义了嵌入式管理子系统进行通信的特定方法。IPMI 信息通过基板管理控制器 (BMC)(位于 IPMI 规格的硬件组件上)进行交流。使用低级硬件智能管理而不使用操作系统进行管理,具有两个主要优点: 首先,此配置允许进行带外服务器管理;其次,操作系统不必负担传输系统状态数据的任务。用户可以利用IPMI监视服务器的物理健康特征,如温度、电压、风扇工作状态、电源状态等。

IPMI的核心是一个专用芯片/控制器(叫做服务器处理器或基板管理控制器(BMC)),其并不依赖于服务器的处理器、BIOS或操作系统来工作,是一个单独在系统内运行的无代理管理子系统,只要有BMC与IPMI固件其便可开始工作,而BMC通常是一个安装在服务器主板上的独立的板卡。IPMI良好的自治特性便克服了以往基于操作系统的管理方式所受的限制,例如操作系统不响应或未加载的情况下其仍然可以进行开关机、信息提取等操作。

在工作时,所有的IPMI功能都是向BMC发送命令来完成的,BMC接收并在系统事件日志中记录事件消息,维护描述系统中传感器情况的传感器数据记录。

一般来说,BMC具有以下功能:

1.通过系统的串行端口进行访问

2.故障日志记录和 SNMP 警报发送

3.访问系统事件日志 (System Event Log ,SEL) 和传感器状况

4.控制包括开机和关机

5.独立于系统电源或工作状态的支持

6.用于系统设置、基于文本公用程序和操作系统控制台的文本控制台重定向

而通过IPMI ,用户可以主动监测组件的状况,以确保不超出预置阈值,例如服务器温度。这样,通过避免不定期的断电,协助维护了 IT 资源的运行时间。 IPMI的预告故障能力也有助于 IT 周期的管理。通过检查系统事件日志 (SEL),可以更轻松的预先判定故障组件。只要将服务器接入网络并且没有断开服务器的电源,不管服务器的处于何种状态(开机、关机、重启),都可以允许用户通过网络进行远程管理。

下面简单的介绍各个部分。

- MOTHERBOARD

首先是图中的左下角部分,名称写着Mother Board。

通常,在服务器中,这一部分是主角,它包含了CPU,PCH等主要的部件。它连接除了数个组件:网卡,串口和IPMI总线,其实还有一个部分在图中最上面中间的PCI总线。

网卡:服务器需要用到网卡,重点其实在于BMC到网卡的连接,后续会介绍。

串口:串口用于输出服务器的调试信息,值得注意的是Serial Port Sharing,它使得服务器的串口输出可以直接输出,也可以输出到BMC。至于为什么要输出到BMC,这里其实需要注意的是一种常用的场景。服务器位于机房,而工作人员通常不会直接在机房操作,而是通过网络(这也是为什么BMC会连接网卡的原因)进行操作,这个时候过需要获取服务器的串口信息,就不方便直接去机房,这个时候通过BMC来获取服务器串口信息就是一个好主意。

IPMI总线:这是BMC与服务器通信并进行控制的主体,当然少不了。

PCI总线:这个部分的作用跟串口很像。服务器除了输出串口信息,当然还需要输出图形界面之类的东西。从服务器端来看,它通过PCI连接的就是一个显卡,通过它来输出显示。 - IPMB

再来到图中的右上角,其中描述的是通过IPMB连接的设备。

这些设备跟BMC类似,也是用来进行管理芯片。它们是对BMC的补充,从而扩展BMC的功能。 - Non-volatile Storage

我们知道BMC其实是一个独立的芯片,那么它肯定也需要运行系统。通过BMC里面运行的是一个类Unix系统,而该系统就存放在Non-volatile Storage中,通常就是SPI Flash里面。跟一般的存储介质没有本质的区别。除了系统本身之后,还包含一系列BMC会存放的信息。比如从服务器上面获取到的串口信息;系统本身的报警信息;FRU信息等。

- Sensors & Control Circuitry

这一部分虽然图中只占很小的一部分,但却是BMC最基本的功能:获取信息和控制环境。BMC会通过I2C/PECI等总线去获取设备的温度,然后根据预先设定的策略去调整温度。调整的方式两种,一种就是调整风扇,属于主动降温;另一种是调整供电,比如CPU的P状态,或者关闭多余的硬盘等,属于被动降温。 - FRU

FRU的全称是Field Replaceable Unit。

从图中也可以看出,类似内存条,CPU等就属于FRU,它们在服务器中通常是可以更换的。

BMC会检测这些设备并保存相关的信息。

当这些设备的在位情况发生变化时,BMC会发生相关的告警。

三、PSoC

可编程化系统单芯片(PSoC),是一种可编程化的混合讯号阵列架构,由一个芯片内建的微控制器(MCU)所控制,整合可组态的类比与数位电路,内含UART、定时器、放大器(amplifier)、比较器、数位类比转换器(ADC)、脉波宽度调变(PWM)、滤波器(Filter)、以及SPI、GPIO、I2C等元件数十种元件,协助客户节省研发时间。

简介

可编程化系统单芯片(PSoC),是一种可编程化的混合讯号阵列架构,由一个芯片内建的微控制器(MCU)所控制,整合可组态的类比与数位电路,内含UART、定时器、放大器(amplifier)、比较器、数位类比转换器(ADC)、脉波宽度调变(PWM)、滤波器(Filter)、以及SPI、GPIO、I2C等元件数十种元件,协助客户节省研发时间。

Altera、Atmel、Xilinx、Lattice皆有推出PSoC产品。实现PSoC有两种方法:利用FPGA/CPLD;另一是在ASIC中加入可编程模组。

PSOC 固件主要功能:

SATA、SAS硬盘LED控制;

BMC获取PSOC版本信息;

BMC通过PSOC获取硬盘状态;

PSOC 4是一个可以重配置和扩展的平台架构,是一个包含ARM Cortex-M0 CPU的可编程嵌入式系统控制器。通过灵活自动布线资源,它将可编程及可重新配置的模拟模块与数字模块相结合。基于此平台的PSOC 4200-L产品系列组合了具有数字可编程逻辑、可编程模拟、可编程互联和片外存储器扩展安全性的微控制器、高性能的模数转换、支持比较器模式的运算放大器以及标准通信和定时外设。针对新应用和设计方面的要求。

PSOC 4200-L产品与PSOC 4平台系列产品完全向上兼容。可编程模拟和数字子系统支持灵活、现场调试的设计。

BMC更新PSOC固件

PSOC的固件可以通过BMC的WEBUI更新,PSOC固件在线更新文件是‘cyacd’格式的文件,BMC不能更新PSOC的hex文件。PSOC的hex格式的固件文件需要通过烧录器在工厂离线烧录或使用赛普拉斯提供的工具烧录。

BMC WEBUI更新PSOC路径:维护->固件更新->更新PSOC固件

当用户在BMC的WEBUI更新PSOC,BMC发送更新命令到PSOC,PSOC进入在线更新模式,然后BMC将PSOC的更新文件传输给PSOC,在PSOC内部完成更新。

BMC 发送I2C命令: 0x01 0x02

PSOC返回数据:0x01/0x00

当PSOC返回0x01时,说明PSOC进入了在线更新模式,然后BMC和PSOC交互完成固件的传输,PSOC内部再完成固件更新动作。如果要确定升级的固件是否正确,可以在BMC的WEBUI查看当前PSOC 的版本号。

四、CPLD

CPLD采用CMOS EPROM、EEPROM、快闪存储器和SRAM等编程技术,从而构成了高密度、高速度和低功耗的可编程逻辑器件。

CPLD主要由逻辑块、可编程互连通道和I/O块三部分构成。

CPLD中的逻辑块类似于一个小规模PLD,通常一个逻辑块包含4~20个宏单元,每个宏单元一般由乘积项阵列、乘积项分配和可编程寄存器构成。每个宏单元有多种配置方式,各宏单元也可级联使用, 因此可实现较复杂组合逻辑和时序逻辑功能。对集成度较高的CPLD,通常还提供了带片内RAM/ROM的嵌入阵列块。

可编程互连通道主要提供逻辑块、宏单元、输入/输出引脚间的互连网络。输入/输出块(I/O块)提供内部逻辑到器件I/O引脚之间的接口。

逻辑规模较大的CPLD一般还内带JTAG边界扫描测试电路,可对已编程的高密度可编程逻辑器件做全面彻底的系统测试,此外也可通过JTAG接口进行在系统编程。

由于集成工艺、集成规模和制造厂家的不同,各种CPLD分区结构、逻辑单元等也有较大的差别。

应用

基于SRAM(静态随机存储器)的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存配置数据。这些配置数据决定了PLD内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。由于SRAM的数据是易失的,因此这些数据必须保存在PLD器件以外的EPROM、EEPROM或FLASH ROM等非易失存储器内,以便使系统在适当的时候将其下载到PLD的SRAM单元中,从而实现在电路可重配置ICR(In-Circuit Reconfigurability)。