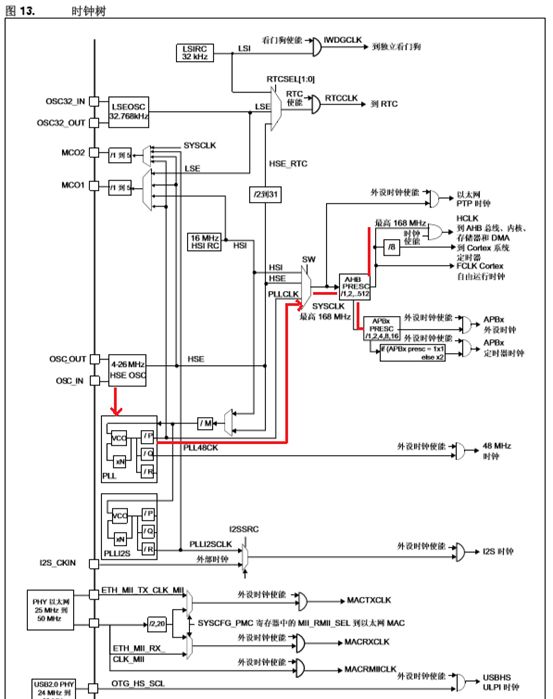

在STM32中,所有的应用都是基于时钟,所以时钟的配置就尤为重要了,而不能仅仅只知道使用默认时钟。

STM32F4的时钟树如上图所示,HSE为外部接入的一个8M的时钟,然后再给PLL提供输入时钟,经过分频倍频后产生PLLCLK时钟,为SYSCLK提供基础时钟来源。

配置的步骤:

- 将RCC寄存器重新设置为默认值

- 打开外部高速时钟晶振HSE

- 等待HSE时钟晶振工作

- 设置AHB时钟也就是HCLK时钟

- 设置高速APB1时钟也就是PCLK1

- 设置低速APB2时钟也就是PCLK2

- 设置PLL

- 打开PLL

- 等待PLL工作

- 设置系统时钟

- 判断系统时钟是否为PLL时钟

重点设置为PLL的配置:

void RCC_PLLConfig( uint32_t RCC_PLLSource, uint32_t PLLM, uint32_t PLLN, uint32_t PLLP, uint32_t PLLQ)

RCC_PLLSource为选择的输入时钟源,在这里为HSE

PLLM:VCO输入时钟分频因子,取值2-63 经分频后输入时钟范围要在1-2M内

PLLN:VCO输出时钟倍频因子,取值192-432经倍频后输出时钟范围要在192-432

PLLP:SYSCLK时钟分频因子,取值2、4、6、8

PLLQ:OTG、FS、SDIO、RNG时钟分频因子,取值4-15,分频后最高48M

PLL_VCO输出时钟 = (RCC_PLLSource/PLLM)*PLLN

SYSCLK = ((RCC_PLLSource/PLLM)*PLLN)/PLLP

OTG、FS、SDIO、RNG Clock = ((RCC_PLLSource/PLLM)*PLLN)/PLLN

所以要将系统时钟配置成120M则应设置参数(RCC_PLLSource_HSE,8,240,2,2);

在这里RCC_PLLConfig (RCC_PLLSource_HSE,8,240,2,2);

SYSClock = 8/8*240/2 = 120M

void RCC_ClockConfig(void) { RCC_DeInit(); RCC_HSEConfig( RCC_HSE_ON ); if(SUCCESS == RCC_WaitForHSEStartUp()) { RCC_HCLKConfig (RCC_SYSCLK_Div1); RCC_PCLK1Config (RCC_HCLK_Div1); RCC_PCLK2Config (RCC_HCLK_Div1); RCC_PLLConfig (RCC_PLLSource_HSE,8,240,2,2); //SYSClock = 8/8*240/2 = 120M RCC_PLLCmd(ENABLE); while(RCC_GetFlagStatus ( RCC_FLAG_PLLRDY) == RESET ) { } RCC_SYSCLKConfig ( RCC_SYSCLKSource_PLLCLK ); while(RCC_GetSYSCLKSource() != 0x08) { } } }

时钟信号可由PA8和PC9引脚输出查看。