如何生成HDL例化模板?

参考资料:

https://forums.xilinx.com/t5/Design-Entry/In-vivado-how-to-generate-instantiation-template/td-p/471962

《Xilinx FPGA 权威设计指南:基于Vivado 2018集成开发环境》/何宾编著 P87

在传统的ISE开发环境中,提供了从用户自己设计的Verilog HDL代码中生成HDL例化模板。但是在Vivado设计套件中不提供类似于ISE中的直接图形化例化模板的方法,需要使用Tcl命令才能从用户自己设计的Verilog HDL代码中生成HDL例化模板。

接下来以Vivado 2017.4设计套件为例。

1、定制Tcl脚本命令

定制Tcl脚本命令的步骤如下所示。

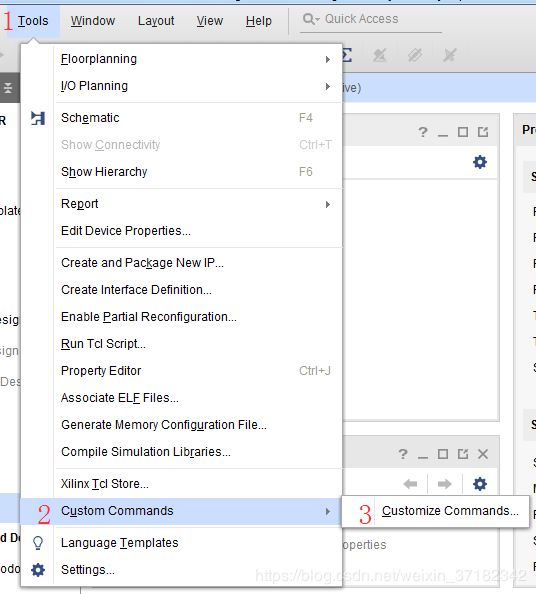

第一步:在Vivado当前设计主界面的主菜单下执行菜单命令【Tools】>>【Custom Commands】>>【Customize Commands】,出现“Customize Commands”对话框,如下图所示。

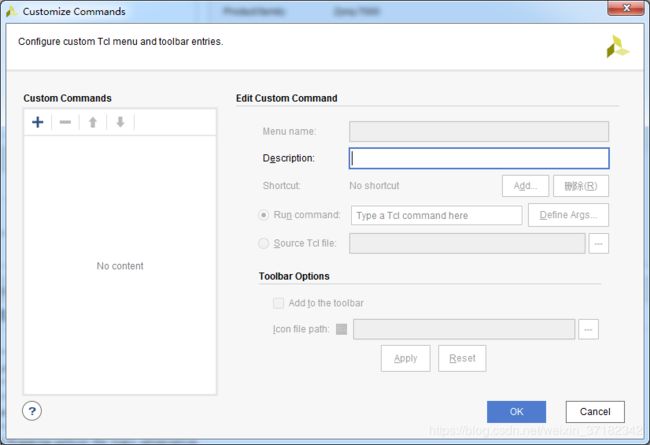

第二步:在“Customize Commands”对话框中单击【加号】按钮,出现浮动对话框,“提示Enter a menu name”信息。

第三步:在浮动对话框中,输入“generate hdl template”,作为定制Tcl命令的名字。

第四步:按【Enter】按键,第二步和第三步如下图所示。

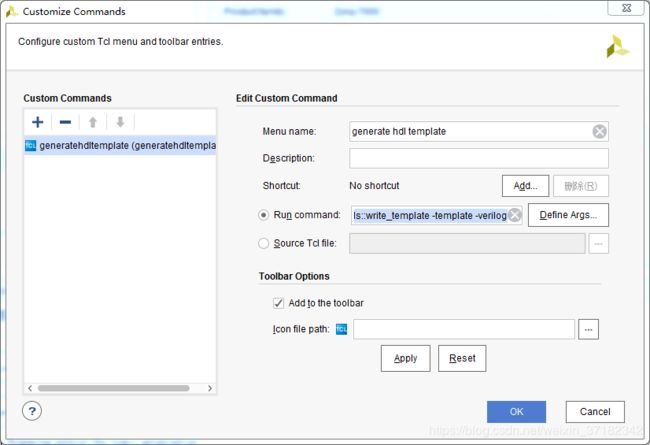

第五步:在“Customize Commands”对话框右侧的窗口勾选“Run command”前面的复选框;在右侧的文本框中输入

xilinx::designutils::write_template -template -verilog第六步:单击【OK】按钮,退出“Customize Commands”对话框。

此时,在Vivado主界面工具栏中出现TCL按钮。

2.生成顶层模板 的例化模板(*)

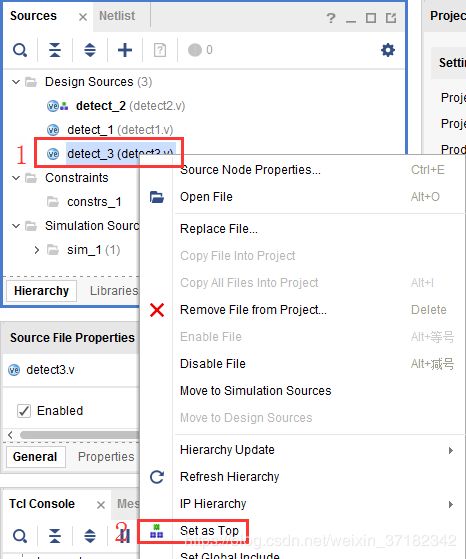

第一步:在Vivado当前设计界面的“Sources”窗口中找到并选择detect3.v文件(可根据自己的工程项目文件选择),单击鼠标右键。出现浮动菜单。在浮动菜单中,执行菜单命令【Set as Top】。

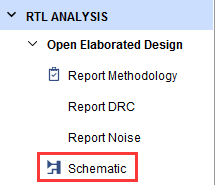

第二步:在Vivado当前设计界面左侧的“Flow Navigator”窗口中找到并展开“RTL ANALYSIS”选项。在展开项中,选择“Open Elaborated Design”(必须执行该步骤)。

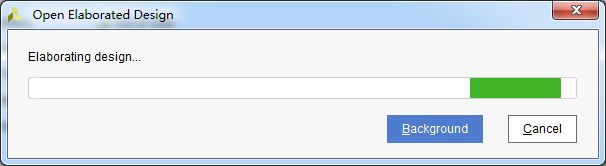

第三步:出现“Elaborate Design”对话框。

第四步:单击“OK”按钮。

第五步:Vivado自动打开详细描述后的top模块结构。在Vivado主界面的工具栏中单击【TCL】按钮。在Vivado主界面下面的“Tcl Console”控制台中,出现下面的消息。

xilinx::designutils::write_template -template -verilog

Creating verilog template for Module detect_3 in C:/Users/Bell/AppData/Roaming/Xilinx/Vivado/detect_3.v

0表示生成了detect_3模块的模板。

第六步:在“Tcl Console”控制台中的文本框内输入下面的Tcl脚本命令。

read_verilog C:/Users/Bell/AppData/Roaming/Xilinx/Vivado/detect_3.v第七步:按【Enter】按键,读取生成的detect_3.v模板。

第八步:在Vivado主界面的“Sources”窗口中,看到新生成了Non-module Files文件夹。在该文件夹中找到并双击detect_3.v文件,打开该例化模板。

经过以上步骤就可以生成HDL例化模板了,但是我个人感觉并不比手输省事,哈哈哈,希望Xilinx后期可以 优化以下这个功能。