Time Borrowing in Latches

Static Timing Analysis applies a concept called Time Borrowing for latch based designs.

This blog post explains time-borrowing, and is relevant to cases where your design has latches, and your timing report has time-borrowing.

Let us consider a clock of period 10, with a duty-cycle of 50%:

Let us also consider a simple circuit as follows:

For ease of understanding, let us assume that the setup and hold for each of the flops is “0”.

Also, assume that the clock skew and clock-delays are “0”.

The data that gets launched from F1 at time 0 gets sampled at F2 at time 10.

So, if data reaches F2 AFTER 10, F2 will not be able to capture the correct data.

Similarly, the data launched from F2 has 10 time-units to reach F3, where it will be sampled at the next clock edge.

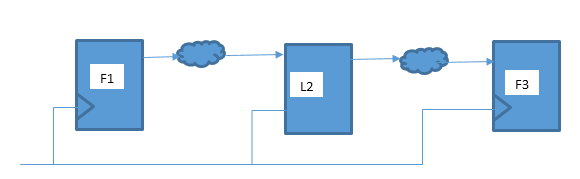

Now let us replace F2 with a latch: L2, where the “Gate” of the Latch is driven by the same clock line:

For the data launched from F1 at time 0:

If it reaches the latch input before 10, this data waits at the Latch’s D pin.

This is similar to the behavior exhibited by F2.

What happens however, when the data reaches L2 after 10?

L2 is “transparent” for the duration of 10 to 15.

So, even if the data reaches L2 after 10, L2 will be able to consume it as long as the data reaches L2 before 15.

This means that the data has up to 15 time-units to reach the Latch, instead of the 10 that it had with a flop.

For example, if the data reaches L2 at 12, this means that the latch has provided an advantage (over the flop) of 2 time-units.

The maximum advantage that L2 could provide is 5 time-units in this example.

Now, let us look at the path from L2 to F3.

The data comes out of L2 at 12, and will be sampled at F3 at time 20.

Thus, the path from L2 to F3 gets only 8 time-units.

In the circuit which had all flops, the second path had 10 time-units.

However in this circuit, it gets 2 time-units less.

In essence:

- The path feeding into the latch got 2 extra time-units.

- As a result, the path following the latch had to “give-away” these 2 time-units from its share (of 10 time-units).

Alternately stated: The path feeding into the latch “borrowed” 2 time-units from the path which is following the latch.

So, a path feeding into a latch CAN borrow additional time (equivalent to the time that the latch is transparent), from the following path.

The actual time borrowed though, need not be all that can be borrowed.

The actual time borrowed would be the minimum that is required for the path to meet timing (subject to a max limit of the latch being transparent).

For the example considered:

- The amount that CAN be borrowed = 5 time units.

- The amount actually borrowed = 2 time units.

10 units are available by default, and with an additional 2, the path of 12ns is able to meet timing.

It should be noted that the path from F1 to F3 still gets a total of 20 which has not changed.

Only the distribution has changed.

eg:

module top (d1, dout, clk, en);

input [8:0] d1;

output reg dout;

input clk;

input en;

reg [8:0] d1_reg ;

reg d2_reg;

always @ (posedge clk)

begin

if (en) begin

d1_reg <= d1;

dout <= comb2;

end

end

assign comb1 = ^ d1_reg;

assign comb2 = & d2_reg;

always @ (comb1 or clk)

begin if (clk)

d2_reg <= comb1;

end

endmodule