STM32通用IO口原理和八种IO口模式学习

1.GPIO基本结构

来自官网数据书册介绍:

Each of the general-purpose I/O ports has two 32-bit configuration registers (GPIOx_CRL,GPIOx_CRH), two 32-bit data registers (GPIOx_IDR, GPIOx_ODR), a 32-bit set/resetregister (GPIOx_BSRR), a 16-bit reset register (GPIOx_BRR) and a 32-bit locking register(GPIOx_LCKR).

Subject to the specific hardware characteristics of each I/O port listed in the datasheet, eachport bit of the General Purpose IO (GPIO) Ports, can be individually configured by software in several modes (STM32中GPIO的8种模式)

• Input floating

• Input pull-up

• Input-pull-down

• Analog

• Output open-drain

• Output push-pull

• Alternate function push-pull

• Alternate function open-drain

Each I/O port bit is freely programmable, however the I/O port registers have to beaccessed as 32-bit words (half-word or byte accesses are not allowed). The purpose of theGPIOx_BSRR and GPIOx_BRR registers is to allow atomic read/modify accesses to any ofthe GPIO registers. This way, there is no risk that an IRQ occurs between the read and themodify access.

2.八种IO口设置模式

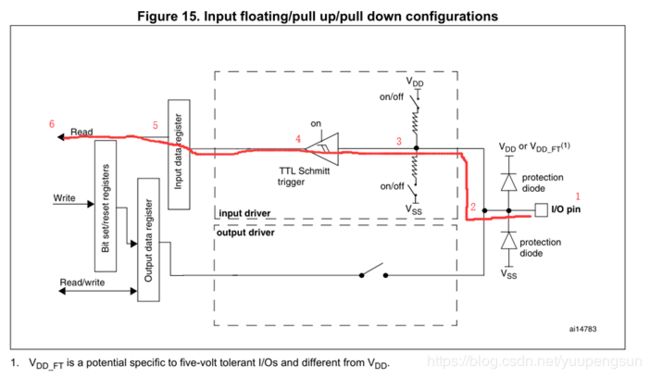

2.1.Input configuration (输入配置)

When the I/O Port is programmed as Input:

• The Output Buffer is disabled(输出缓冲器被禁止)

• The Schmitt Trigger Input is activated( Schmitt Trigger输入被激活)

• The weak pull-up and pull-down resistors are activated or not depending on inputconfiguration (pull-up, pull-down or floating): (根据输入配置(上拉,下拉或浮动)的不同,弱上拉和下拉电阻被连接,取决于3号位置的上拉和下拉电阻连接状态)

• The data present on the I/O pin is sampled into the Input Data Register every APB2 clock cycle(I/O脚上的数据在每个APB2时钟被采样到输入数据寄存器 5号位置)

• A read access to the Input Data Register obtains the I/O State.(CPU6号位置从5位置读出1号位置IO的状态信息)

2.1.1.Input floating(输入浮空)

这种模式比较简单,也就时CPU6号位置读取5号位置的数据,就可以知道1号位置IO的状态,

整个回路从1 --> 2 --> 3 -->4 --> 5-->6,是一条简单的通路。

VDD_FT 对5伏容忍I/O脚是特殊的,它与V DD 不同,

在芯片手册中查找带有FT标识的则就是可以识别5V信号的IO引脚。

2.1.2.Input pull-up(输入上拉)

3号位置上拉电阻连接,下拉电阻断开表示为输入上拉设置。

2.1.3.Input-pull-down(输入下拉)

和输入上拉相反,3号位置下拉电阻连接,上拉电阻断开表示为输入下拉设置。

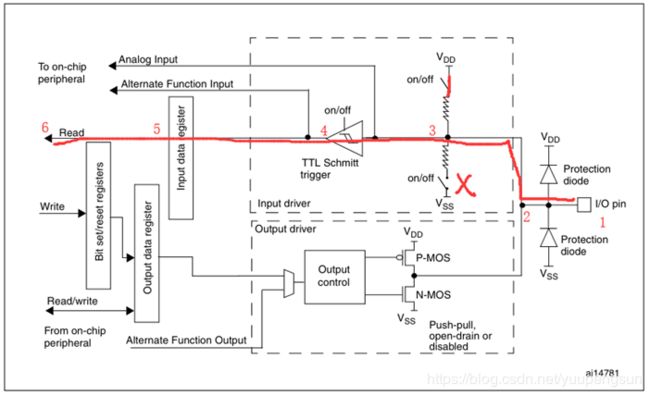

2.1.4.Analog configuration(输入模拟量设置)

When the I/O Port is programmed as Analog configuration:

• The Output Buffer is disabled. (输出缓冲器被禁止)

• The Schmitt Trigger Input is de-activated providing zero consumption for every analog value of the I/O pin. The output of the Schmitt Trigger is forced to a constant value (0).( 3号位置Schmitt Trigger输入被禁用,为I / O引脚的每个模拟值提供0值。 Schmitt Trigger的输出被强制为恒定值(0)也就是CPU5号位置从4号位置读出数据永远等于0)

• The weak pull-up and pull-down resistors are disabled.(在2号位置和3号位置之间的上拉下拉电阻无效)

• Read access to the Input Data Register gets the value “0”.( CPU5号位置从4号位置读出数据永远等于0)

真正的数据读出是从6号位置读出1号位置输入的模拟量值,模拟量值不同于数字量值的1和0,模拟量值是一个连续的数值集合,如:AD信号

2.2Output configuration(输出配置)

When the I/O Port is programmed as Output:

• The Output Buffer is enabled(6号位置输出缓冲寄存器被使能)

– Open Drain Mode(输出漏极开路): A “0” in the Output register activates the N-MOS while a “1” in the Output register leaves the port in Hi-Z. (the P-MOS is never activated) (5号位置输出0则激活4号位置的N-MOS, 3号位置P-MOS永远不会被激活,而且这种模式下IO口信号由1号位置的上拉下拉决定)

– Push-Pull Mode(推挽输出): A “0” in the Output register activates the N-MOS while a “1” in the Output register activates the P-MOS.(5号位置输出0则激活4号位置的N-MOS,当设置为1时候激活3号位置P-MOS)

• The Schmitt Trigger Input is activated.(11号位置的Schmitt Trigger会被激活)

• The weak pull-up and pull-down resistors are disabled. (在2号位置和11号位置之间的上拉下拉电阻无效)

• The data present on the I/O pin is sampled into the Input Data Register every APB2 clock cycle(意思就是CPU可以在9号位置从10号位置读取1号位置IO的电平状态)

• A read access to the Input Data Register gets the I/O state in open drain mode(对输入数据寄存器的读访问在漏极开路模式下获得I / O状态)

• A read access to the Output Data register gets the last written value in Push-Pull mode(对输出数据寄存器的读访问在推挽模式下获得最后写入的值)

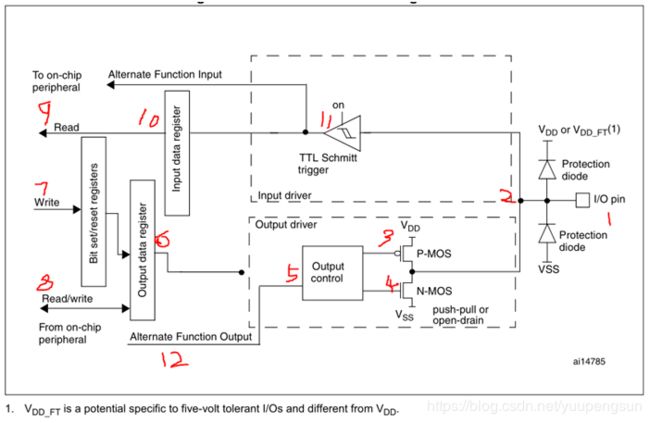

2.2.1.Output open-drain(输出漏极开路)

当7号位置写1,映射到输出寄存器ODR,然后到5输出控制器,这种模式会到4号位置,因为设置为1,则N-MOS截止,那么1号位置的状态由上拉和下拉决定。

当5号位置输出0,则4号位置N-MOS导通,那么1号位置会被N-MOS拉到Vss状态。

1号位置的状态可以被CPU在9号位置从10号位置读出。

2.2.2.Output push-pull(推挽输出模式)

这种模式和Output open-drain区别就是经过5号位置后会经过3号和4号位置来决定1号位置的状态。

5号位置输出1,则3号位置P-MOS会被导通,N-MOS会被截止,那么号位置会输出1状态。

5号位置输出0,则3号位置N-MOS会被导通, P-MOS会被截止,那么号位置会输出1状态。

同样1号位置的状态可以被CPU在9号位置从10号位置读出。

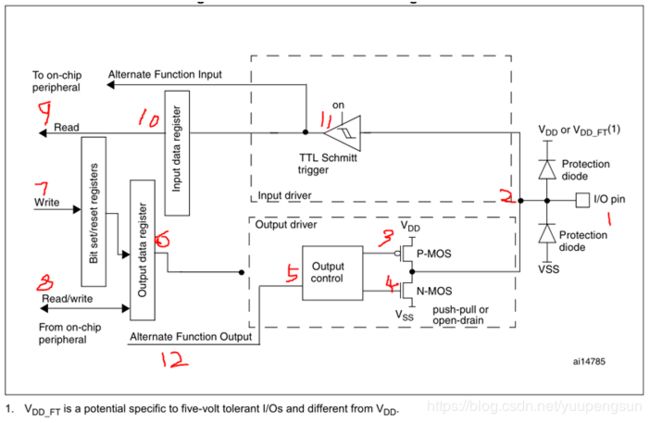

2.2.3.Alternate function push-pull(复用推挽输出模式)

这种模式和Output push-pull不同的是1号位置状态设置的源头来自于12号位置,复用功能的通信通道控制。

2.2.4.Alternate function open-drain(复用漏极开路输出)

这种模式和Output open-drain不同的是1号位置状态设置的源头来自于12号位置,复用功能的通信通道控制。

3.总结在1号位置的状态

推挽输出:

可以输出强高低电平,连接数字器件 ,输出状态由6号位置输出寄存器控制

开漏输出:

只可以输出强低电平,因为N-MOS会在输入0时导通,高电平得靠外部电阻拉高,因为N-MOS会在输入1时截止。输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20mA以内)

4.IO口相关的寄存器

/* 来自stm32f10x.h */

typedef struct

{

__IO uint32_t CRL;//端口配置低寄存器32位,4个位控制1个IO口

__IO uint32_t CRH;//端口配置高寄存器32位,4个位控制1个IO口

__IO uint32_t IDR;//端口输入寄存器32位

__IO uint32_t ODR;//端口输出寄存器32位

__IO uint32_t BSRR;//端口位设置/清除寄存器32位

__IO uint32_t BRR;//端口位清除寄存器16位

__IO uint32_t LCKR;//端口配置锁存寄存器32位

} GPIO_TypeDef;