逻辑门(Logic Gates)是集成电路设计的基本组件。通过晶体管或MOS管组成的简单逻辑门,可以对输入的电平(高或低)进行一些简单的逻辑运算处理,而简单的逻辑门可以组合成为更复杂的逻辑运算,是超大规模集成电路设计的基础。

最基本的逻辑门有三种,即“与”、“或”、“非”,其符号如下图所示:

至于它们的逻辑作用这里不再列出了,免得大家说编剧我灌水,为了显得我能勉强高逼格一点,我们仔细看看逻辑门芯片中有哪些信息值得我们关注,Follow me!

如果你仔细观察过74HC系列与、或、非逻辑器件数据手册(datasheet)的逻辑原理图(Logic Diagram),我们会发现上面三个门会是下图那样的:

我们利用以前教材上的知识来化简一下这三个组合逻辑,如下所示:

果然还是“与”、“或”、“非”逻辑,有心人可能立马就发现其中的奥秘:这些逻辑全都被表达成“与非”、“或非”!原来以前在学校做的那些将逻辑表达式化成“与非”、“或非”的题目在这里就有呀,真是学以致用呀,我太兴奋了,我太有才了,我太…

打住,今天我来这不是让你来做这些简单的表达式化简,而是想问你们两个问题:

(1)为什么这么简单且基本得不能再基本的逻辑运算要做得这么复杂?或者换句话说,为什么学校的书本上有那么多将逻辑表达式化成“与非”、“或非”的题目?

(2)为什么插入那么多非门?好像不要钱似的!

这两个问题涉及到集成电路的设计,我们首先来看看在CMOS集成电路设计中是如何将这三个逻辑设计出来的,如下图所示的“非门”逻辑构造:

上面带圆圈的是PMOS晶体管,下面是NMOS晶体管,从开关的角度来看,PMOS管相当于PNP三极管,输入为“1”时截止,输入为“0”时导通;而NMOS则相当于NPN三极管,输入为“1”时导通,输入为“0”时截止(这个比喻可能不太合适,但你可以这么去理解这个开关行为,因为相对于MOS管,可能更多人对三极管更熟悉,如果不是的话,可以忽略这个比喻)。

当输入为“0”时,下面的NMOS截止,而上面的PMOS导通将输出拉为高电平,即输出“1”。当输入为“1”时,上面的PMOS截止,而下面的NMOS导通将输出拉为低电平,即输出“0”,很明显,这就是个“非门”逻辑。

OK,我们再看看“与非门”逻辑的结构:

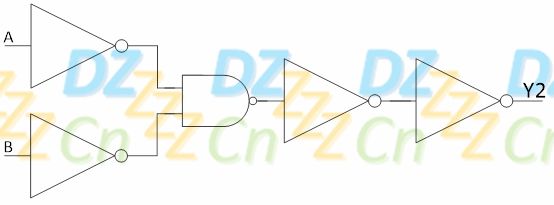

当上图中的任何一个输入(A或B)为低时,都将有一只PMOS导通,从而将输出Y拉高,因此该电路是“与非门”逻辑,那么“与门”逻辑就是在“与非门”后面加一级“非门”了,如下图所示:

有些人就会叫起来:编剧你脑残了,这不是乱盖吗?我下面设计的电路不是更省逻辑吗?

你自己看看,只有当输入A与B都为高电平时,输出Y才被上拉为高电平,而只要有任何一个输入为低电平时,输出Y就被拉为低电平,不是吗?我太有才了!你们电子制作站微信订阅号的老师水平真是太差了!

但是,对MOS管有较深理解的人都会知道,NMOS可以高效传输低电平,而PMOS可以高效传输高电平,两者配合可以达到轨对轨输出,而相反却不可以(会有损耗),因此你设计的逻辑电路从书本上看是合格的,但实际应用中不会有这种电路。

这样你发现了什么没有?在CMOS集成电路设计中,构建一个“与门”逻辑竟然比“与非门”逻辑还要多花费两个MOS晶体管,CMOS门在本质上是反相位的,也就是说每一个基本的逻辑门都自带了一个逻辑非,所以说,在学校里老师让你将复杂的表达式化成“与非”或“或非”逻辑,不仅仅是让你考试拿分的一道题,而是在CMOS集成电路设计当中,用“与非”、“或门”这样的设计可以充分地利用CMOS门本身的“逻辑非”。

这么一个“与门”逻辑与“与非门”逻辑之间的差距虽然仅有两个MOS管,但是在成千上万的大规模集成电路设计时(如奔腾处理器),省下来的面积就非常可观了。

下面是“或非门”逻辑的结构,读者有兴趣可以推导一下

你可能认为这只是巧合而已,那你可以看看更复杂的逻辑芯片的逻辑原理图,大多数都是用“与非门”、“或非门”、“非门”,当然,有些也不是,毕竟只是上层的逻辑原理框图,但是底层的CMOS实现肯定是一样的

这样第一个问题就已经解答了,那么第二个问题呢?首先要说的是:插入的非门肯定是要花钱的,但是既然这么做,就一定有道理。有人说输入插入非门是为了整形,输出插入非门是为了增强带负载能力,难道“与非门”或“或非门”的带负载能力会比“非门”差?都是一样的构造,只有“非门”可以对输入电平进行整形?

其实插入“非门”的主要目的是为了提升速度,即优化逻辑门的延时!虾米?编剧你这次又被我抓到了吧?我插入两个非门就多了两级逻辑,不就更慢了吗?地球人都知道呀!

But,我只想告诉你,这只是一般人的想法(我们是高逼格的人JJ),大多数人都会认为每一级逻辑都有一个“门延时”,因此会通过计算总的逻辑级数来计算总的延时,也就是说,逻辑级数越少的电路就是速度最快的,然而,门延时实际上取决于电气努力(这个不好解释,知道这个名词就行了),所以采用较少的逻辑级数往往会导致更大的延时(这有点类似时序逻辑的“流水线”结构)。

CMOS集成电路设计里有一个“最优级数”的概念,不是这个专业的不需要深究,我们只举个最简单的例子就可以说明白这个问题,如下图所示:

这三个“非门”逻辑当中哪个延时最小呢?你可能认为是第一个,但实际上第二个方案是延时最小的,这就解释了:为什么这些厂家都不要钱似的插入“非门”逻辑了吧?插入这么多的“非门”就是为了获得更快的速度,然后卖个更好的价钱,正所谓:天下熙熙,皆为利来;天下攘攘,皆为利往,这个道理永远是正确的,在集成电路设计里也不例外。

好的,本节就此结束了,下一节我们谈谈逻辑电平,想听的记得带上板凳呀

原文链接点击这里