【应用笔记】用Cyclone V FPGA配置AD9361

更多精彩内容,请微信搜索“FPGAer俱乐部”关注我们。

传统的射频收发器硬件架构由分立的LNA,Mixer,VGA,ADC/DAC,IQ调制器和射频频综等芯片组成。AD9361是一款面向3G和4G基站应用的高性能、高集成度的射频RF Transceiver。该器件的可编程性和带宽能力使其成为多种收发器应用的理想选择。单一芯片最大可完成2T2R通道的射频及中频处理。

Intel FPGA作为一种可编程逻辑器件,具有丰富的逻辑资源包括嵌入式存储器,数字信号处理模块,高速收发器,高速IO管脚等,可以方便实现各种外围器件的配置和数字信号处理。.

本文介绍采用cyclone V FPGA完成9361的配置,在 FPGA中通过SPI接口完成对 AD9361一系列寄存器的配置,从而使得 AD 9361 在配置的模式和参数下正常工作。

AD9361评估软件配置说明

AD9361的配置是通过SPI接口读写内部寄存器实现,而寄存器配置参数包含在AD9361评估软件release出的InitScrip文件中。

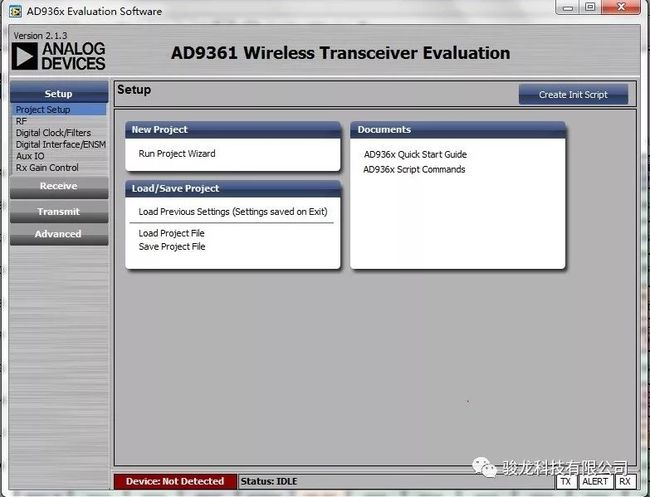

1、打开9361评估软件如下图所示

2、点击Run ProjectWizard,弹出的界面可以选择射频输入输出口,本设计中单芯片实现 1T1R,均选择 2A端 口,根据板卡原理图的设计配置如下:

3、点击Next,进行参考时钟设置,本方案外部时钟30.72M(19~50M)连接至XTAL_N,为了达到最佳性能,BBPLL和TX/RX SYNTH的参考输入时钟范围是35~80M,所以BBPLL Input Scale和RFPLL Input Scale均为2x,本方案没有使用DCXO,可以不用设置。

4、点击Next,进入下一界面。设置接口速率和通道带宽,如果要设计的带宽和数据速率相同,用户可以直接使用Standard里的模板,也可以选择Cutom自定义参数。在自定义的情况下,输入接口数据速率和通道带宽后,软件会自动得出ADC CLK和DAC CLK,以及相应的抽取插值倍数。需要注意的是ADC CLK范围是10.5M~672M,在不超过范围的情况下,ADC CLK的频率越高越好。本方案收发数据速率为30.72M,参考设计中TX,RX射频带宽为18M,用户可根据自身使用情况进行修改。

5、点击Next进入RX滤波器参数设置界面。只要在上个界面中设定好接口数据速率和带宽,软件会自动设置好滤波器参数。红线为模拟滤波器响应,绿线为数字滤波器响应,白线为两者级联的响应。其中数字滤波器的系数由用户根据自己需求通过matlab生成。

6、点击Next进入TX滤波器参数设置界面,与RX滤波器参数设置相同。

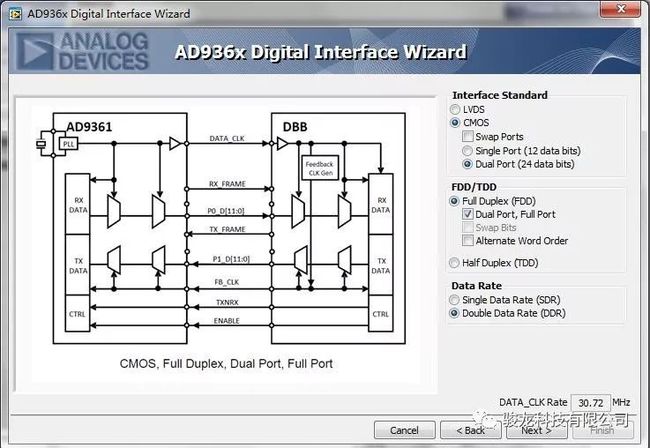

7、点击Next进入数字接口设置界面,本方案硬件采用CMOS,Dual Port FDD全双工模式(收发各12比特),双边沿采样。

8、点击Next进入接口相关设置界面。下图中上方的相关设置可以取反时钟相位,交换IQ顺序,交换通道,推荐不更改。下方的Delay Cell Control可以调整数据管脚和时钟之间的延时,从而得到一个好的采样窗口。

9、点击Next进入ENSM设置界面,可以对TDD/FDD进行设置。参考设计中设置为FDD模式,ENABLE和TXNRX独立控制收发。

10、点击Next进入增益控制设置界面,可以设置为AGC自动模式,也可以设置为MGC手动模式。推荐用户在前期测试自己的板卡时设置为MGC模式,参考设计中采用MGC模式。

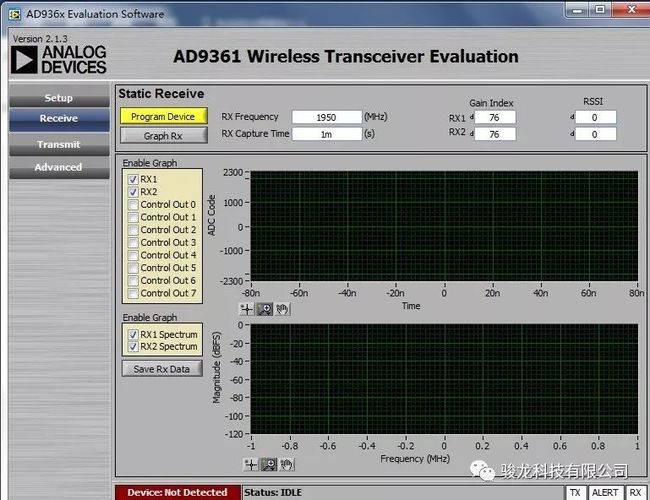

11、点击Finish,回到主界面。然后点击左边Receive,设置接收本振,参考设计中默认设置为1950M,也可在程序中通过ISSP动态修改。右上方可以设置初始增益值,也可在ISSP中实时修改。

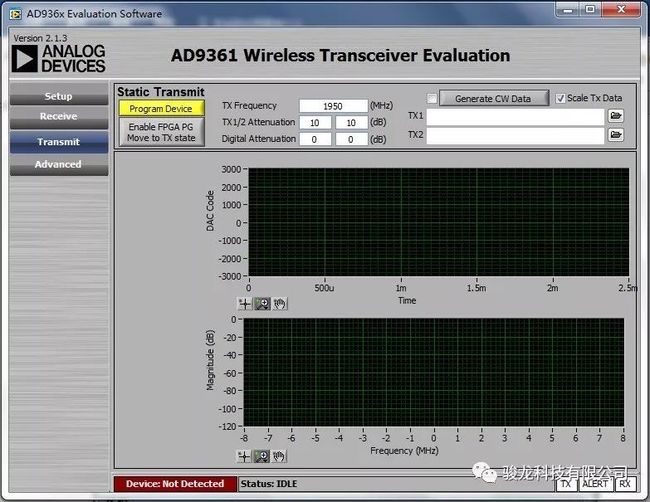

12、点击左方的Transmit,设置发射本振,参考设计中的默认频率为1950M,也可通过ISSP实时修改。TX1/2Attenuation可以设置TX端的初始衰减值(0~89.75dB),也可在ISSP中动态修改。

13、设置完成后回到主界面,在此界面可以保存和读取该软件的project文件。点击右上角的Create Init Script,在随后弹出的小窗口选择Low Level Scripting(文件保存类型选择为.txt)可以生成对应当前配置的完整配置参数文本。

14、生成的寄存器配置文件.txt 格式如下,可以明确看出配置流程。

FPGA 设计流程

FPGA 内部主要完成三大功能,分别是 AD 9361 配置,收发数据处理和外部功放的配置。

AD 9361 配置

根据上述 AD9361 软件配置流程14中生成的 Init Scrip文件,将 AD9361的配置流程通过22个状态机来实现,分别为IDLE→(CONFIG_PART1)→BBPLL SET(CONFIG_PART2)→TX FILTER SET(CONFIG_PART3)→RX FILTER SET(CONFIG_PART4)→PARALLEL PORT SET(CONFIG_PART5)→AUXDAC AUXADC SET(CONFIG_PART6)→CONTROL OUT SET(CONFIG_PART7)→GPO SET(CONFIG_PART8)→ENSM SET(CONFIG_PART9)→RFVCO SET(CONFIG_PART10)→MIXER SUBTABLE SET(CONFIG_PART11)→RX GAIN TABLE(CONFIG_PART12)→RX MANUAL SET(CONFIG_PART13)→RX BB FILTER TUNE SET(CONFIG_PART14)→TX BB FILTER TUNE SET(CONFIG_PART15)→RX TIA SET(CONFIG_PART16)→TX 2NDFILTER SET(CONFIG_PART17)→ADC TUNE SET(CONFIG_PART18)→TX QUAD CAL SET(CONFIG_PART19)→TX ATT SET(CONFIG_PART20)→RSSI POWER MEASURE SET(CONFIG_PART21)→END ENABLE SET(CONFIG_PART22).

一般工作模式下,以上状态机均根据 Init Scrip文件中寄存器配置流程和顺序进行跳转,每个状态里面实现本模块的寄存器配置,而且每个状态模块内部也是通过状态机实现,基本结构为 RESET→CONFIGURE DATA→WAIT→END ,有些模块内部包含延迟等待的信息,需要有 WAIT 状态。

2. 收发数据处理

FPGA 和 AD9361 之间采用 CMOS Dual PORT全双工模式,双边沿采样DDR。即 FPGA 和 AD9361 之间收发均为12bit并行数据,DDR模式。因此在 FPGA 内部需要实现 DDR 数据和 SDR 数据的转换。具体地,发射端由NCO 产生 CW 信号,频率可通过频率控制字实时改变。产生的 CW 信号先经过数字增益模块,然后通过 DDRIO 模块转换成 DDR 格式输出给 AD9361。接收端通过 DDRIO 将接收到的 AD9361 数据转换成 SDR 格式后,通过 RX FRAME 信号将 IQ 分开。

============华 丽 的 分 割 线============

想加入我们FPGA学习交流群吗?可以长按或扫描以下二维码,审核通过后我们邀请您加入。

这些微信群旨在打造一个提供给FPGA工程开发人员及兴趣爱好者(统称“FPGAer”)进行技术交流、答疑解惑和学习的平台。而且我们也将会通过网络举办一系列的FPGA技术讲座,分享一系列相关研究文献,举办一系列交流研究成果的学术活动。

![]()

了解更多FPGA知识可以长按或扫描以下二维码关注“FPGAer俱乐部”。