Xilinx 7系列SelectIO结构之IO标准和端接匹配(二)

引言:本文继续介绍Xilinx 7系列FPGA SelcetIO电平标准及相关端接匹配电路。具体内容包括:

- LVDCI电平标准

- LVDCI_DV2电平标准

- HSLVDCI电平标准

- HSTL电平标准

1. LVDCI电平标准

图1、LVDCI I/O可用的bank类型

LVDCI接收器本质上和LVCOMS接收器一样。7系列器件HP I/O提供可控阻抗输出驱动器以匹配串行端接,而不需要外部源端电阻。阻抗通过外部公共的参考电阻进行设置,阻抗等于传输线特征阻抗。DCI I/O标准支持LVDCI_15和LVDCI_18标准。

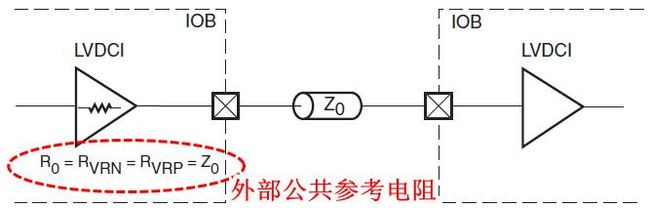

图2显示了单向LVDCI I/O标准可控阻抗驱动器拓扑。

图2、单向LVDCI I/O标准可控阻抗驱动器拓扑

图3显示了双向受控阻抗驱动器拓扑。

图3、双向受控阻抗驱动器拓扑

2. LVDCI_DV2电平标准

具有半阻抗(源端接)的受控阻抗驱动器也可以为驱动器提供参考电阻的一半阻抗。这需要将外部公共参考电阻值增大到2倍,这样可以降低通过VRN和VRP的静态功耗。该I/O标准支持LVDCI_DV2_15和LVDCI_DV2_18电平。

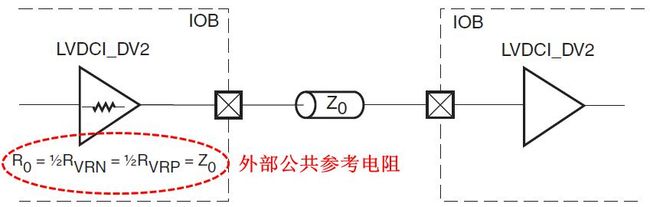

图4举例了使用阻抗拓扑的单向受控阻抗驱动器。

图4、使用阻抗拓扑的单向受控阻抗驱动器

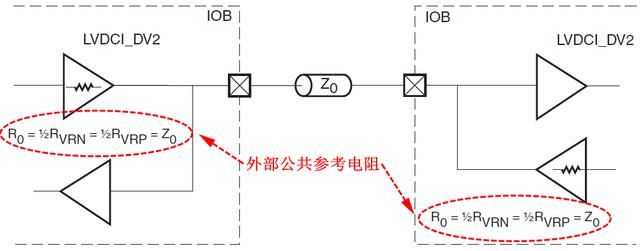

图5举例了使用阻抗拓扑的双向受控阻抗驱动器。

图5、使用阻抗拓扑的双向受控阻抗驱动器

LVDCI驱动器没有可选的电流驱动强度设置。当驱动器阻抗是VRN/VRP参考电阻的一半时,通过在属性名中添加DV2来指示。

3. HSLVDCI(高速LVDCI)电平标准

图6、HSLVDCI I/O可用的bank类型

HSLVDCI标准用于双向管脚中。驱动器和LVDCI标准一样,输入与HSTL和SSTL一样。通过使用VREF参考输入,HSLVDCI允许在接收器处比使用单端LVCMOS类型接收器具有更大的噪声余量。该标准支持HSLVDCI_15和HSLVDCI_18电平标准。

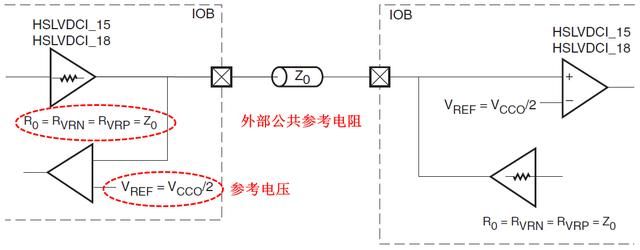

HSLVDCI受控阻抗驱动器双向端接拓扑如图7所示。

图7、HSLVDCI受控阻抗驱动器双向端接拓扑

4. HSTL(高速收发器逻辑)电平标准

HSTL标准是一种一般的高速总线标准,由JEDEC制定,HSTL标准有四种变体(类别)。为了支持时钟高速存储器接口,差分版本也可用。7系列FPGA I/O支持HSTL 1.2V Class-I和1.5V/1.8V Class-II以及差分版本标准。

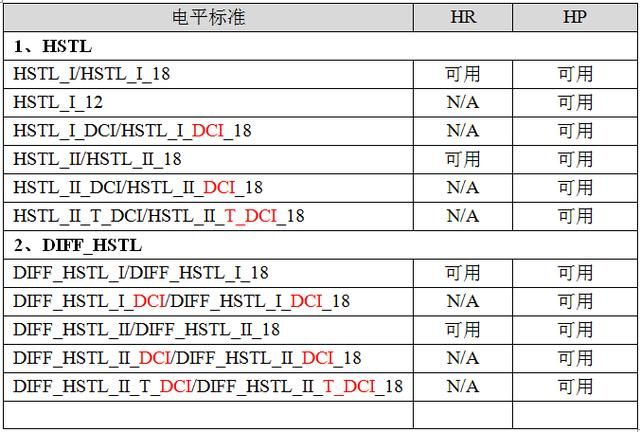

图8、HSTL标准可用I/O Bank

4.1 HSTL Class I(1.2V、1.5V和1.8V)

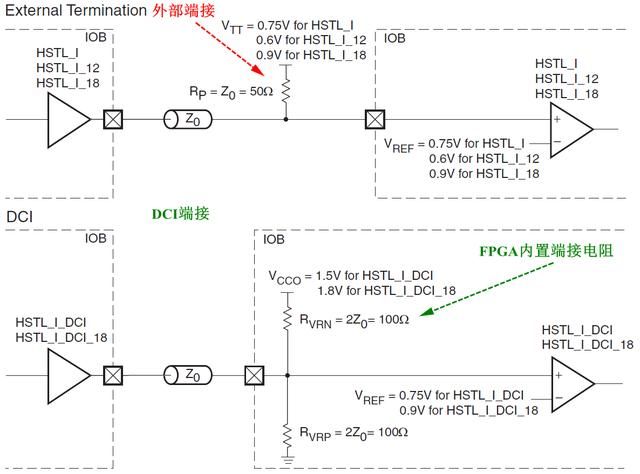

图9显示了HSTL Class I(1.2V、1.5V或者1.8V)端接电路技术。在特殊电路中,所有驱动器和接收器必须保持在相同电压电平(1.2V、1.5V或者1.8V)。只有HP I/O banks支持DCI标准。

图9、HSTL Class I(1.2V、1.5V和1.8V)端接

4.2 差分HSTL Class I

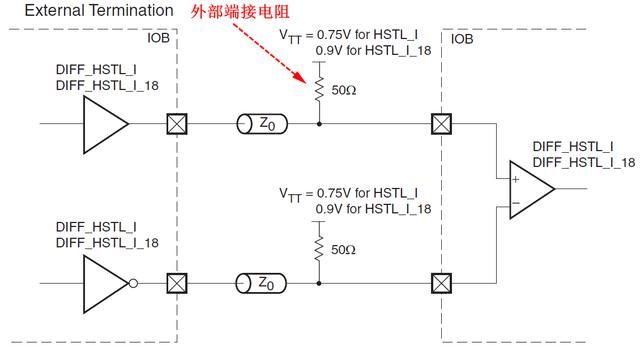

图10显示了差分HSTL Class I(1.5V或1.8V)单向端接技术。在特殊电路中,所有驱动器和接收器必须保持在相同电压电平(1.5V或1.8V)。

图10、差分HSTL Class I(1.5V或者1.8V)单向端接

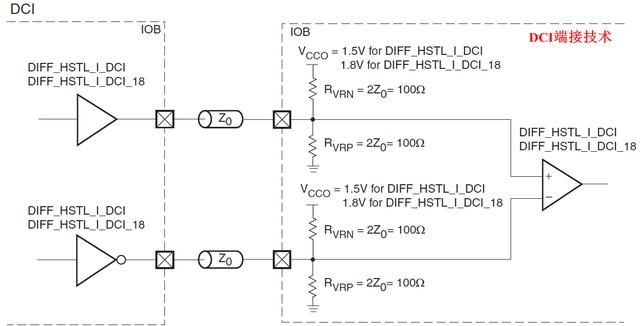

图11显示了HP I/O banks 差分HSTL Class I单向端接技术。

图11、差分HSTL Class I单向DCI端接技术

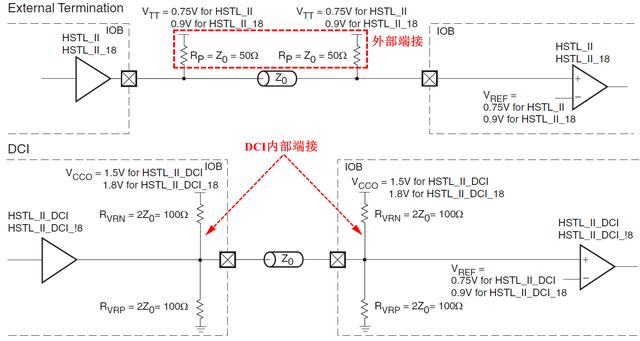

4.3 HSTL Class II

图12显示了HSTL Class II(1.5V或者1.8V)端接电路技术。在特殊电路中,所有驱动器和接收器必须保持在相同电压电平(1.5V或者1.8V)。只有HP I/O banks支持DCI标准。

图12、HSTL Clas II(1.5V或者1.8V)单向端接

图13显示了HSTL Class II(1.5V或者1.8V)双向端接。

图13、HSTL Class II(1.5V或者1.8V)双向端接

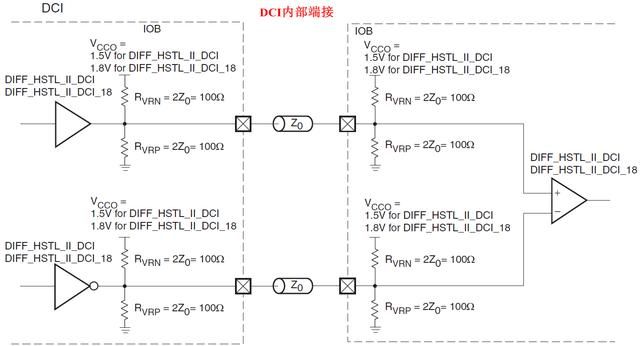

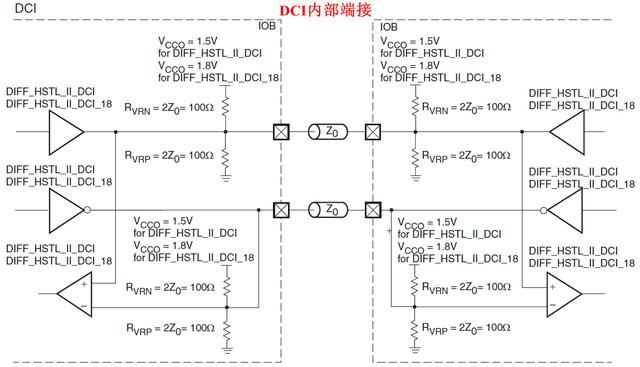

4.4 差分HSTL Class II

图14显示了差分HSTL Class II(1.5V或者1.8V)单向端接。

图14、差分HSTL Class II(1.5V或者1.8V)单向端接

图15显示了差分HSTL Class II(1.5V或者1.8V)DCI单向端接。

图15、差分HSTL Class II(1.5V或者1.8V)DCI单向端接。

图16显示了差分HSTL Class II(1.5V或者1.8V)双向端接。

图16、差分HSTL Class II(1.5V或者1.8V)双向端接。

图17显示了差分HSTL Class II(1.5V或者1.8V)DCI双向端接。

图17、差分HSTL Class II(1.5V或者1.8V)DCI双向端接。

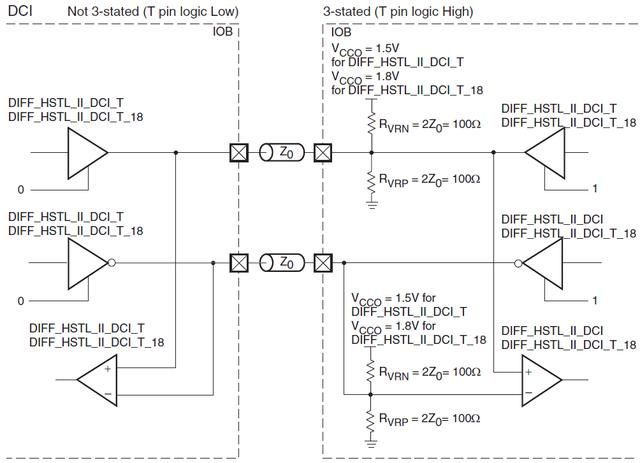

4.5 HSTL_II_T_DCI(1.5V或1.8V)分立戴维宁端接(三态)

图18显示了HSTL_II_T_DCI(1.5V或1.8V)分立戴维宁端接。

图18、HSTL_II_T_DCI(1.5V或1.8V)分立戴维宁端接。

图19显示了差分HSTL_II_T_DCI(1.5V或1.8V)分立戴维宁端接。

图19显、差分HSTL_II_T_DCI(1.5V或1.8V)分立戴维宁端接

更多其他技术文章可以关注我的公众号“FPGA技术实战”,欢迎交流 !