ARM平台处理器简介

1.总体情况

先从ARM的wiki上抄个表过来:

| Architecture | Family |

| ARMv1 | ARM1 |

| ARMv2 | ARM2,ARM3 |

| ARMv3 | ARM6,ARM7 |

| ARMv4 | StrongARM,ARM7TDMI,ARM9TDMI |

| ARMv5 | ARM7EJ,ARM9E,ARM10E,XScale |

| ARMv6 | ARM11, Cortex-M |

| ARMv7 | Cortex-A,Cortex-M,Cortex-R |

| ARMv8 | - |

左侧的一列可以视作是ARM处理器的各个“代”,而右侧则是同一代的各个“家族”(或者说“系列”)。现在基本已是ARMv7的时代,ARMv6及更早的Architecture只在一些低端的设备上能见到了。而ARMv8则是ARM平台的未来时,被设计为64位的架构,显然不是主要面向移动设备的。不过到现在为止ARMv8也只是有一些资料,离真正面世还有一段时间。

现在把重点放在ARMv7,更确切的,是ARMv7中的Cortex-A系列核心上来。Cortex-M系列处理面向嵌入式应用,而Cortex-R系列则面向实时应用,Cortex-A,则面向广大的手机用户。

2.Cortex-A系列的众多核心们

| 核心 | Cortex-A5 | Cortex-A7 | Cortex-A8 | Cortex-A9 | Cortex-A15 |

| 发布年份 | 2009年 | 2011年 | 2006年 |

2007年 | 2011年 |

| 核心 | 1-4核 | 1-4核 | 单核 |

1-4核 | 最多4核每cluster,每物理核最多2个cluster |

| 流水线 | 8级(in-order) |

8-10级 | 13级(整点 in-order) |

8级(out-of-order) | 12级in-order加3-12级out-of-order |

| 硬件虚拟化 | 否 | 是 | 否 | 否 | 是 |

| L1 Cache | 4-64K/4-64K | 8-64K/8-64K | 16-32K/16-32K | 16-64K/16-64K | 32K/32K |

| 大物理地址扩展 | 否 | 是 | 否 | 否 | 是 |

| 浮点部件 | VFPv4 | VFPv4 | VFPv3 | VFPv3 | VFPv4 |

*发布年份是ARM公布核心的时间(可能不太准确)。

*A15的流水线前12级是in-order的,后面则是out-of-order的多种流水线,级数从3到12不等。A7类似,NEON部件的流水线是10级,整点则是8级。

现在来分析一下各个核心的参数。首先是Cortex-A后面的编号,大体上,这个编号代表该核心的性能,或者说在ARM产品线中的位置。比如A5面向低端应用,编号最小;A15是目前ARMv7性能中性能最高的核心;A7虽然发布晚于A8,而且规格接近,但由于限制了双发带宽,其性能预期是低于A8的。总的来看,A5的定位最低端,取代ARMv7之前的产品;A15最高端,A7性能低于A8,但更加节能,成本也更低;A8/A9则可能被取代,不过目前仍然是主流;A15则是目前为止ARM处理器中规格最高的了。

再看一下较新的核心中几个重要的特性。A7和A15支持硬件虚拟化,以A7的定位来说硬件虚拟化的支持似乎没有太多用武之地,不过对于A15来说则表明A15可能用于传说中的ARM服务器(不过算算时间似乎也没有太多A15发挥的余地,毕竟64位的ARMv8更适合用于服务器)。大物理地址扩展(LPAE)和x86上的PAE相似,允许32位的ARM处理器最大寻址2^40bit的内存(1TB)。这又是一个表明A15可用于服务器的迹象,毕竟4G的寻址空间对现在的服务器来说完全不够用啊。

3.浮点和高级SIMD部件

ARMv7开始使用VFPv3版本的浮点部件,而ARMv7中更新的核心则使用了VFPv4( 见前面表格)。VFPv2则用于ARMv7之前的核心,现在还有一部分低端手机使用这种处理器;而使用VFPv1浮点部件的核心已经基本淘汰掉了。ARM的高级SIMD部件称为NEON,从ARMv7开始出现

ARM浮点部件的一个问题是对很多核心来说是可选的,一些处理器并没有浮点部件。不仅如此,尽管ARMv7的处理器基本都实现了浮点部件,但浮点部件也有多个可选实现,再加上NEON部件也是可选的,最后导致市面上的ARM处理器对浮点/SIMD的支持并不一致。下表列出了主要的VFPv3实现的版本(VPFv4的资料需要补充):

| 版本 | 寄存器 | 其他特性 |

| VFPv3(-D32) | 32个64位寄存器,32个32位寄存器 | |

| VFPv3-FP16 | 同上 | 半精度扩展(FP16的含义) |

| VFPv4(-D32) | 同上 | VFPv4总是实现半精度扩展和Fused Multiply-Add 扩展 |

| VFPv3-D16 | 16个64位寄存器,32个32位寄存器 | |

| VFPv3-D16-FP16 | 同上 | 半精度扩展 |

| VFPv4-D16 | 同上 | 同VFPv4 |

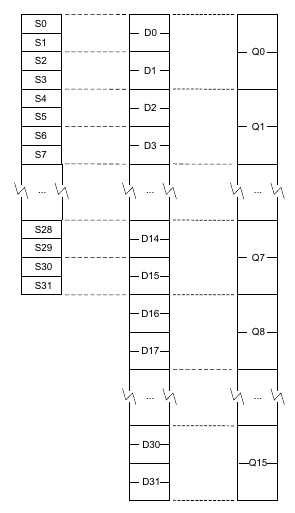

上表中所说的32位寄存器和64位寄存器并不是独立的,前16个64位寄存器每个可以视为2个32位寄存器,同时,两个64位寄存器可以视为一个128位寄存器。下图来自ARM官方文档,展示了32位寄存器和64位寄存器的关系:

对于VFPv3-D16、VFPv3-D16-FP16和VFPv4-D16来说,上图中的D16~D31是不存在的。除了上表中的版本,VFPv3还有单精度版本,只实现了单精度浮点数的运算指令,gcc中称这种版本的VFPv为“vfpv3xd”,相应的,还有vfpv3xd-fp16。不过这种实现的ARM处理比较少见。

NEON部件和浮点部件关系密切,在两者同时存在时,使用的是同一套寄存器。不过,NEON的寄存器数目是固定的,和VFPv3/VFPv-FP16/VFPv4相同。这意味着,NEON不能和VFPv3-D16/VFPv3-D16-FP16这种寄存器阉割版共存。当没有浮点部件时,NEON部件只能进行整点运算。下表是NEON和VFP部件可能的组合:

| NEON部件 | VFP部件 | 说明 |

| 仅整型 | 未实现 | |

| 整型和单精度浮点 | 单精度浮点 | |

| 整型和单精度浮点 | 单精度和双精度浮点 | |

| 未实现 | 单精度浮点 | |

| 未实现 | 单精度和双精度浮点 |

从上面这个表可以看出,即使VFP部件实现了双精度运算的功能,NEON部件也只能进行单精度运算。不止如此,gcc的手册之处,NEON的浮点运算不完全符合IEEE 754标准,在某些情况下会损失精度,因此即使使用了自动向量化的选项,浮点运算的向量化默认也是关闭的。

依据半精度和Fused Multiply-Ad扩展的实现情况,NEON部件可以分为3种版本:

高级SIMDv1:两者均未实现

高级SIMDv1带半精度扩展:实现了半精度扩展

高级SIMDv2:同时实现了半精度和Fused Multiply-Ad扩展

而NEON半精度和Fused Multiply-Ad扩展的实现情况与VFP部件是相关的。

总结一下VFP和NEON的特点:

1.VFPv3/VFPv4分为根据寄存器情况分为D16和D32两个版本,D16的双精度(64位)寄存器只有16个。

2.D16版本的VFP不能和NEON部件共存。

3.NEON部件单独存在时只能进行整点运算

4.实现了半精度扩展的VFPv3称为FP16版本,如果连Fused Multiply-Ad扩展也实现了,就是VFPv4了。

除了上面所说的,ARMv7处理器还有很多特性。由于我了解的不多,就不多说了