SDSoC软硬件协同设计流程系列——4.搭建SDSoC Platform

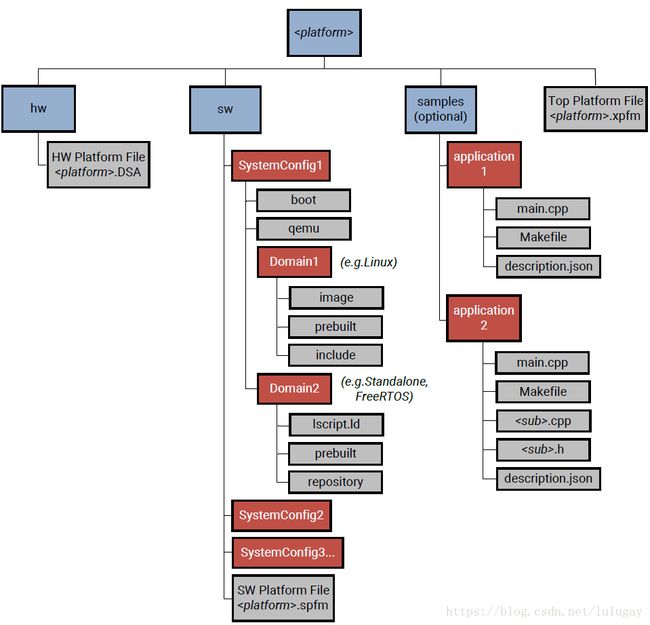

SDSoC Platfrom定义了基本的硬件和软件架构以及应用程序的运行环境,本节从硬件和软件两方面,介绍SDSoC Platform如何在SDSoC中被调用然后说明如何搭建自己的SDSoC Platform。一个SDSoC Platform应该包含如下文件:

- 硬件文件夹,里面包含Device Support Archive file,DSA文件定义了Zynq的PL部分, 在编译时SDSoC利用DSA文件包含的信息重新构建硬件工程,并以此为基础舔加算法加速器。

- 软件文件夹,包含

- 系统配置和处理器域,定义了系统启动顺序以及每颗CPU上运行的操作系统

- 启动相关文件,如fsbl.elf,u-boot.elf,如果是linux系统还需要提供设备树,内核,ramdisk或image.ub(设备树,内核,ramdisk的集合)启动相关文件,如fsbl.elf,u-boot.elf,如果是linux系统还需要提供设备树,内核,ramdisk或image.ub(设备树,内核,ramdisk的集合)

- Prebuild Hardware(可选),包括了比特流,.hdf等文件,如果程序里没有硬件加速函数,SDSoC将跳过调用Vivado生成比特流的步骤直接使用预先生成的文件以加快编译速度。Prebuild Hardware(可选),包括了比特流,.hdf等文件,如果程序里没有硬件加速函数,SDSoC将跳过调用Vivado生成比特流的步骤直接使用预先生成的文件以加快编译速度。

- 库的头文件以及静态库(可选)库的头文件以及静态库(可选)

- Metadata文件,用来组织上面提到的文件Metadata文件,用来组织上面提到的文件

- Sample Application(可选)Sample Application(可选)

SDSoC Hardware Platform

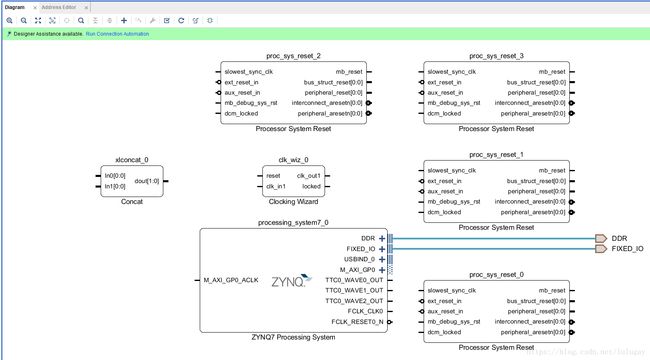

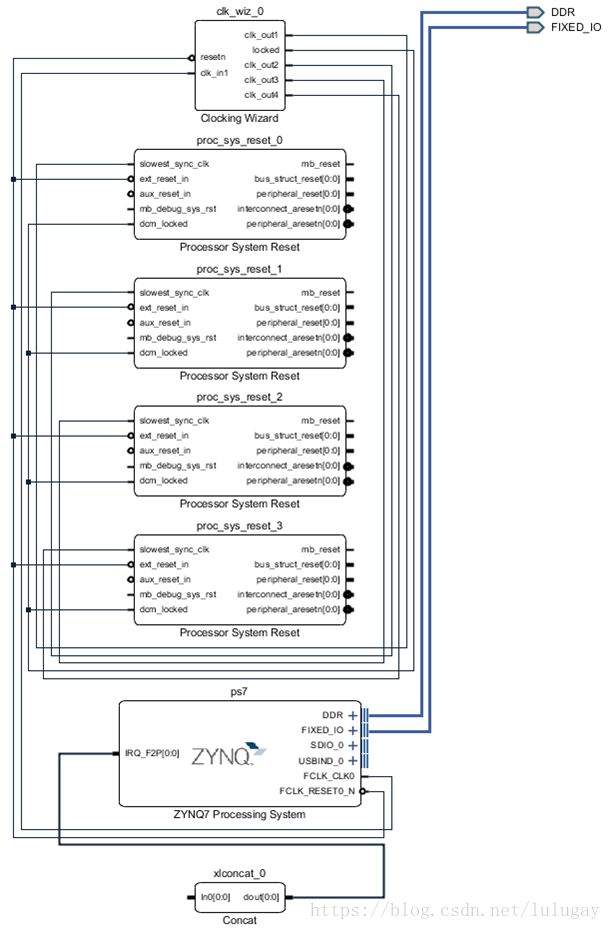

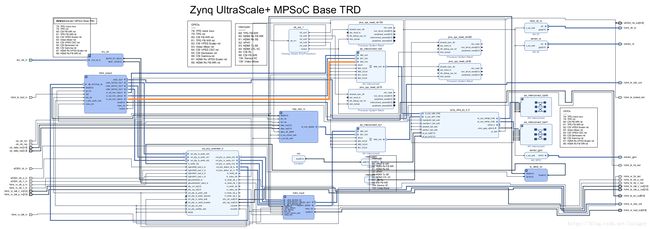

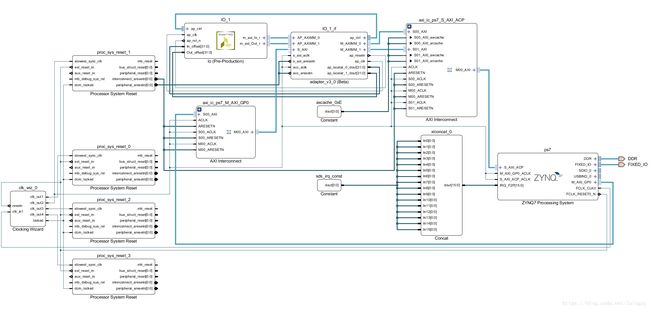

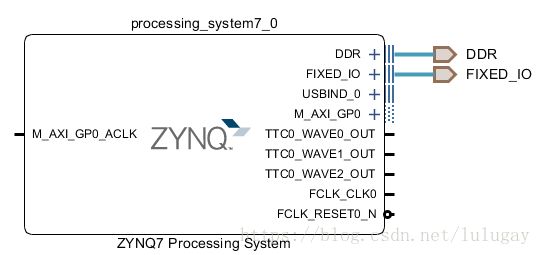

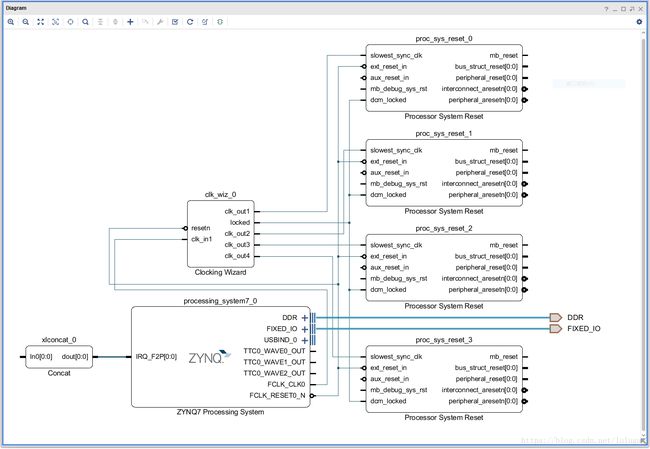

上图是PYNQ SDSoC Platform硬件部分的基础平台,里面只有系统复位(Processor System Reset)模块和时钟向导(Clocking Wizard)模块。在SDSoC中可以指定硬件加速器的时钟频率,如100M、142M、166M和200M,这些频率并不是凭空产生的,而是在Platform的时钟向导模块中指定的,如果想要其他频率可以在时钟向导中添加。

上图是reVISION 的案例平台zcu102_rv_ss Platform硬件部分的基础平台,除了包含系统复位模块和时钟向导模块之外,还包含了MIPI接口和HDMI接口。zcu102_rv_ss提供了一个光流算法的案例,输入是MIPI摄像头,输出是DisplayPort接口(DP接口是连接到PS上的),在SDSoC中无法编写MIPI接口的控制逻辑,所以这部分逻辑是在创建SDSoC平台时准备好的。所有用到MIPI接口的工程都可以使用该基础平台,使用SDSoC工具我们可以很容易地在该基础平台上实现不同的算法。

最终加载进PL的比特流由图3所示工程生成的(路径:Debug/sds/p0/_vpl/ipi/syn),该工程在图1的基础上添加了若干IP,包括:

- io:调用HLS产生的算法加速IP。

- Constant:某些IP的某些接口需要一直为1/0。

- Adaptor:AXI接口在在direct模式下控制信号以及数据需要通过Adaptor转换再连接到算法加速IP上。

- AXI Interconnet:Adaptor的AXI接口不能直接与PS的AXI接口相连,需要通过AXI Interconnect转接。

创建自己的SDSoC Hardware Platform

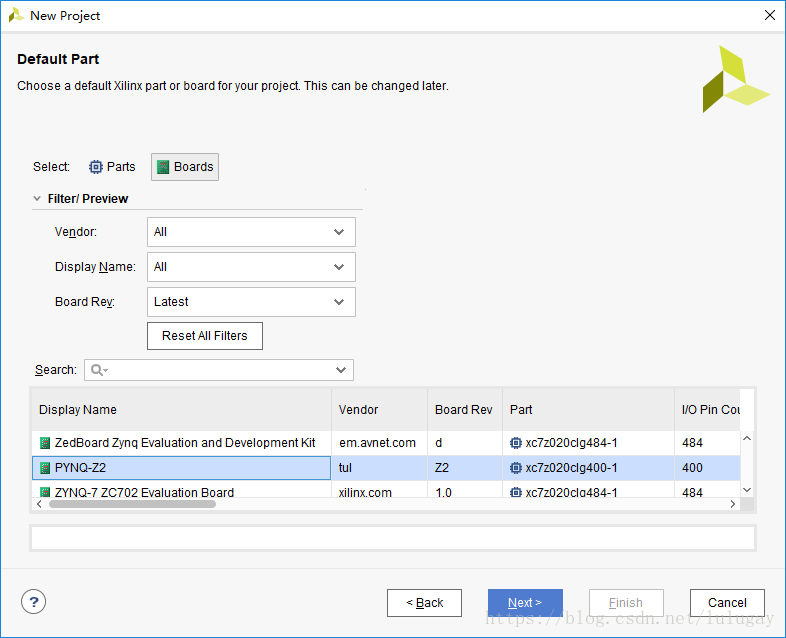

- 打开Vivado IDE并创建一个工程

- Vivado没有提供PYNQ的Board file,将我们提供的PYNQ board file拷贝到{Xilinx_Vivado}\data\boards\board_files路径下

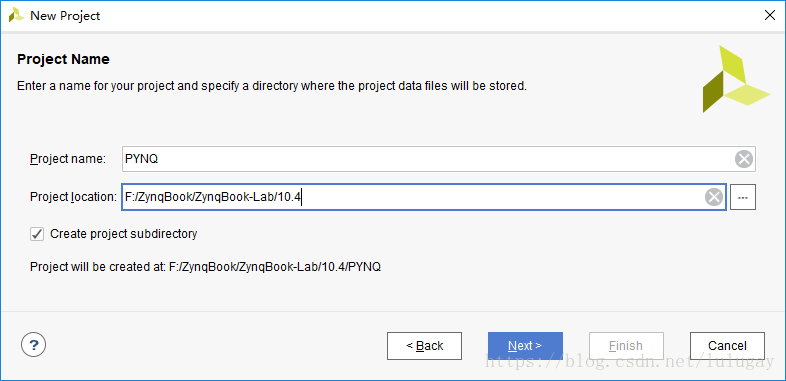

- 打开Vivado IDE,在 Quick Start下点击Create Project,点击Next,输入工程名PYNQ和工程路径,点击Next

- Project Type保持默认RTL Project,点击Next,跳过Add Sources和Add Constraints

- Defualt Part界面下选择PYNQ-Z2

- 点击Next,检查后点击Finish

- 创建一个IP Integrator设计

-

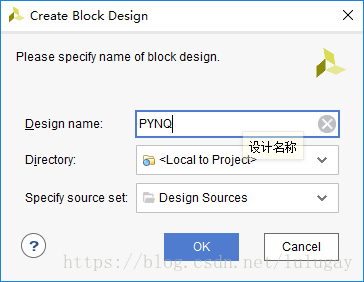

在Flow Navigator –> IP Integrator, 选择Create Block Design.

-

在Block Design画布右键选择Add IP

-

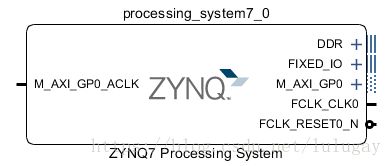

搜索框内输入zynq找到ZYNQ7 Processing System IP

-

在IP catalog中选择ZYNQ7 Processing System IP,按下回车将其添加到Block Design中。

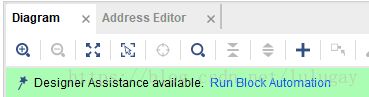

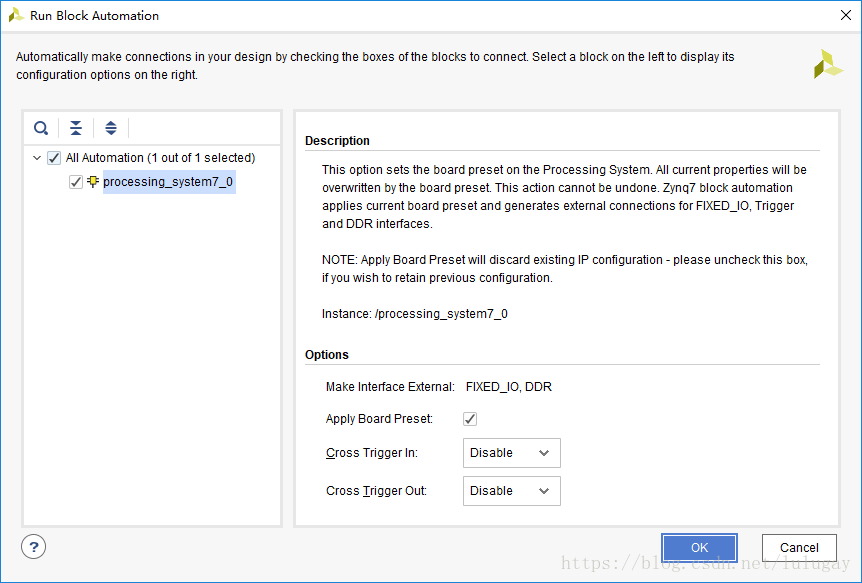

Run Block Automation对话框打开后如下图所示,这个对话框表示FIXED_IO和DDR接口会被创建,Apply Board Preset选项通用会被勾选。在board file文件夹PYNQ目录下有一个preset.xml文件,里面提供了PS部分的基本配置,如DDR的设置。

- 点击OK,在IP integrator diagram会出现如下的图形

- Running Block Automation 之后Zynq-7000 AP SoC Processing System,注意加载preset之后要检查TTC模块,QSPI模块,UART模块,Eth模块有没有被使能,这些模块是Petalinux正常运行所必需的。

- 右键Add IP,输入proc sys res找到Processor System Reset,按回车将这些模块添加到Block Diagram中,重复三次该操作,最终在Block Diagram中应该有四个Processor System Reset

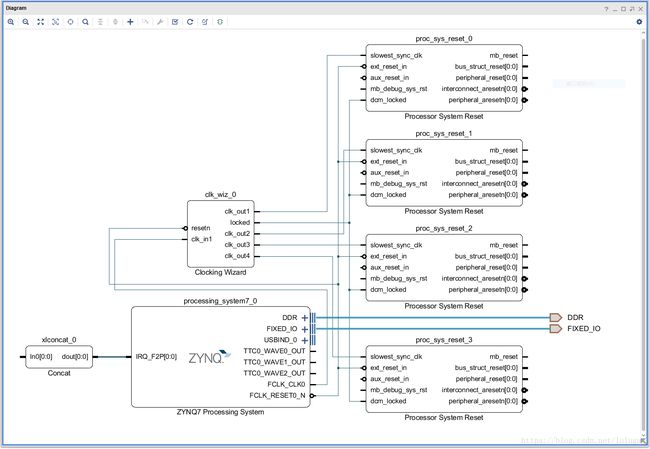

- 相似地,添加Clocking Wizard和Concat IP,以上步骤执行之后Block Diagram应跟下面这张图比较相似

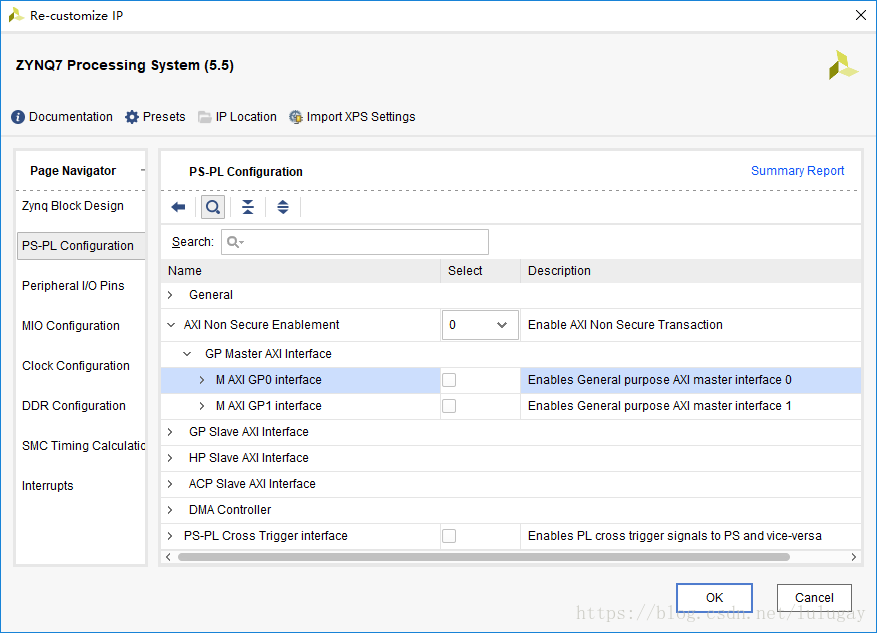

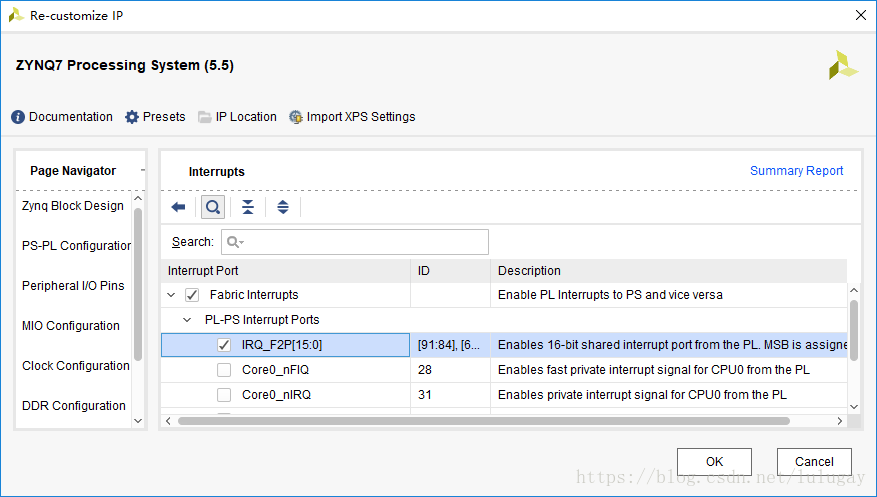

双击Zynq IP打开配置引导界面,在Re-customize IP对话框中执行如下操作

-

PS-PL Configuration-> AXI Non Secure Enablement-> GP Master AXI Interface取消勾选M AXI GP0 interface

-

Interrupts->勾选Fabric Interrupts->PL-PS Interrupt Ports,勾选IRQ_F2P[15:0],点击OK退出

-

双击Clocking Wizard进入配置界面,选择Output Clocks选项卡,勾选clk_out2,3,4并按照下图配置频率,这些频率就是最终在SDSoC平台中可以选择的频率。

-

在该页面下向下滑动,将Reset Type设置成Active Low,点击OK关闭该界面。

-

双击Concat IP,将Number of Ports设置为1,Re-customizing IP之后的Block Diagram应如下图所示。

下面开始手动连线

- clk_wiz_0/ clk_in1与ZYNQ7 PS/ FCLK_CLK0,clk_wiz_0/clk_out1与proc_sys_reset_0/ slowest_sync_clk相连,以此类推连接所有PSR的slowest。

- 将ZYNQ7 PS/FCLK_RESET0_N,Clocking Wizard/resetn,所有PSR/ext_reset_in相连

- 将Clocking Wizard的locked与所有PSR的dcm_locked相连。

- 将Concat的dout[0:0]与ZYNQ7 PS的IRQ_F2P[0:0]相连。

- 点击Regenerate Layout按钮重新生成Block Diagram的布局。

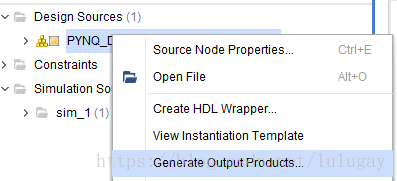

- 右键bd文件,点击Generate Output Products-> Synthesis Options->Global,点击Generate

然后右键bd文件,点击Create HDL Wrapper,生成HDL Wrapper。

- 设置Platform属性

完成Vivado设计套件中的硬件平台设计项目后,必须完成添加平台属性(PFM)定义平台名称并配置平台接口如时钟,中断和总线接口。这些属性被设置一次并存储在工程中。平台通常由多个时钟组成。在当前项目中,我们的设计包含四个用Clocking Wizard生成不同的时钟,用户可以在SDSoC中选择要被硬件加速的函数的时钟频率。同理,在SDSoC中被用到的AXI端口也要标注,硬件加速函数会用这些被标注的AXI端口来建立Data motion network。

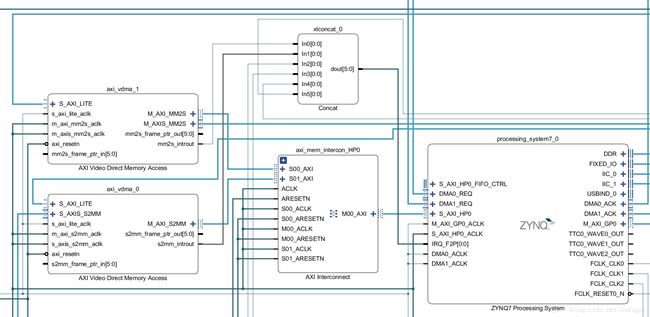

上图所示的Block Diagram中S_AXI_HP0被两个VDMA占用,那么这个AXI端口就不再可以被SDSoC调用。这些AXI端口在Block Diagram中可能不可见(在该Block Diagram中只能看到S_AXI_HP0),但是只要平台属性里标注好就可以被SDSoC中的硬件加速函数使用。

- 平台属性(PFM_NAME)必须定义Vendor, Library, Name, and Version (VLNV),在Tcl Console中输入如下指令并按回车,设置SDSoC Hardware Platform的名称。

set_property PFM_NAME "xilinx.com:PYNQ:PYNQ:1.0" [get_files PYNQ.bd]

PFM_NAME属性按照下面的格式

:::

- 用户可以导出平台内的任何时钟源,但是被导出的时钟源要搭配一个Processor System Reset IP。PFM.CLOCK属性可以设为BD cell,外部端口或者外部接口。比如在本设计中时钟源来自Clocking Wizard的四个输出,也可以选择PS的FCLK_CLK0~3作为时钟源。输入如下指令并按回车,设置SDSoC Hardware Platform的时钟。

set_property PFM.CLOCK {\

clk_out1 {id "0" is_default "false" proc_sys_reset "proc_sys_reset_0"} \

clk_out2 {id "1" is_default "true" proc_sys_reset "proc_sys_reset_1" } \

clk_out3 {id "2" is_default "false" proc_sys_reset "proc_sys_reset_2"} \

clk_out4 {id "3" is_default "false" proc_sys_reset "proc_sys_reset_3"} \

} [get_bd_cells /clk_wiz_0]

- 定义AXI端口

set_property PFM.AXI_PORT { \

M_AXI_GP0 {memport "M_AXI_GP"} \

M_AXI_GP1 {memport "M_AXI_GP"} \

S_AXI_ACP {memport "S_AXI_ACP" sptag "ACP" memory "ps7 ACP_DDR_LOWOCM"} \

S_AXI_HP0 {memport "S_AXI_HP" sptag "HP0" memory "ps7 HP0_DDR_LOWOCM"} \

S_AXI_HP1 {memport "S_AXI_HP" sptag "HP1" memory "ps7 HP1_DDR_LOWOCM"} \

S_AXI_HP2 {memport "S_AXI_HP" sptag "HP2" memory "ps7 HP2_DDR_LOWOCM"} \

S_AXI_HP3 {memport "S_AXI_HP" sptag "HP3" memory "ps7 HP3_DDR_LOWOCM"} \

} [get_bd_cells /ps7]

- SDSoC产生的中断需要通过Concat模块转接到Zynq7000系列的F2P_irq端口

set intVar []

for {set i 0} {$i < 16} {incr i} {

lappend intVar In$i {}

}

set_property PFM.IRQ $intVar [get_bd_cells /xlconcat_0]

- 生成HDL设计文件

- File->Export->Export Hardware勾选include bitstream,点击OK,这一步的目的是生成.hdf文件,后面Petalinux会用到这个文件。

- 打包DSA文件

- 将所有文件打包成DSA文件,在Tcl Console中输入下面指令

write_dsa –force /PYNQ.dsa -include_bit

注意,SDSoC Hardware Platform的名称,即PFM_NAME下的要与Vivado工程名,block diagram名以及dsa文件名保持一致以免出现不必要的麻烦,在本教程中所有的名称都是PYNQ。

- 验证DSA文件的正确.

validate_dsa /PYNQ.dsa

SDSoC Software Platform

Zynq启动时需要的文件包括kernel,device-tree,u-boot和fsbl,如果与PL部分相关,还需要.bit文件,这些文件除了.bit文件都可以由Petalinux生成,其中image.ub文件包含了kernel以及device-tree。

Petalinux 简介

PetaLinux 是Xilinx 提供的工具链, 用于生成Linux 内核映像, 根文件系统和ZYNQ 的内核模块, 例如带有可编程硬件的嵌入式系统(用于FPGA 部分中的不同硬件设计)。使用PetaLinux工具链, 我们可以轻松地为ZYNQ PS 构建内核和模块, 而无需使用单独的交叉编译工具。使用PetaLinux 的一个缺点是, 每个PetaLinux 版本都带有特定的Linux 内核版本。例如PetaLinux2017.4 带有4.9 的默认内核版本。赛灵思提供了一种方法来改变Petalinux 使用的默认内核版本, 读者可以通过百度搜索轻松找到它, 在此不赘述。注意:对于特定的硬件设计,PetaLinux 工具可以生成U-Boot 文件, 第一阶段启动加载程序(FSBL)和BOOT.BIN。使用Xilinx SDK 可以完成同样的事情。

环境要求

2017.4/2018.2 版本的工具链(包括Vivado,SDSoC,Petalinux)跟之前的版本有很大区别, 因此强烈建议版本与本文保持一致。此外,SDSoC,Vivado,Petalinux必须版本一致,本文在2017.4、2018.2均测试通过。

- Ubuntu16.04 的PC

- SD 卡(8GB 或更大)

- SD 卡读卡器

- 搭载ZYNQ 系列处理器的板卡, 本文在PYNQ 上测试通过

- 装有Vivado2018.2的PC,Windows/Linux 均可

安装Petalinux

- Petalinux必须安装在Linux系统上,下面提供在Ubuntu16.04上安装的步骤

Petalinux2017.4 版本下载链接:

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/embedded-designtools/2017-4.html

读者可以直接到Xilinx官网查找

$ sudo apt-get install gawk xvfb chrpath socat autoconf libtool git texinfo zlib1g-dev zlib1g-dev gcc-multilib libsdl1.2-dev libglib2.0-dev zlib1g-dev libncurses5-dev libssl-dev zlib1g:i386 –y

安装Petalinux 依赖的库

$ sudo mkdir -p /opt/pkg/petalinux

$ cd /opt/pkg/

$ sudo dpkg-reconfigure bash

UG1144 中提到所用到的/bin/sh 命令都需要是bash, 而Ubuntu 默认的/bin/sh 是dash, 在弹出界面选“否”来禁用dash, 选择bash

$ sudo chown USERNAME:users petalinux/ -R

USERNAME 替换成Ubuntu 的用户名,Petalinux 不能在root 权限下安装,,所以需要chown

$ cd

$ ./petalinux-v2017.4-final-installer.run /opt/pkg/petalinux

等待一段时间来到了Agreement 部分, 按Enter 进入协议文本, 按q 退出协议文本, 输入y 同意协议, 进入下一条协议, 若干次之后, 就进入安装部分, 再等待一段时间Petalinux 就安装完成了

$ source /opt/pkg/petalinux/settings64.sh

每次使用petalinux之前要先设置环境

使用PetaLinux 为SDSoC Hardware Platform 生成image

- 按照上一章介绍的方法生成PYNQ 的SDSoC Hardware Platform 的Vivado 工程, 生成bitstream。然后File->Export->Export Hardware, 勾选include bitstream, 在工程目录.sdk 文件夹下可以找到一个.hdf 文件(硬件描述文件)。

- 创建Petalinux工程

$ petalinux-create –type project –template zynq –name PYNQ

新建Petalinux 工程, 命名为PYNQ,会自动生成一个名为PYNQ的文件夹

$ cd PYNQ/

将第一步中.hdf 文件复制到PYNQ 文件夹下

$ petalinux-config –get-hw-description ./

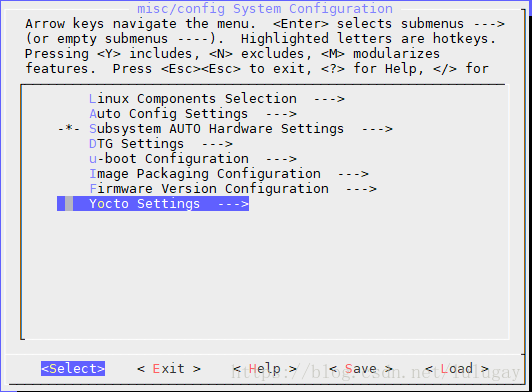

- 配置system config

DTG Settings->Kernel Bootargs->generate boot args automatically 取消勾选该选项

手动将bootargs 设置成

console=ttyPS0,115200 earlyprintk quiet

- 配置内核

$ petalinux-config -c kernel

Device Drivers->Generic Driver Options->Size in Mega Bytes(256)

Device Drivers->Staging drivers (ON)->Xilinx APF Accelerator driver (ON)->Xilinx APF

DMA engines support (ON)

保存并退出

- 手动添加设备树

打开/project-spec/metauser/recipes-bsp/device-tree/files/system-user.dtsi, 添加如下几行

/{

xlnk {

compatible =“xlnx,xlnk-1.0”;

};

};

- 编译工程

$ petalinux-build

编译结束后在images/linux下找到zynq_fsbl.elf, u-boot.elf, image.ub, 这些文件之后会用到。

SDSoC Platform

前两节我们已经准备好了搭建自己的SDSoC Platform所需要的文件,下面我们将介绍如何将这些文件组织成一个SDSoC Platform。一个典型的SDSoC Platform文件结构如下

创建自己的SDSoC Platform

- 新建一个文件夹命名为boot,将上一节生成的zynq_fsbl.elf改名为fsbl.elf,和u-boot.elf文件放到该文件夹下,然后新建一个linux.bif文件,输入以下内容

/* linux */

the_ROM_image:

{

[bootloader]

}

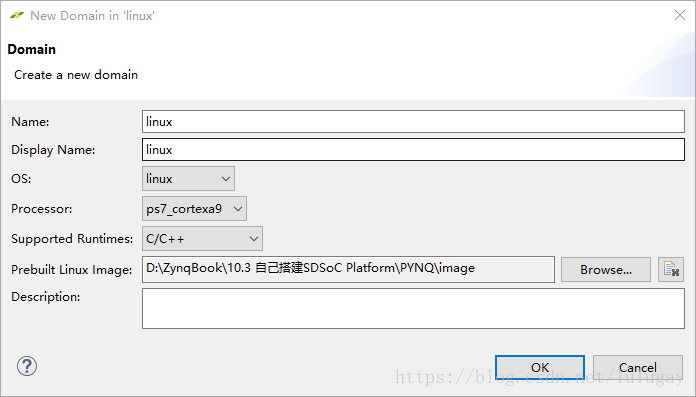

- 打开SDSoC新建一个工程,Project type选择Platform Project,然后找到dsa文件,工程会自动命名为dsa文件的名称

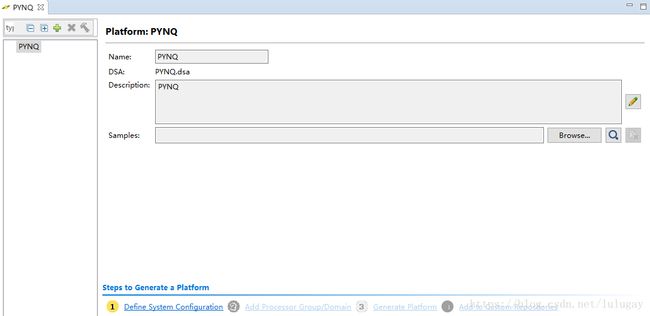

- 打开该工程

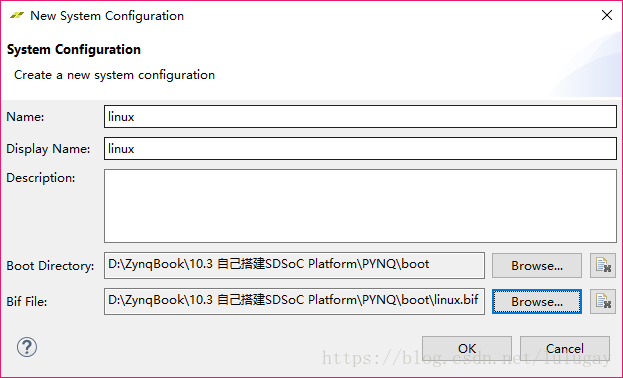

SDSoC Platform Project - 点击左下角Define System Configuration,添加以下内容

Define System Configuration

boot directory里包含了u-boot.elf,fsbl.elf,这两个文件将与SDSoC生成的.bit文件打包在一起生成BOOT.BIN文件。

这一步完成点击Generate Platform和Add to Custom Repositories将使该Platform可以被SDSoC工具找到。至此我们就完成了搭建最基础的SDSoC Platform的流程,下一章将介绍如何将SDSoC应用到实际项目中。

欢迎大家关注Xilinx学术合作以及Pynq的官方公众号,里面有许多优质的学习资源等着你哦

![]()

![]()

希望了解HLS的同学可以关注公众号Xilinx学术合作以及PYNQ中文社区获取最新版《FPGA并行编程-- 以HLS实现信号处理为例》pdf ,关注任一公众号,回复 pp4fpgas 即可获得