Vivado开发套件设计笔记(2)——加法器设计——变量(上)

目录

- 1 简介

- 2 HLS设计

- (1)创建工程

- (2)程序设计

- (3)四步曲

- 2 HLS设计(番外)

- 3 Vivado设计

- (1)创建工程

- (2)硬件电路连接

- (3)硬件信息输出

1 简介

在上一篇博文中笔者介绍了Vivado™设计套件的概要,用途,优点,开发思路等等。这一篇博文中,我就不啰嗦直接进入正题,以最简单的变量加法器作为例子,从HLS到Vivado再到SDK走一遍流程,让读者更快地体会到Vivado这一开发技巧的便捷性,为之后最更复杂的设计打下最基本的地基。

2 HLS设计

首先要做的是在Vivado HLS上设计我们所需要的加法器IP核。

这里科普一下IP核:IP核就是知识产权核或知识产权模块的意思,在EDA技术开发中具有十分重要的地位。美国著名的Dataquest咨询公司将半导体产业的IP定义为“用于ASIC或FPGA中的预先设计好的电路功能模块”。IP主要分为软IP、固IP和硬IP。软IP是用Verilog/VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。固IP是完成了综合的功能块。硬IP提供设计的最终阶段产品——掩膜(来自百度百科)。相信会看这一博文的各位一定是很清楚的,这里我为了再多废话一点,我们平时做C程序设计总是会自定义一些 子函数 方便主函数的调用并使得主函数更精简,这些函数一般都是在CPU上跑的,而IP核可以理解成在硬件上通过电路实现出来的 子函数 ,起着数据处理或交换等作用。

言归正传,我们从最基本的开始一步一步做。

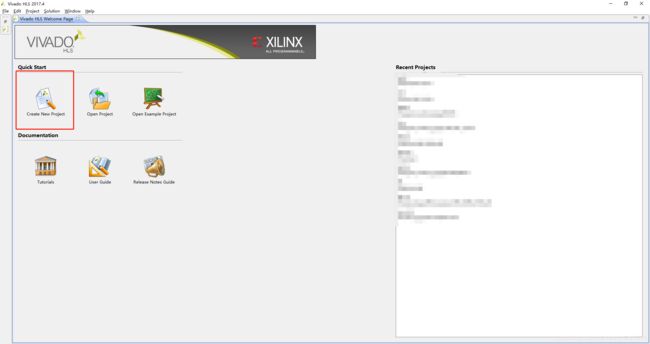

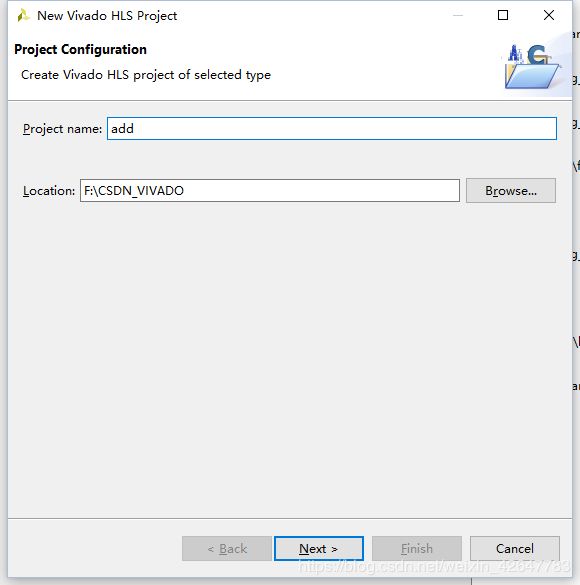

(1)创建工程

按照红色框框来,先创建工程。

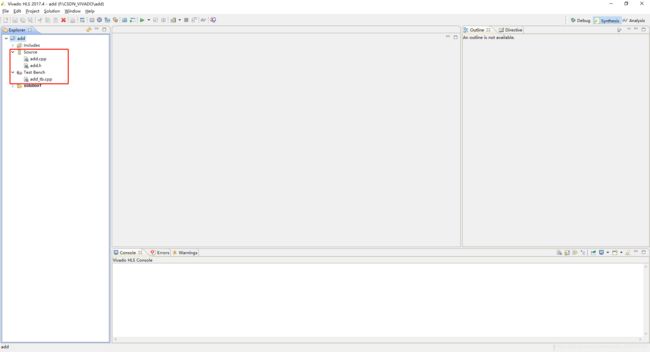

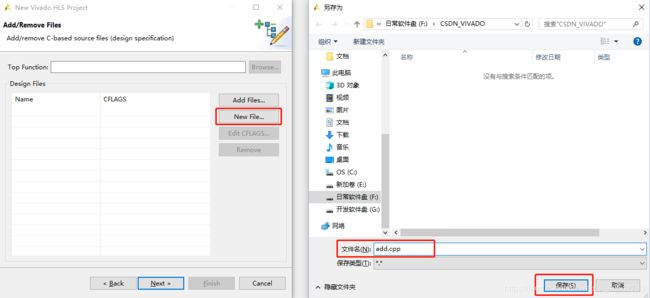

点击 New File… 创建所需的文件,一是头文件,二是顶层函数文件。IP核 就是根据 顶层文件 综合出来的,非常重要。相继添加 add.cpp 和 add.h 。添加完成后 Design Files 框中就会有刚添加的两个文件,此时上面的 Top Function 框是还没有东西,这里等我们写完程序后再在工程中设置就可以。

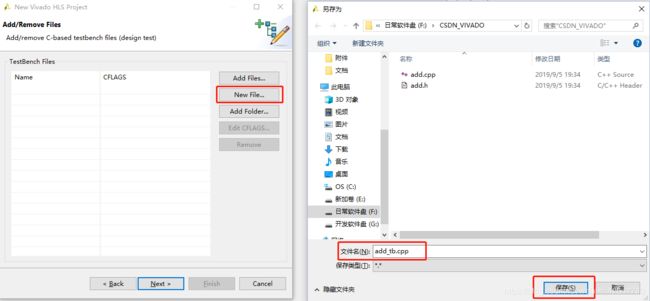

然后添加testbench测试文件,这在做C综合过程中也是必不可少的,添加方法更上面添加顶层文件和头文件是一样的。

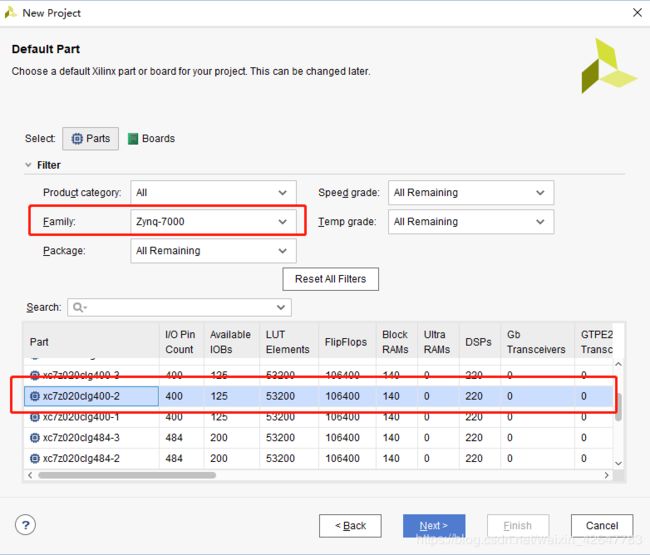

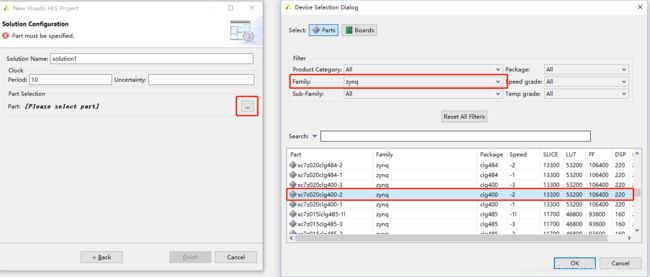

然后选择硬件,我用的开发硬件是黑金的AX7020板子,根据芯片型号这里选择的是 xc7020clg400-2 ,读者在开发的时候需要根据自己的硬件选择一致的。左边的 Solution 不用变,之后的博文会介绍。

这样就完成工程创建了,如果出现以下错误不用管它,直接点 Close 和 OK 就可以了。

在这里插入图片描述

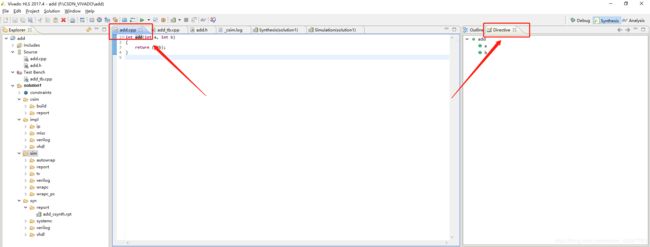

然后软件就会打开设计界面,如下图所示。

(2)程序设计

双击 add.cpp ,如上图所示,并添加 顶层文件 的代码。如下:

int add(int a, int b)

{

return (a+b);

}

然后双击 add.h ,添加 头文件 的代码。如下:

#ifndef add_h_

#define add_h_

int add(int, int);

#endif

最后双击 add_tb.cpp ,添加 testbench 的代码。如下:

#include "add.h"

#include <iostream>

#include <cstdio>

#include <fstream>

int main()

{

int a, b;

a = 5;

b = 10;

int res;

res = add(a, b);

if(res == 15)

{

printf("OK");

return 0;

}

else

return 1;

}

关于这些程序的写法,相信有过C语言基础的读者应该比较清楚,篇幅有限,笔者暂且不过多阐述。这里值得一提的是,testbench文件 中一般都会有一个验证顶层函数是否正确的语句,比如这里我用的 res == 15表示加法器的输出与预想一致,那么返回值为0。如果一个 main 函数的返回值是0的话,程序就是正确的,如果返回值是1的话(条件是我们自己设定的),程序在做C仿真的时候是会出现错误的。

(3)四步曲

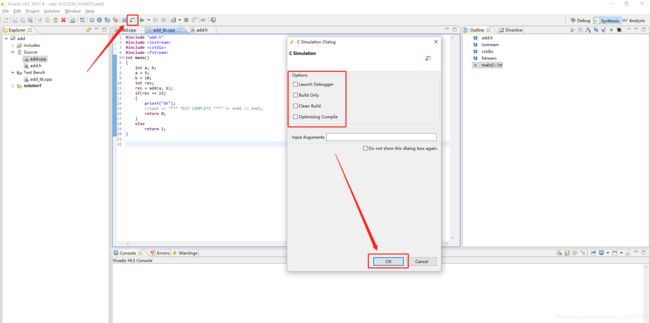

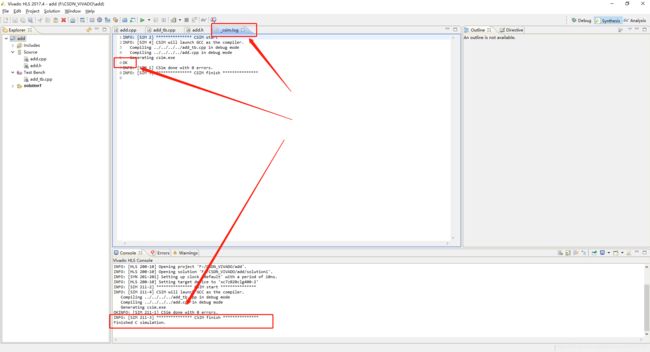

第一步,做 C仿真(C Simulation)。

看到下图就是 C仿真 成功了,上面打印出了 OK 标识,与我们程序设定的验证成立条件是一致的,这里读者可以自己改一下数字尝试,看验证不成立的时候是不是会出现仿真出错的提示,这里我节省一下篇幅,留给读者尝试。

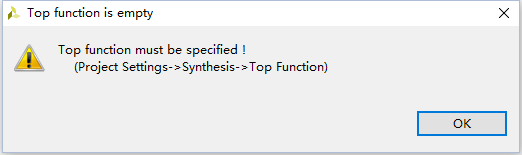

第二步,做 C综合(C Synthesis),点击下图红色框框的按钮,就在上一步 C仿真 的右边。

会出现下图错误,因为我们刚才没有 指定顶层模块 。根据提示做就可以了。

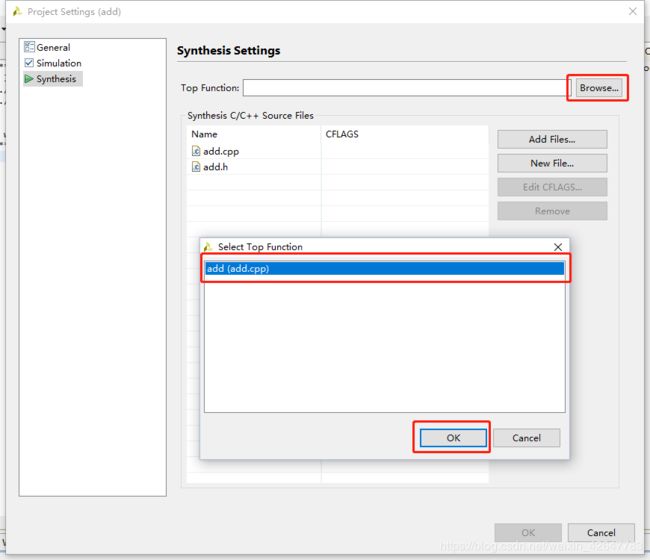

点击菜单栏 Project —— Project Settings… —— Synthesis ,然后根据下图点击就可以了。

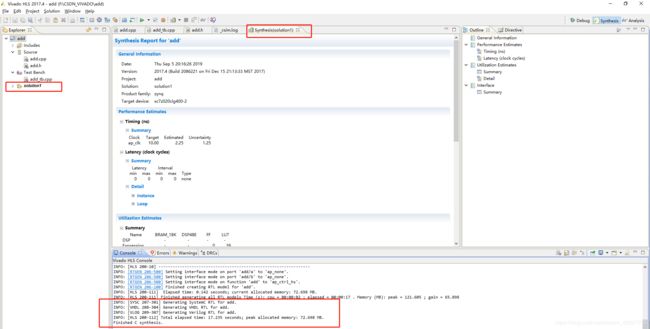

之后再点击一次 C综合(C Synthesis) 按钮,就会出现下图所示的结果。

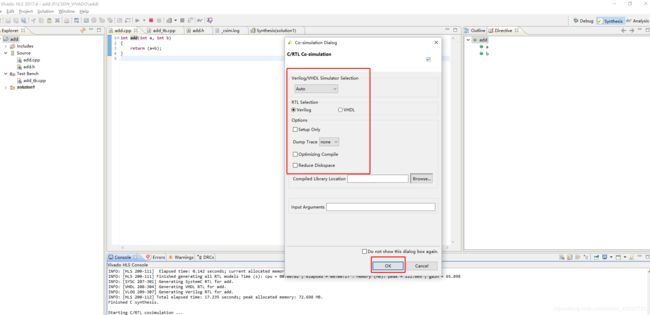

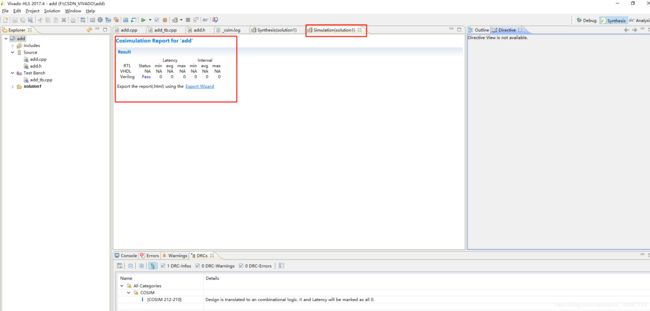

第三步,做 C/RTL联合仿真(C/RTL Cosimulation) ,点击下图中的红色框框,在上一步 C综合 的右边。

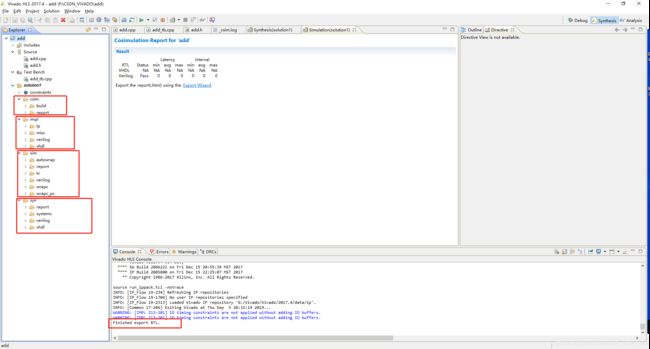

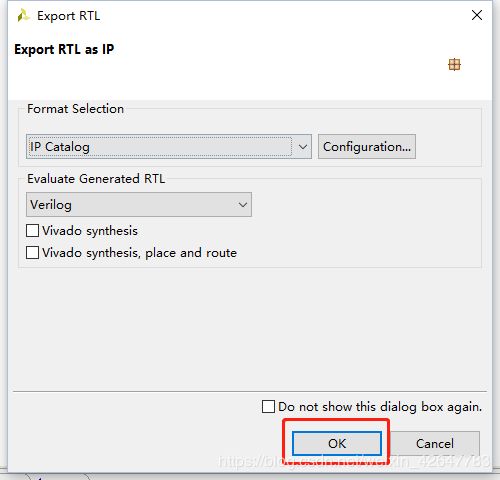

第四步,点击下图红色框框的按钮,导出RTL(Export RTL) 也就是我们一直在说的 IP核 了。

导出后如下图所示,左边的四个框从上到下是刚做完的四步曲对应的四个结果,从上到下分别对应到 C仿真 、导出RTL、C/RTL联合综合 和 C综合 。

2 HLS设计(番外)

上面的设计存在一个问题,就是这样综合出来的一个 IP核,ZYNQ处理系统是没法去用它的,因为数据不知道怎么放到IP核的输入,更不知道怎么把输出取出来,因此这里加入一个 番外,告诉读者最重要的一件事情——添加 AXI接口协议 。这一块笔者在初学的时候查阅了很多资料,大多都没有提及,因此走了很多弯路,这里单独放到一个番外章节旨在提醒读者不要忘记这个重要的步骤。

怎么添加呢?点击到 add.cpp 顶层文件,再点击 Directive (我将其称为综合引导,用来引导HLS按照我们希望的综合方向去走),如下图所示。

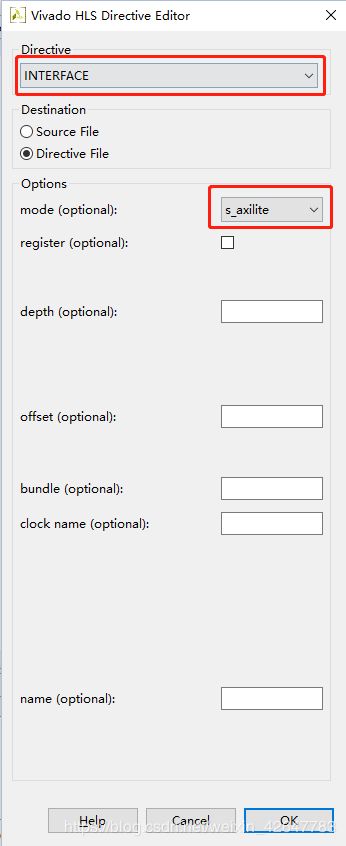

然后点击 Directive 下面的三个绿点对应到的对象,分别是 add 顶层函数(顶层模块)、变量 a和变量 b ,分别用右键点击这三个对象,然后点 Insert Directive… 。然后按照下图选择 Directive 类型 INTERFACE ,再选择 mode 类型为 s_axiite 。这里选择接口协议为AXI协议,关于AXI协议是什么,之后的博文会补充,现在我们先用着。

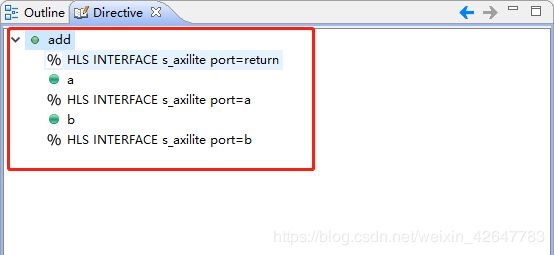

给 add 、a 和 b 三个对象添加同样的引导,如下图所示。

最后再做一下四步曲就可以了,其实可以直接做 C综合 和 导出RTL ,但是保险起见,而且速度也很快,我们就都做一遍。再补充一点, C仿真 、C综合 和 导出RTL 是必不可少的,但是 C/RTL联合综合 对一些比较大的模块可能会非常耗时,如果读者对自己写的程序有信心的话,其实是可以跳过的。

现在我们已经有了加法器的 IP核 了,接下来就是把它用起来。

3 Vivado设计

(1)创建工程

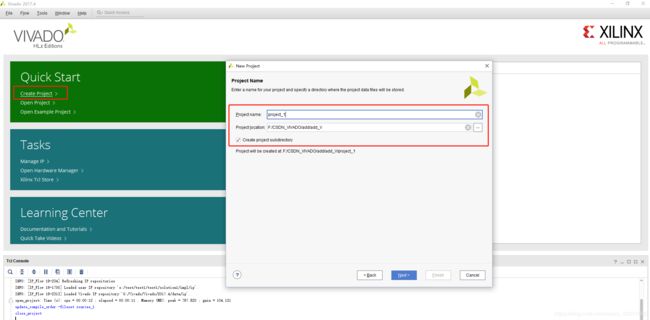

首先创建工程项目,命名并存放在全英文路径中,然后点击 Next 。

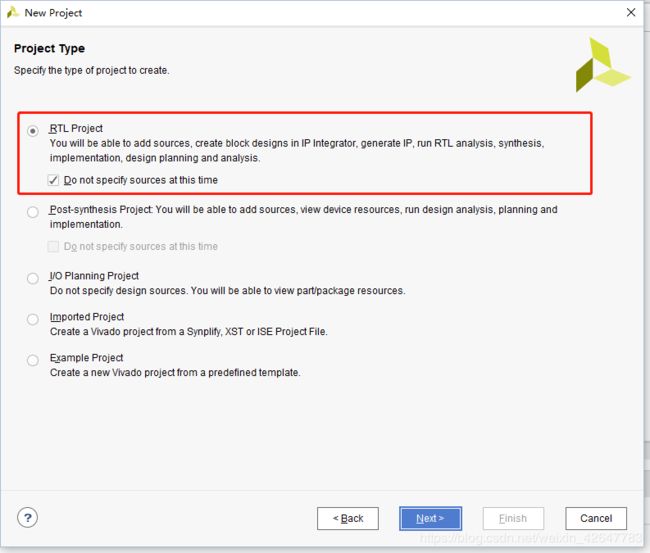

点击下一步选择项目类型为 RTL Project ,下面的选项框选上,然后点击 Next 。

(2)硬件电路连接

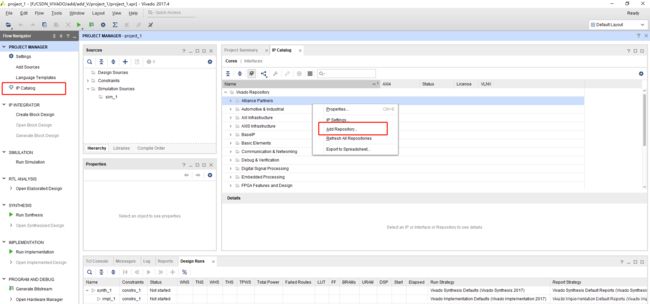

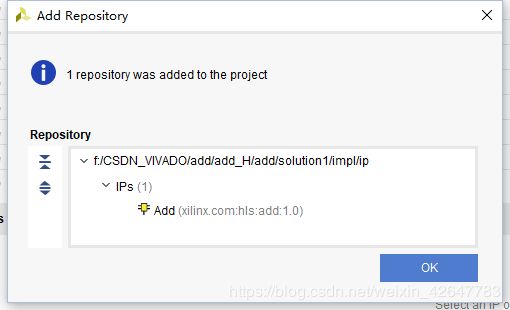

第一步,把 自定义IP核 添加到 IP目录 中,如下图点击。

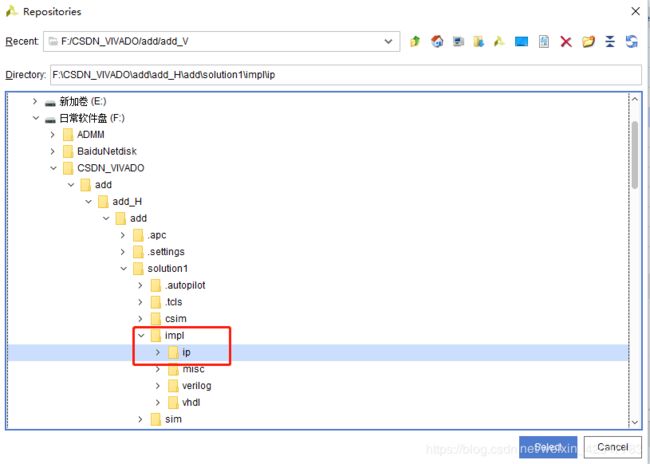

然后找到之前利用 HLS 生成的项目路径,找到其中的 ip 文件夹,如下图所示。

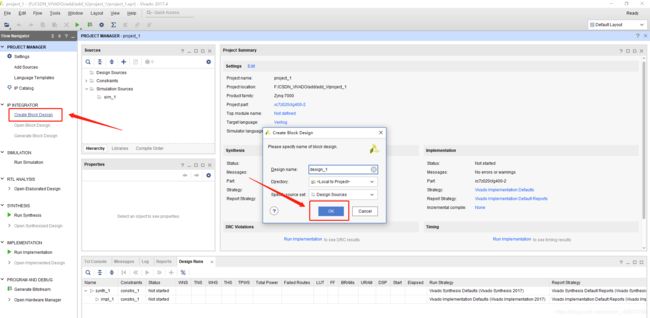

第二步,创建可视化的顶层文件,并连接电路。如下图所示点击 Create Block Design ,然后弹出对话框,不用改名字,直接点击 OK ,完成 Block Design 的创建。

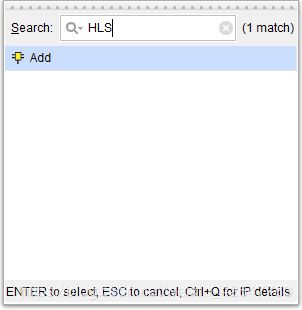

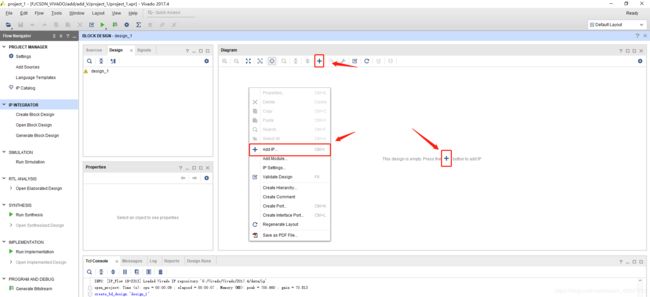

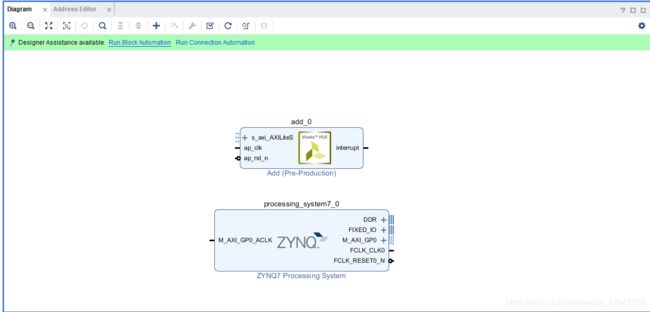

在新出现的 Diagram 框中点击 + 号或者在框内右键再点击 Add IP… ,加入我们刚才设计的加法器IP核 Add ,如下图所示。

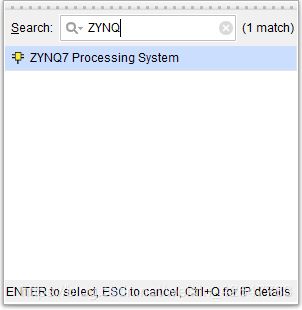

在搜索栏中分别输入 ZYNQ 和 HLS 以快速找到我们想要的 IP核 ,双击添加到我们的 Block Design 。

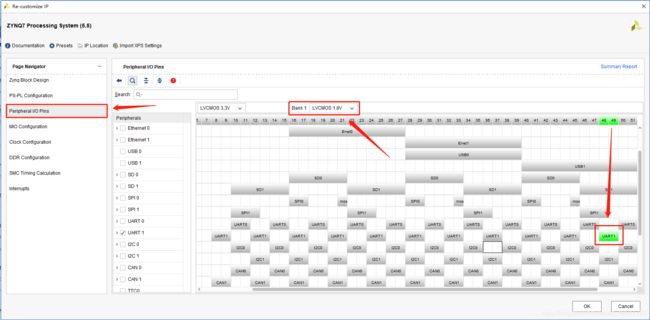

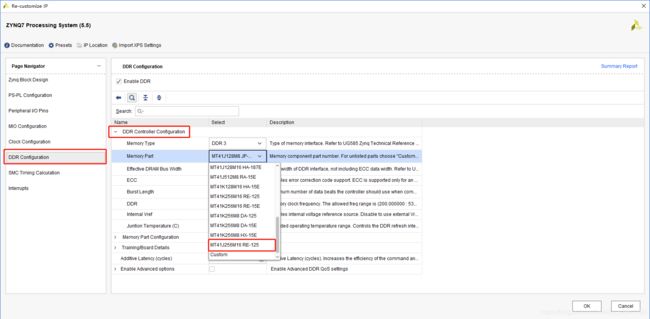

双击 ZYNQ7 Processing System ,配置 串口通信UART ,用于在PC上与硬件通信;配置 DDR3 ,用于数据的存储,根据硬件上 DDR 型号选择最相近的即可。如下图所示。最后点击 OK 完成配置。

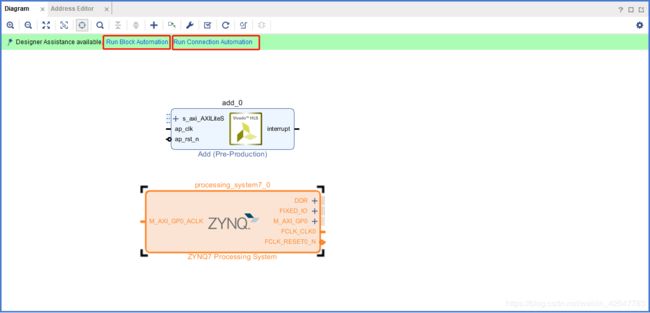

回到 Diagram 界面,分别点击 Run Connection Automation 和 Run Block Automation ,完成自动连线和引出必要端口,如下图所示。

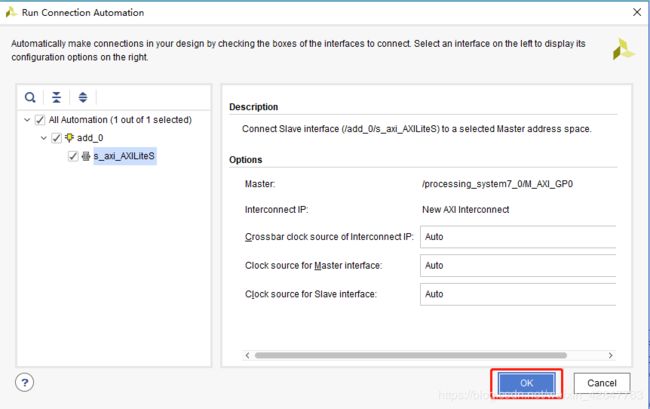

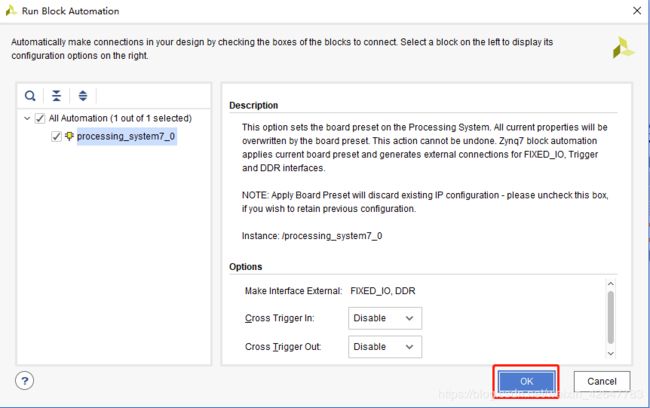

Run Connection Automation 对话框中直接点击 OK 。

Run Block Automation 对话框中直接点击 OK 。

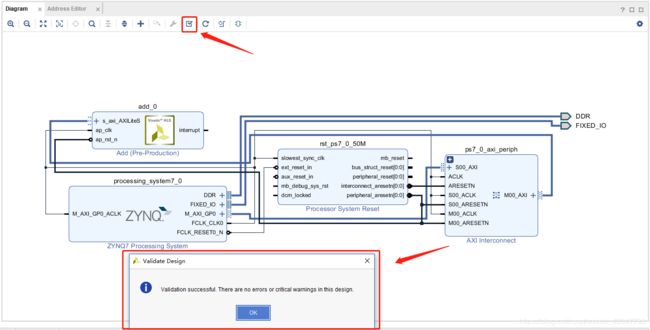

得到如下电路图,然后点击 Validate Design 验证 Block Design 是否有错误。

出现以上信息就是电路验证通过了,接下来的操作就是走走流程就可以了。

(3)硬件信息输出

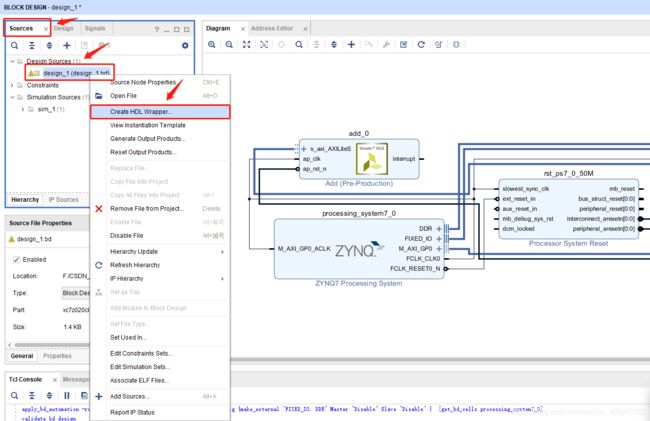

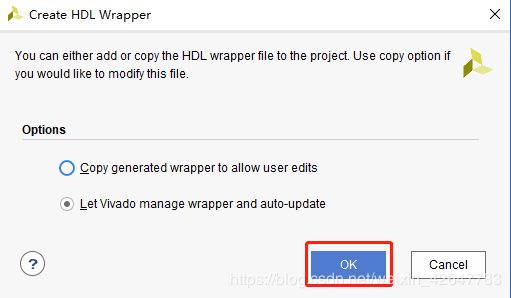

第一步, 创建HDL封装(Create HDL Wrapper) ,按照下图三个红色方框从上到下依次点击,然后在出现的对话框点击 OK 即可。

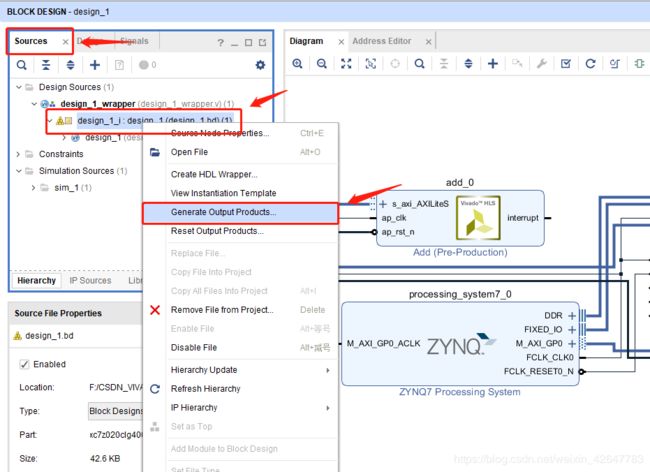

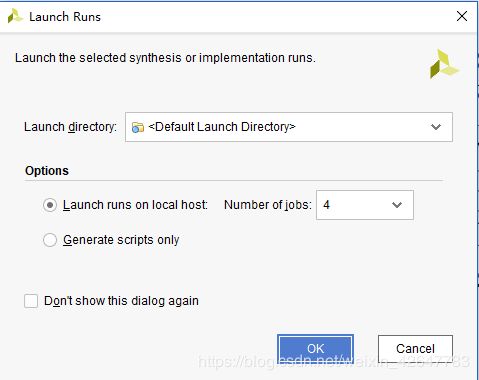

第二步,生成硬件输出(Generate Output Products) ,如下图所示。弹出的 Generate Output Products 直接点击 Generate 即可,对话框中的 Number of jobs 表示想用几个CPU线程去完成这个输出,线程越多速度生成硬件心机就越快。

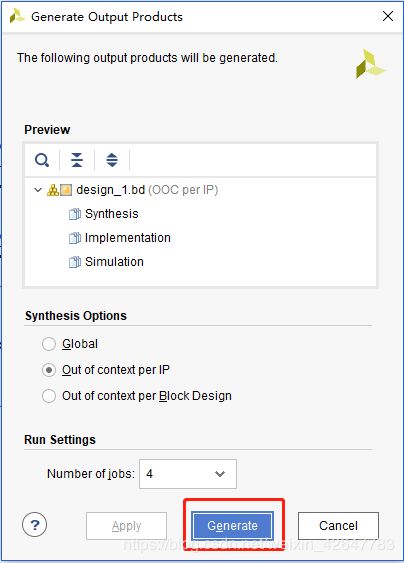

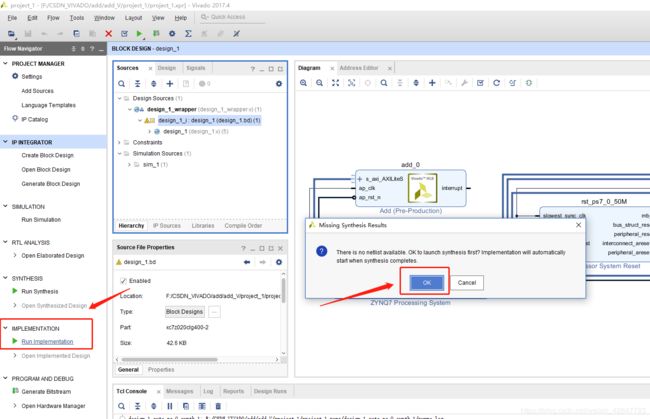

第三步,点击 Run Implementation 运行项目,对话框一直点击 OK 即可。

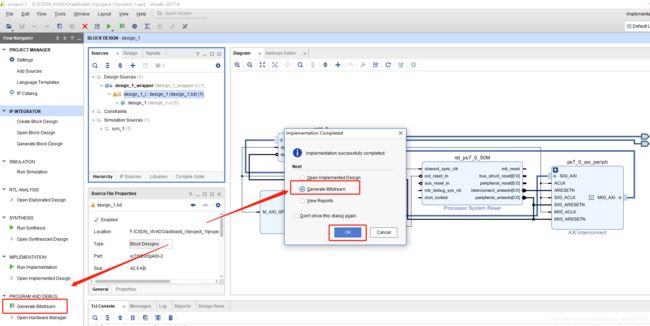

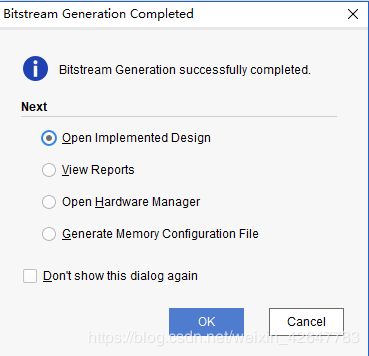

第四步,第三步完成后会出现 Implementation Completed 对话框,可以看到设计的硬件实现的可视化结果图(点击 Open Implemented Design 再点击 OK ),也可以不看,直接生成含有硬件信息的 bit流(Generate Bitstream) ,如下图所示。可以直接在对话框中生成,也可以到左侧 Flow Navigator 导航栏中去操作生成,弹出的 Bitstream Generation Completed 对话框可以不看,直接点击 Cancel ,读者有兴趣的话也可以自行去点开看一下结果。

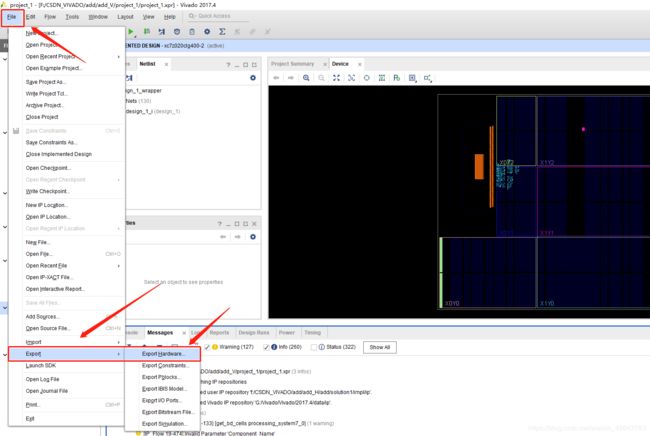

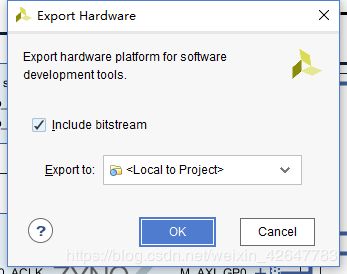

第五步,导出硬件信息(Export Hardware) ,按照下图点击,弹出的 Export Hardware 对话框把 Include Bitstream 选上,然后点 OK 。

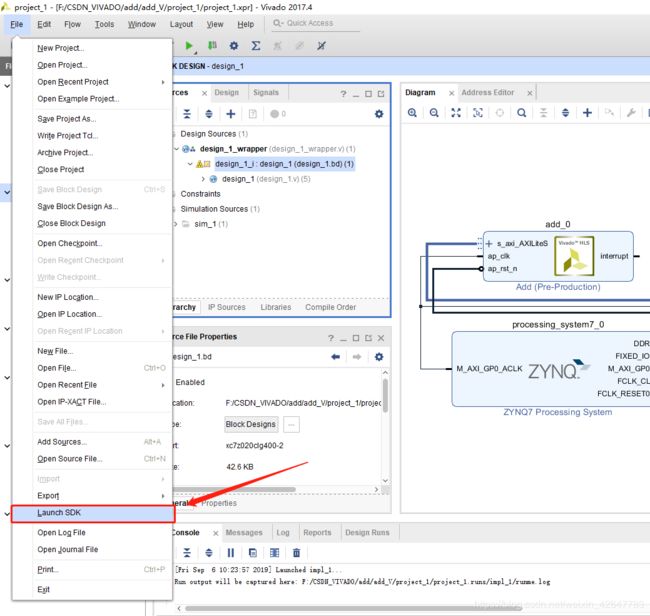

搞定,Vivado 软件上的操作到此为止,接下来就是 SDK 的操作了。直接从 Vivado 软件中运行 SDK, 如下图,弹出的 Launch SDK 对话框直接点击 OK 。

补充一点,在每一步操作之后,软件右上角都会有一个软件运行状态的指示区,指示现在软件正在干什么活,读者在做完每一步操作都等它提示操作完成之后,再做下一步,避免出现问题。

由于本博文讲的比较详细,篇幅量较大,全部放在一个博文中读者不太方便阅读,所以笔者把剩下的工作放到下一篇博文《Vivado开发套件设计笔记(2)——加法器设计——变量(下)》中,如造成不便还请谅解。

原创性声明:本文属于作者原创性文章,小弟码字辛苦,转载还请注明出处。谢谢~

如果有哪些地方表述的不够得体和清晰,有存在的任何问题,亦或者程序存在任何考虑不周和漏洞,欢迎评论和指正,谢谢各路大佬。

需要代码和有需要相关技术支持的可咨询QQ:297461921