基于FPGA的图像浮雕效果实现

基于FPGA的图像浮雕效果实现

- 项目简述

- 算法原理及MATLAB实现

- 浮雕效果的FPGA实现

- FPGA工程代码

- 下板效果

- 参考文献

- 总结

项目简述

为什么要做这个小项目,因为最近正在在学习FPGA开源工作室中的FPGA图像处理的文章。发现这个小例子非常容易实现。就把这个小算法给复现了。这个基本上不能称之为一个项目,因为太简单了。但是,这里面涉及了真彩图转变成灰度图像的一个方法,在书写的时候我们也用到了除法器Ip(为了介绍IP专门使用的触除法器),有符号数的使用。所以,这里我们这里进行简单的介绍。

算法原理及MATLAB实现

写了好多博客关于图像处理算法的实现,不知道大家发没发现图像处理算法很容易在FPGA中复现,这是因为图像处理的数据是整数,一般也都针对像素点处理,这在FPGA实现的过程中完全没有压力。所以这也是FPGA在图像处理中的一个优点。

图像实现浮雕效果与SOBEL是非常相似的,只不过SOBEL是与一个像素点周围的像素点有关,而浮雕处理至于自己一行的像素点有关。具体的公式如下:

i m a g e _ n e w ( i , j ) = i m s g e ( i , j ) − i m a g e ( i , j + m ) + T H image\_new(i,j)=imsge(i,j)-image(i,j+m)+TH image_new(i,j)=imsge(i,j)−image(i,j+m)+TH

其中i是图像的行数,j是图像的列,TH是设置的阈值。这里需要注意的是上面的图像是灰度图像。

这里的m可以控制浮雕效果的明显程度,TH控制主背景的明亮程度。

常见的真彩图转换成灰度图像的方法主要有:

1、直接取RGB三分量其中的一种当作灰度化图像

2、将RGB三分量取平均当作灰度化图像

3、进行RGB到YCbCr格式的转换,取Y分量当作灰度化图像

本篇文章中我们使用的是第2中方法。

原理这么简单,也就不多说,MATLAB代码如下:

clc

clear all

image_old = imread('456.bmp');

image_gray= (image_old(:,:,1) + image_old(:,:,2)+image_old(:,:,2))/3;

[Height,Width] = size(image_gray);

image_new = zeros(Height,Width);

TH = 100;

for i = 1:Height

for j=1:Width-2

image_new(i,j)=image_gray(i,j)-image_gray(i,j+2)+TH;

if image_new(i,j) >255

image_new(i,j) = 255;

elseif image_new(i,j) <0

image_new(i,j) = 0;

else

image_new(i,j) = image_new(i,j);

end

end

end

image_new = uint8(image_new);

imshow(image_new);

实验效果如下:

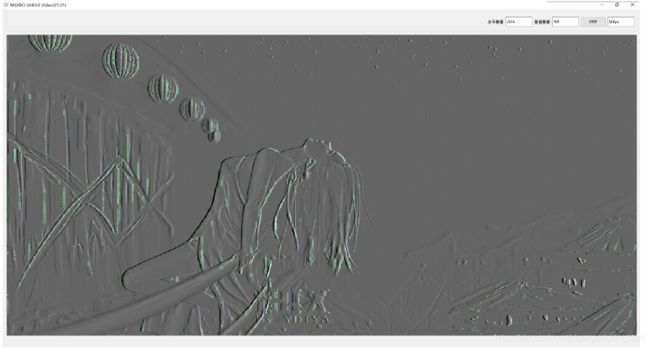

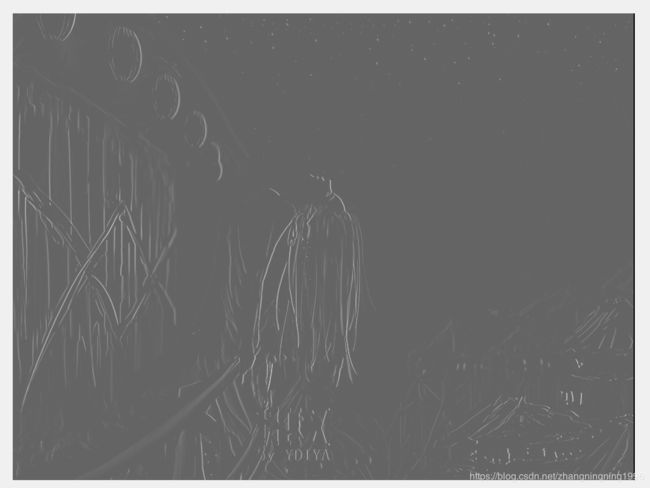

处理后的图像为m=2:

处理后的图像为m=4:

对比上面两张图可以发现m可以控制浮雕效果的明显程度

浮雕效果的FPGA实现

上面的MATLAB代码,我们已经详细写出了算法流程,接下来我们直接给出相应的图像处理代码,并指出几点需要注意的地方:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : image.v

// Create Time : 2020-05-12 09:40:55

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module image(

//System Interfaces

input sclk ,

input rst_n ,

//Communication Interfaces

input [31:0] rgb_data ,

input rgb_data_en ,

output wire [31:0] data_wr ,

output reg data_wr_en

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [15:0] gray_data ;

reg rgb_data_en_r ;

wire [23:0] divider_data ;

wire divider_data_en ;

reg [23:0] divider_data_r ;

reg [23:0] divider_data_r2 ;

reg signed [10:0] count_data ;

reg [ 7:0] dout ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

assign data_wr = {8'h00,dout,dout,dout};

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

gray_data <= 16'd0;

else

gray_data <= rgb_data[31:24] + rgb_data[23:16] + rgb_data[15:8] + rgb_data[7:0];

always @(posedge sclk)

rgb_data_en_r <= rgb_data_en;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)begin

divider_data_r <= 8'd0;

divider_data_r2 <= 8'd0;

end else if(divider_data_en == 1'b1)begin

divider_data_r <= divider_data;

divider_data_r2 <= divider_data_r;

end

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

count_data <= 11'd0;

else if(divider_data_en == 1'b1)

count_data <= divider_data_r2[23:8] - divider_data[23:8] + 100;

else

count_data <= count_data;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

dout <= 8'd0;

else if(count_data > 255)

dout <= 8'd255;

else if(count_data < 0)

dout <= 8'd0;

else

dout <= count_data[7:0];

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

data_wr_en <= 1'b0;

else

data_wr_en <= divider_data_en;

div_gen_0 div_gen_0_inst (

.aclk (sclk ), // input wire aclk

.s_axis_divisor_tvalid (rgb_data_en_r ), // input wire s_axis_divisor_tvalid

.s_axis_divisor_tdata (8'd3 ), // input wire [7 : 0] s_axis_divisor_tdata

.s_axis_dividend_tvalid (rgb_data_en_r ), // input wire s_axis_dividend_tvalid

.s_axis_dividend_tdata (gray_data ), // input wire [15 : 0] s_axis_dividend_tdata

.m_axis_dout_tvalid (divider_data_en ), // output wire m_axis_dout_tvalid

.m_axis_dout_tdata (divider_data ) // output wire [23 : 0] m_axis_dout_tdata

);

endmodule

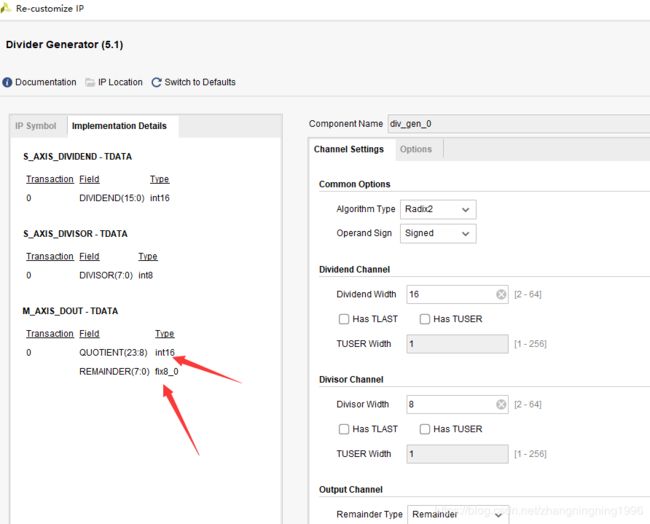

1、除法器的输出为什么使用了前16位,这里是引文后面的8位是小数位:

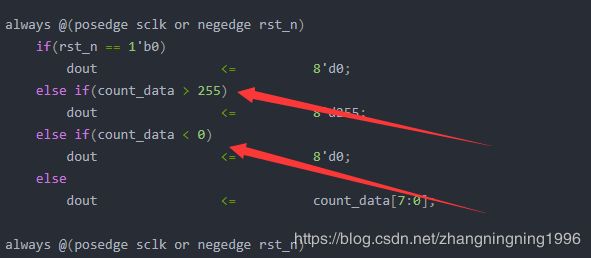

2、这里要使用下面的判断:

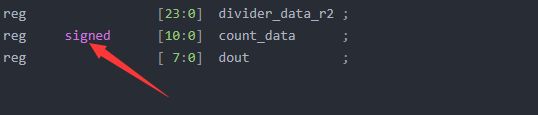

count_data必须在程序中定义成有符号数。

FPGA工程代码

这里为了方便大家的学习,我们给出整个FPGA工程的代码,整个项目的流程参考前面的SOBEL边缘检测部分,这里不多家赘述:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : top.v

// Create Time : 2020-03-01 20:33:42

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module top(

//System Interfaces

input sclk ,

input rst_n ,

//DDR3 Interfaces

output wire [13:0] ddr3_addr ,

output wire [ 2:0] ddr3_ba ,

output wire ddr3_cas_n ,

output wire ddr3_ck_n ,

output wire ddr3_ck_p ,

output wire ddr3_cke ,

output wire ddr3_ras_n ,

output wire ddr3_reset_n ,

output wire ddr3_we_n ,

inout [31:0] ddr3_dq ,

inout [ 3:0] ddr3_dqs_n ,

inout [ 3:0] ddr3_dqs_p ,

output wire [ 0:0] ddr3_cs_n ,

output wire [ 3:0] ddr3_dm ,

output wire [ 0:0] ddr3_odt ,

//Gigbit Interfaces

output wire phy_rst_n ,

input [ 3:0] rx_data ,

input rx_ctrl ,

input rx_clk ,

//USB3 Interfaces

output wire USBSS_EN ,

input USB_clk ,

inout [15:0] data ,

inout [ 1:0] be ,

input rxf_n ,

input txf_n ,

output wire oe_n ,

output wire wr_n ,

output wire siwu_n ,

output wire rd_n ,

output wire wakeup ,

output wire [ 1:0] gpio

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

//clk_wiz_0_inst

wire clk_200m ;

wire locked ;

wire clk_125m ;

//ddr3_drive_inst

wire init_calib_complete ;

wire c3_p0_cmd_clk ;

wire c3_p0_cmd_en ;

wire [ 2:0] c3_p0_cmd_instr ;

wire [27:0] c3_p0_cmd_byte_addr ;

wire [ 6:0] c3_p0_cmd_bl ;

wire c3_p0_wr_clk ;

wire c3_p0_wr_en ;

wire [31:0] c3_p0_wr_mask ;

wire [255:0] c3_p0_wr_data ;

wire [10:0] c3_p0_wr_count ;

wire c3_p1_cmd_clk ;

wire c3_p1_cmd_en ;

wire [ 2:0] c3_p1_cmd_instr ;

wire [27:0] c3_p1_cmd_byte_addr ;

wire [ 6:0] c3_p1_cmd_bl ;

wire c3_p1_rd_clk ;

wire c3_p1_rd_en ;

wire [255:0] c3_p1_rd_data ;

wire [10:0] c3_p1_rd_count ;

//sensor_data_gen_inst

wire clk_24m ;

wire data_wr_en ;

wire [31:0] data_wr ;

//usb3_drive_inst

wire [15:0] data_in ;

wire data_req ;

wire [ 7:0] image_data ;

wire image_data_en ;

wire [31:0] rlst ;

wire rlst_flag ;

wire [31:0] rgb_data ;

wire rgb_data_en ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

clk_wiz_0 clk_wiz_0_inst(

// Clock out ports

.clk_out1 (clk_200m ), // output clk_out1

.clk_out2 (clk_125m ),

.clk_out3 (clk_50m ),

// Status and control signals

.reset (~rst_n ), // input reset

.locked (locked ), // output locked

// Clock in ports

.clk_in1 (sclk )

); // input clk_in1

ddr3_top ddr3_top_inst(

//System Interfaces

.rst_n (rst_n ),

.locked (locked ),

.clk_200m (clk_200m ),

//DDR3 Interfaces

.ddr3_addr (ddr3_addr ),

.ddr3_ba (ddr3_ba ),

.ddr3_cas_n (ddr3_cas_n ),

.ddr3_ck_n (ddr3_ck_n ),

.ddr3_ck_p (ddr3_ck_p ),

.ddr3_cke (ddr3_cke ),

.ddr3_ras_n (ddr3_ras_n ),

.ddr3_reset_n (ddr3_reset_n ),

.ddr3_we_n (ddr3_we_n ),

.ddr3_dq (ddr3_dq ),

.ddr3_dqs_n (ddr3_dqs_n ),

.ddr3_dqs_p (ddr3_dqs_p ),

.ddr3_cs_n (ddr3_cs_n ),

.ddr3_dm (ddr3_dm ),

.ddr3_odt (ddr3_odt ),

//User Interfaces

.init_calib_complete (init_calib_complete ),

.c3_p0_cmd_clk (c3_p0_cmd_clk ),

.c3_p0_cmd_en (c3_p0_cmd_en ),

.c3_p0_cmd_bl (c3_p0_cmd_bl ),

.c3_p0_cmd_byte_addr (c3_p0_cmd_byte_addr ),

.c3_p0_cmd_empty ( ),

.c3_p0_cmd_full ( ),

.c3_p0_wr_clk (c3_p0_wr_clk ),

.c3_p0_wr_en (c3_p0_wr_en ),

.c3_p0_wr_mask (c3_p0_wr_mask ),

.c3_p0_wr_data (c3_p0_wr_data ),

.c3_p0_wr_full ( ),

.c3_p0_wr_empty ( ),

.c3_p0_wr_count (c3_p0_wr_count ),

.c3_p1_cmd_clk ('d0 ),

.c3_p1_cmd_en ('d0 ),

.c3_p1_cmd_bl ('d0 ),

.c3_p1_cmd_byte_addr ('d0 ),

.c3_p1_cmd_empty ( ),

.c3_p1_cmd_full ( ),

.c3_p1_wr_clk ('d0 ),

.c3_p1_wr_en ('d0 ),

.c3_p1_wr_mask ('d0 ),

.c3_p1_wr_data ('d0 ),

.c3_p1_wr_full ( ),

.c3_p1_wr_empty ( ),

.c3_p1_wr_count ( ),

.c3_p2_cmd_clk (c3_p1_cmd_clk ),

.c3_p2_cmd_en (c3_p1_cmd_en ),

.c3_p2_cmd_bl (c3_p1_cmd_bl ),

.c3_p2_cmd_byte_addr (c3_p1_cmd_byte_addr ),

.c3_p2_cmd_empty ( ),

.c3_p2_cmd_full ( ),

.c3_p2_rd_clk (c3_p1_rd_clk ),

.c3_p2_rd_en (c3_p1_rd_en ),

.c3_p2_rd_data (c3_p1_rd_data ),

.c3_p2_rd_full ( ),

.c3_p2_rd_empty ( ),

.c3_p2_rd_count (c3_p1_rd_count ),

.c3_p3_cmd_clk ('d0 ),

.c3_p3_cmd_en ('d0 ),

.c3_p3_cmd_bl ('d0 ),

.c3_p3_cmd_byte_addr ('d0 ),

.c3_p3_cmd_empty ( ),

.c3_p3_cmd_full ( ),

.c3_p3_rd_clk ('d0 ),

.c3_p3_rd_en ('d0 ),

.c3_p3_rd_data ( ),

.c3_p3_rd_full ( ),

.c3_p3_rd_empty ( ),

.c3_p3_rd_count ( )

);

ddr3_drive ddr3_drive_inst(

//System Interfaces

.rst_n (init_calib_complete ),

//DDR3 Interfaces

.c3_p0_cmd_clk (c3_p0_cmd_clk ),

.c3_p0_cmd_en (c3_p0_cmd_en ),

.c3_p0_cmd_instr (c3_p0_cmd_instr ),

.c3_p0_cmd_byte_addr (c3_p0_cmd_byte_addr ),

.c3_p0_cmd_bl (c3_p0_cmd_bl ),

.c3_p0_wr_clk (c3_p0_wr_clk ),

.c3_p0_wr_en (c3_p0_wr_en ),

.c3_p0_wr_mask (c3_p0_wr_mask ),

.c3_p0_wr_data (c3_p0_wr_data ),

.c3_p0_wr_count (c3_p0_wr_count ),

.c3_p1_cmd_clk (c3_p1_cmd_clk ),

.c3_p1_cmd_en (c3_p1_cmd_en ),

.c3_p1_cmd_instr (c3_p1_cmd_instr ),

.c3_p1_cmd_byte_addr (c3_p1_cmd_byte_addr ),

.c3_p1_cmd_bl (c3_p1_cmd_bl ),

.c3_p1_rd_clk (c3_p1_rd_clk ),

.c3_p1_rd_en (c3_p1_rd_en ),

.c3_p1_rd_data (c3_p1_rd_data ),

.c3_p1_rd_count (c3_p1_rd_count ),

//Write DDR3

.clk_24m (clk_125m ),

.data_wr_en (data_wr_en ),

.data_wr (data_wr ),

////Read DDR3

.USB_clk (USB_clk ),

.wr_n (data_req ),

.data_in (data_in )

);

gbit_top gbit_top_inst(

//System Interfaces

.clk_50m (clk_50m ),

.clk_125m (clk_125m ),

.rst_n (locked ),

//Gigbit Interfaces

.phy_rst_n (phy_rst_n ),

.rx_data (rx_data ),

.rx_ctrl (rx_ctrl ),

.rx_clk (rx_clk ),

//Communication Interfaces

.image_data (image_data ),

.image_data_en (image_data_en ),

.rlst (rlst ),

.rlst_flag (rlst_flag )

);

conver_bit conver_bit_inst(

//System Interfaces

.sclk (clk_125m ),

.rst_n (locked ),

//Gigbit Interfaces

.image_data (image_data ),

.image_data_en (image_data_en ),

//Communication Interfaces

.rgb_data (rgb_data ),

.rgb_data_en (rgb_data_en )

);

image image_inst(

//System Interfaces

.sclk (clk_125m ),

.rst_n (locked ),

//Communication Interfaces

.rgb_data (rgb_data ),

.rgb_data_en (rgb_data_en ),

.data_wr ({data_wr[15:8],data_wr[23:16],data_wr[31:24],data_wr[7:0]} ),

.data_wr_en (data_wr_en )

);

//sensor_data_gen sensor_data_gen_inst(

// .clk (clk_24m ),

// .rst_n (init_calib_complete ),

// .rgb ({data_wr[15:0],data_wr[31:16]} ),

// .de (data_wr_en ),

// .vsync ( ),

// .hsync ( )

//);

//lways @(posedge clk_24m)

// if(init_calib_complete == 1'b0)

// data_wr_en <= 1'b0;

// else

// data_wr_en <= 1'b1;

//lways @(posedge clk_24m)

// if(init_calib_complete == 1'b0)

// data_wr <= 32'd0;

// else if(data_wr_en == 1'b1)

// data_wr <= data_wr + 1'b1;

usb3_drive usb3_drive_inst(

//System Interfaces

.rst_n (init_calib_complete ),

//USB3 Interfaces

.USBSS_EN (USBSS_EN ),

.sclk (USB_clk ),

.data (data ),

.be (be ),

.rxf_n (rxf_n ),

.txf_n (txf_n ),

.oe_n (oe_n ),

.wr_n (wr_n ),

.siwu_n (siwu_n ),

.rd_n (rd_n ),

.wakeup (wakeup ),

.gpio (gpio ),

//Communication Interfaces

.data_in (data_in ),

.data_req (data_req )

);

//========================================================================================\

//******************************* Debug **********************************

//========================================================================================/

ila_3 ila_3_inst (

.clk (clk_125m ), // input wire clk

.probe0 (image_data ), // input wire [7:0] probe0

.probe1 (image_data_en ), // input wire [0:0] probe1

.probe2 (data_wr ), // input wire [31:0] probe2

.probe3 (data_wr_en ) // input wire [0:0] probe3

);

endmodule

ddr3_top模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : ddr3_top.v

// Create Time : 2020-02-27 23:16:16

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module ddr3_top(

//System Interfaces

input rst_n ,

input locked ,

input clk_200m ,

//DDR3 Interfaces

output wire [13:0] ddr3_addr ,

output wire [ 2:0] ddr3_ba ,

output wire ddr3_cas_n ,

output wire ddr3_ck_n ,

output wire ddr3_ck_p ,

output wire ddr3_cke ,

output wire ddr3_ras_n ,

output wire ddr3_reset_n ,

output wire ddr3_we_n ,

inout [31:0] ddr3_dq ,

inout [ 3:0] ddr3_dqs_n ,

inout [ 3:0] ddr3_dqs_p ,

output wire [ 0:0] ddr3_cs_n ,

output wire [ 3:0] ddr3_dm ,

output wire [ 0:0] ddr3_odt ,

//User Interfaces

output wire init_calib_complete ,

input c3_p0_cmd_clk ,

input c3_p0_cmd_en ,

input [ 6:0] c3_p0_cmd_bl ,

input [27:0] c3_p0_cmd_byte_addr ,

output wire c3_p0_cmd_empty ,

output wire c3_p0_cmd_full ,

input c3_p0_wr_clk ,

input c3_p0_wr_en ,

input [31:0] c3_p0_wr_mask ,

input [255:0] c3_p0_wr_data ,

output wire c3_p0_wr_full ,

output wire c3_p0_wr_empty ,

output wire [10:0] c3_p0_wr_count ,

input c3_p1_cmd_clk ,

input c3_p1_cmd_en ,

input [ 6:0] c3_p1_cmd_bl ,

input [27:0] c3_p1_cmd_byte_addr ,

output wire c3_p1_cmd_empty ,

output wire c3_p1_cmd_full ,

input c3_p1_wr_clk ,

input c3_p1_wr_en ,

input [31:0] c3_p1_wr_mask ,

input [255:0] c3_p1_wr_data ,

output wire c3_p1_wr_full ,

output wire c3_p1_wr_empty ,

output wire [10:0] c3_p1_wr_count ,

input c3_p2_cmd_clk ,

input c3_p2_cmd_en ,

input [ 6:0] c3_p2_cmd_bl ,

input [27:0] c3_p2_cmd_byte_addr ,

output wire c3_p2_cmd_empty ,

output wire c3_p2_cmd_full ,

input c3_p2_rd_clk ,

input c3_p2_rd_en ,

output wire [255:0] c3_p2_rd_data ,

output wire c3_p2_rd_full ,

output wire c3_p2_rd_empty ,

output wire [10:0] c3_p2_rd_count ,

input c3_p3_cmd_clk ,

input c3_p3_cmd_en ,

input [ 6:0] c3_p3_cmd_bl ,

input [27:0] c3_p3_cmd_byte_addr ,

output wire c3_p3_cmd_empty ,

output wire c3_p3_cmd_full ,

input c3_p3_rd_clk ,

input c3_p3_rd_en ,

output wire [255:0] c3_p3_rd_data ,

output wire c3_p3_rd_full ,

output wire c3_p3_rd_empty ,

output wire [10:0] c3_p3_rd_count

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

//mig_7series_0_inst

wire [27:0] app_addr ;

wire [ 2:0] app_cmd ;

wire app_en ;

wire [255:0] app_wdf_data ;

wire app_wdf_end ;

wire app_wdf_wren ;

wire [255:0] app_rd_data ;

wire app_rd_data_end ;

wire app_rd_data_valid ;

wire app_rdy ;

wire app_wdf_rdy ;

wire [31:0] app_wdf_mask ;

wire ui_clk ;

wire ui_clk_sync_rst ;

//a7_wr_ctrl_inst1

wire app_en_wr1 ;

wire [ 3:0] app_cmd_wr1 ;

wire [27:0] app_addr_wr1 ;

wire app_wdf_wren_wr1 ;

wire [255:0] app_wdf_data_wr1 ;

wire [31:0] app_wdf_mask_wr1 ;

wire app_wdf_end_wr1 ;

wire a7_wr_start_wr1 ;

wire [ 6:0] a7_wr_bl_wr1 ;

wire [27:0] a7_wr_init_addr_wr1 ;

wire [255:0] a7_wr_data_wr1 ;

wire [31:0] a7_wr_mask_wr1 ;

wire a7_wr_end_wr1 ;

wire a7_wr_req_wr1 ;

//a7_wr_ctrl_inst2

wire app_en_wr2 ;

wire [ 3:0] app_cmd_wr2 ;

wire [27:0] app_addr_wr2 ;

wire app_wdf_wren_wr2 ;

wire [255:0] app_wdf_data_wr2 ;

wire [31:0] app_wdf_mask_wr2 ;

wire app_wdf_end_wr2 ;

wire a7_wr_start_wr2 ;

wire [ 6:0] a7_wr_bl_wr2 ;

wire [27:0] a7_wr_init_addr_wr2 ;

wire [255:0] a7_wr_data_wr2 ;

wire [31:0] a7_wr_mask_wr2 ;

wire a7_wr_end_wr2 ;

wire a7_wr_req_wr2 ;

//a7_rd_ctrl_inst1

wire app_en_rd1 ;

wire [ 3:0] app_cmd_rd1 ;

wire [27:0] app_addr_rd1 ;

wire app_rd_data_valid_rd1 ;

wire a7_rd_start_rd1 ;

wire [ 6:0] a7_rd_bl_rd1 ;

wire [27:0] a7_rd_init_addr_rd1 ;

wire [255:0] a7_rd_data_rd1 ;

wire a7_rd_data_valid_rd1 ;

wire a7_rd_end_rd1 ;

//a7_rd_ctrl_inst2

wire app_en_rd2 ;

wire [ 3:0] app_cmd_rd2 ;

wire [27:0] app_addr_rd2 ;

wire app_rd_data_valid_rd2 ;

wire a7_rd_start_rd2 ;

wire [ 6:0] a7_rd_bl_rd2 ;

wire [27:0] a7_rd_init_addr_rd2 ;

wire [255:0] a7_rd_data_rd2 ;

wire a7_rd_data_valid_rd2 ;

wire a7_rd_end_rd2 ;

//arbit_inst

//wire c3_p0_cmd_empty ;

//wire c3_p1_cmd_empty ;

//wire c3_p2_cmd_empty ;

//wire c3_p3_cmd_empty ;

//rst delay

reg [ 5:0] rst_cnt ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

always @(posedge clk_200m or negedge rst_n)

if(rst_n == 1'b0)

rst_cnt <= 6'b0;

else if(locked == 1'b0)

rst_cnt <= 6'b0;

else if(rst_cnt[5] == 1'b0)

rst_cnt <= rst_cnt + 1'b1;

mig_7series_0 mig_7series_0_inst (

// Memory interface ports

.ddr3_addr (ddr3_addr ), // output [13:0] ddr3_addr

.ddr3_ba (ddr3_ba ), // output [2:0] ddr3_ba

.ddr3_cas_n (ddr3_cas_n ), // output ddr3_cas_n

.ddr3_ck_n (ddr3_ck_n ), // output [0:0] ddr3_ck_n

.ddr3_ck_p (ddr3_ck_p ), // output [0:0] ddr3_ck_p

.ddr3_cke (ddr3_cke ), // output [0:0] ddr3_cke

.ddr3_ras_n (ddr3_ras_n ), // output ddr3_ras_n

.ddr3_reset_n (ddr3_reset_n ), // output ddr3_reset_n

.ddr3_we_n (ddr3_we_n ), // output ddr3_we_n

.ddr3_dq (ddr3_dq ), // inout [31:0] ddr3_dq

.ddr3_dqs_n (ddr3_dqs_n ), // inout [3:0] ddr3_dqs_n

.ddr3_dqs_p (ddr3_dqs_p ), // inout [3:0] ddr3_dqs_p

.init_calib_complete (init_calib_complete ), // output init_calib_complete

.ddr3_cs_n (ddr3_cs_n ), // output [0:0] ddr3_cs_n

.ddr3_dm (ddr3_dm ), // output [3:0] ddr3_dm

.ddr3_odt (ddr3_odt ), // output [0:0] ddr3_odt

// Application interface ports

.app_addr (app_addr ), // input [27:0] app_addr

.app_cmd (app_cmd ), // input [2:0] app_cmd

.app_en (app_en ), // input app_en

.app_wdf_data (app_wdf_data ), // input [255:0] app_wdf_data

.app_wdf_end (app_wdf_end ), // input app_wdf_end

.app_wdf_wren (app_wdf_wren ), // input app_wdf_wren

.app_rd_data (app_rd_data ), // output [255:0] app_rd_data

.app_rd_data_end (app_rd_data_end ), // output app_rd_data_end

.app_rd_data_valid (app_rd_data_valid ), // output app_rd_data_valid

.app_rdy (app_rdy ), // output app_rdy

.app_wdf_rdy (app_wdf_rdy ), // output app_wdf_rdy

.app_sr_req (1'b0 ), // input app_sr_req

.app_ref_req (1'b0 ), // input app_ref_req

.app_zq_req (1'b0 ), // input app_zq_req

.app_sr_active ( ), // output app_sr_active

.app_ref_ack ( ), // output app_ref_ack

.app_zq_ack ( ), // output app_zq_ack

.ui_clk (ui_clk ), // output ui_clk

.ui_clk_sync_rst (ui_clk_sync_rst ), // output ui_clk_sync_rst

.app_wdf_mask (app_wdf_mask ), // input [31:0] app_wdf_mask

// System Clock Ports

.sys_clk_i (clk_200m ),

.sys_rst (locked ) // input sys_rst

);

arbit arbit_inst(

//System Interfaces

.rst_n (init_calib_complete ),

//DDR3 Interfaces

.ui_clk (ui_clk ),

.app_addr (app_addr ),

.app_cmd (app_cmd ),

.app_en (app_en ),

.app_wdf_data (app_wdf_data ),

.app_wdf_end (app_wdf_end ),

.app_wdf_wren (app_wdf_wren ),

.app_rd_data_valid (app_rd_data_valid ),

.app_wdf_mask (app_wdf_mask ),

//a7_wr_ctrl_inst1

.app_en_wr1 (app_en_wr1 ),

.app_cmd_wr1 (app_cmd_wr1 ),

.app_addr_wr1 (app_addr_wr1 ),

.app_wdf_wren_wr1 (app_wdf_wren_wr1 ),

.app_wdf_data_wr1 (app_wdf_data_wr1 ),

.app_wdf_mask_wr1 (app_wdf_mask_wr1 ),

.app_wdf_end_wr1 (app_wdf_end_wr1 ),

.a7_wr_start_w1 (a7_wr_start_wr1 ),

.a7_wr_end_wr1 (a7_wr_end_wr1 ),

.c3_p0_cmd_empty (c3_p0_cmd_empty ),

//a7_wr_ctrl_inst1

.app_en_wr2 (app_en_wr2 ),

.app_cmd_wr2 (app_cmd_wr2 ),

.app_addr_wr2 (app_addr_wr2 ),

.app_wdf_wren_wr2 (app_wdf_wren_wr2 ),

.app_wdf_data_wr2 (app_wdf_data_wr2 ),

.app_wdf_mask_wr2 (app_wdf_mask_wr2 ),

.app_wdf_end_wr2 (app_wdf_end_wr2 ),

.a7_wr_start_w2 (a7_wr_start_wr2 ),

.a7_wr_end_wr2 (a7_wr_end_wr2 ),

.c3_p1_cmd_empty (c3_p1_cmd_empty ),

//a7_rd_ctrl_inst1

.app_en_rd1 (app_en_rd1 ),

.app_cmd_rd1 (app_cmd_rd1 ),

.app_addr_rd1 (app_addr_rd1 ),

.app_rd_data_valid_rd1 (app_rd_data_valid_rd1 ),

.a7_rd_start_rd1 (a7_rd_start_rd1 ),

.a7_rd_end_rd1 (a7_rd_end_rd1 ),

.c3_p2_cmd_empty (c3_p2_cmd_empty ),

//a7_rd_ctrl_inst2

.app_en_rd2 (app_en_rd2 ),

.app_cmd_rd2 (app_cmd_rd2 ),

.app_addr_rd2 (app_addr_rd2 ),

.app_rd_data_valid_rd2 (app_rd_data_valid_rd2 ),

.a7_rd_start_rd2 (a7_rd_start_rd2 ),

.a7_rd_end_rd2 (a7_rd_end_rd2 ),

.c3_p3_cmd_empty (c3_p3_cmd_empty )

);

a7_wr_ctrl a7_wr_ctrl_inst1(

//System Interfaces

.rst_n (init_calib_complete ),

//DDR3 Interfaces

.ui_clk (ui_clk ),

.app_rdy (app_rdy ),

.app_wdf_rdy (app_wdf_rdy ),

.app_en (app_en_wr1 ),

.app_cmd (app_cmd_wr1 ),

.app_addr (app_addr_wr1 ),

.app_wdf_wren (app_wdf_wren_wr1 ),

.app_wdf_data (app_wdf_data_wr1 ),

.app_wdf_mask (app_wdf_mask_wr1 ),

.app_wdf_end (app_wdf_end_wr1 ),

//Communication Interfaces

.a7_wr_start (a7_wr_start_wr1 ),

.a7_wr_bl (a7_wr_bl_wr1 ),

.a7_wr_init_addr (a7_wr_init_addr_wr1 ),

.a7_wr_data (a7_wr_data_wr1 ),

.a7_wr_mask (a7_wr_mask_wr1 ),

.a7_wr_end (a7_wr_end_wr1 ),

.a7_wr_req (a7_wr_req_wr1 )

);

fifo_generator_0 cmd_wr1_fifo (

.rst (~init_calib_complete ), // input wire rst

.wr_clk (c3_p0_cmd_clk ), // input wire wr_clk

.rd_clk (ui_clk ), // input wire rd_clk

.din ({c3_p0_cmd_bl,c3_p0_cmd_byte_addr}), // input wire [38 : 0] din

.wr_en (c3_p0_cmd_en ), // input wire wr_en

.rd_en (a7_wr_start_wr1 ), // input wire rd_en

.dout ({a7_wr_bl_wr1,a7_wr_init_addr_wr1}), // output wire [38 : 0] dout

.full (c3_p0_cmd_full ), // output wire full

.empty (c3_p0_cmd_empty )

);

fifo_generator_1 data_wr1_fifo (

.rst (~init_calib_complete ), // input wire rst

.wr_clk (c3_p0_wr_clk ), // input wire wr_clk

.rd_clk (ui_clk ), // input wire rd_clk

.din ({c3_p0_wr_mask,c3_p0_wr_data} ), // input wire [287 : 0] din

.wr_en (c3_p0_wr_en ), // input wire wr_en

.rd_en (a7_wr_req_wr1 ), // input wire rd_en

.dout ({a7_wr_mask_wr1,a7_wr_data_wr1}), // output wire [287 : 0] dout

.full (c3_p0_wr_full ), // output wire full

.empty (c3_p0_wr_empty ), // output wire empty

.wr_data_count (c3_p0_wr_count ) // output wire [10 : 0] wr_data_count

);

a7_wr_ctrl a7_wr_ctrl_inst2(

//System Interfaces

.rst_n (init_calib_complete ),

//DDR3 Interfaces

.ui_clk (ui_clk ),

.app_rdy (app_rdy ),

.app_wdf_rdy (app_wdf_rdy ),

.app_en (app_en_wr2 ),

.app_cmd (app_cmd_wr2 ),

.app_addr (app_addr_wr2 ),

.app_wdf_wren (app_wdf_wren_wr2 ),

.app_wdf_data (app_wdf_data_wr2 ),

.app_wdf_mask (app_wdf_mask_wr2 ),

.app_wdf_end (app_wdf_end_wr2 ),

//Communication Interfaces

.a7_wr_start (a7_wr_start_wr2 ),

.a7_wr_bl (a7_wr_bl_wr2 ),

.a7_wr_init_addr (a7_wr_init_addr_wr2 ),

.a7_wr_data (a7_wr_data_wr2 ),

.a7_wr_mask (a7_wr_mask_wr2 ),

.a7_wr_end (a7_wr_end_wr2 ),

.a7_wr_req (a7_wr_req_wr2 )

);

fifo_generator_0 cmd_wr2_fifo (

.rst (~init_calib_complete ), // input wire rst

.wr_clk (c3_p1_cmd_clk ), // input wire wr_clk

.rd_clk (ui_clk ), // input wire rd_clk

.din ({c3_p1_cmd_bl,c3_p1_cmd_byte_addr}), // input wire [38 : 0] din

.wr_en (c3_p1_cmd_en ), // input wire wr_en

.rd_en (a7_wr_start_wr2 ), // input wire rd_en

.dout ({a7_wr_bl_wr2,a7_wr_init_addr_wr2}), // output wire [38 : 0] dout

.full (c3_p1_cmd_full ), // output wire full

.empty (c3_p1_cmd_empty )

);

fifo_generator_1 data_wr2_fifo (

.rst (~init_calib_complete ), // input wire rst

.wr_clk (c3_p1_wr_clk ), // input wire wr_clk

.rd_clk (ui_clk ), // input wire rd_clk

.din ({c3_p1_wr_mask,c3_p1_wr_data} ), // input wire [287 : 0] din

.wr_en (c3_p1_wr_en ), // input wire wr_en

.rd_en (a7_wr_req_wr2 ), // input wire rd_en

.dout ({a7_wr_mask_wr2,a7_wr_data_wr2}), // output wire [287 : 0] dout

.full (c3_p1_wr_full ), // output wire full

.empty (c3_p1_wr_empty ), // output wire empty

.wr_data_count (c3_p1_wr_count ) // output wire [10 : 0] wr_data_count

);

a7_rd_ctrl a7_rd_ctrl_inst1(

//System Interfaces

.rst_n (init_calib_complete ),

//DDR3 Interfaces

.ui_clk (ui_clk ),

.app_en (app_en_rd1 ),

.app_cmd (app_cmd_rd1 ),

.app_addr (app_addr_rd1 ),

.app_rd_data (app_rd_data ),

.app_rd_data_valid (app_rd_data_valid_rd1 ),

.app_rdy (app_rdy ),

//Communication Interfaces

.a7_rd_start (a7_rd_start_rd1 ),

.a7_rd_bl (a7_rd_bl_rd1 ),

.a7_rd_init_addr (a7_rd_init_addr_rd1 ),

.a7_rd_data (a7_rd_data_rd1 ),

.a7_rd_data_valid (a7_rd_data_valid_rd1 ),

.a7_rd_end (a7_rd_end_rd1 )

);

fifo_generator_0 cmd_rd1_fifo (

.rst (~rst_cnt[5] ), // input wire rst

.wr_clk (c3_p2_cmd_clk ), // input wire wr_clk

.rd_clk (ui_clk ), // input wire rd_clk

.din ({c3_p2_cmd_bl,c3_p2_cmd_byte_addr}), // input wire [38 : 0] din

.wr_en (c3_p2_cmd_en ), // input wire wr_en

.rd_en (a7_rd_start_rd1 ), // input wire rd_en

.dout ({a7_rd_bl_rd1,a7_rd_init_addr_rd1}), // output wire [38 : 0] dout

.full (c3_p2_cmd_full ), // output wire full

.empty (c3_p2_cmd_empty )

);

fifo_generator_2 data_rd1_fifo (

.rst (~rst_cnt[5] ), // input wire rst

.wr_clk (ui_clk ), // input wire wr_clk

.rd_clk (c3_p2_rd_clk ), // input wire rd_clk

.din (a7_rd_data_rd1 ), // input wire [255 : 0] din

.wr_en (a7_rd_data_valid_rd1 ), // input wire wr_en

.rd_en (c3_p2_rd_en ), // input wire rd_en

.dout (c3_p2_rd_data ), // output wire [255 : 0] dout

.full (c3_p2_rd_full ), // output wire full

.empty (c3_p2_rd_empty ), // output wire empty

.rd_data_count (c3_p2_rd_count ) // output wire [10 : 0] rd_data_count

);

a7_rd_ctrl a7_rd_ctrl_inst2(

//System Interfaces

.rst_n (init_calib_complete ),

//DDR3 Interfaces

.ui_clk (ui_clk ),

.app_en (app_en_rd2 ),

.app_cmd (app_cmd_rd2 ),

.app_addr (app_addr_rd2 ),

.app_rd_data (app_rd_data ),

.app_rd_data_valid (app_rd_data_valid_rd2 ),

.app_rdy (app_rdy ),

//Communication Interfaces

.a7_rd_start (a7_rd_start_rd2 ),

.a7_rd_bl (a7_rd_bl_rd2 ),

.a7_rd_init_addr (a7_rd_init_addr_rd2 ),

.a7_rd_data (a7_rd_data_rd2 ),

.a7_rd_data_valid (a7_rd_data_valid_rd2 ),

.a7_rd_end (a7_rd_end_rd2 )

);

fifo_generator_0 cmd_rd2_fifo (

.rst (~rst_cnt[5] ), // input wire rst

.wr_clk (c3_p3_cmd_clk ), // input wire wr_clk

.rd_clk (ui_clk ), // input wire rd_clk

.din ({c3_p3_cmd_bl,c3_p3_cmd_byte_addr}), // input wire [38 : 0] din

.wr_en (c3_p3_cmd_en ), // input wire wr_en

.rd_en (a7_rd_start_rd2 ), // input wire rd_en

.dout ({a7_rd_bl_rd2,a7_rd_init_addr_rd2}), // output wire [38 : 0] dout

.full (c3_p3_cmd_full ), // output wire full

.empty (c3_p3_cmd_empty )

);

fifo_generator_2 data_rd2_fifo (

.rst (~rst_cnt[5] ), // input wire rst

.wr_clk (ui_clk ), // input wire wr_clk

.rd_clk (c3_p3_rd_clk ), // input wire rd_clk

.din (a7_rd_data_rd2 ), // input wire [255 : 0] din

.wr_en (a7_rd_data_valid_rd2 ), // input wire wr_en

.rd_en (c3_p3_rd_en ), // input wire rd_en

.dout (c3_p3_rd_data ), // output wire [255 : 0] dout

.full (c3_p3_rd_full ), // output wire full

.empty (c3_p3_rd_empty ), // output wire empty

.rd_data_count (c3_p3_rd_count ) // output wire [10 : 0] rd_data_count

);

endmodule

arbit模块:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2020/03/01 15:17:14

// Design Name:

// Module Name: arbit

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module arbit(

//System Interfaces

input rst_n ,

//DDR3 Interfaces

input ui_clk ,

output reg [27:0] app_addr ,

output reg [ 2:0] app_cmd ,

output reg app_en ,

output reg [255:0] app_wdf_data ,

output reg app_wdf_end ,

output reg app_wdf_wren ,

input app_rd_data_valid ,

output reg [31:0] app_wdf_mask ,

//a7_wr_ctrl_inst1

input app_en_wr1 ,

input [ 3:0] app_cmd_wr1 ,

input [27:0] app_addr_wr1 ,

input app_wdf_wren_wr1 ,

input [255:0] app_wdf_data_wr1 ,

input [31:0] app_wdf_mask_wr1 ,

input app_wdf_end_wr1 ,

output reg a7_wr_start_w1 ,

input a7_wr_end_wr1 ,

input c3_p0_cmd_empty ,

//a7_wr_ctrl_inst1

input app_en_wr2 ,

input [ 3:0] app_cmd_wr2 ,

input [27:0] app_addr_wr2 ,

input app_wdf_wren_wr2 ,

input [255:0] app_wdf_data_wr2 ,

input [31:0] app_wdf_mask_wr2 ,

input app_wdf_end_wr2 ,

output reg a7_wr_start_w2 ,

input a7_wr_end_wr2 ,

input c3_p1_cmd_empty ,

//a7_rd_ctrl_inst1

input app_en_rd1 ,

input [ 3:0] app_cmd_rd1 ,

input [27:0] app_addr_rd1 ,

output reg app_rd_data_valid_rd1 ,

output reg a7_rd_start_rd1 ,

input a7_rd_end_rd1 ,

input c3_p2_cmd_empty ,

//a7_rd_ctrl_inst2

input app_en_rd2 ,

input [ 3:0] app_cmd_rd2 ,

input [27:0] app_addr_rd2 ,

output reg app_rd_data_valid_rd2 ,

output reg a7_rd_start_rd2 ,

input a7_rd_end_rd2 ,

input c3_p3_cmd_empty

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

parameter IDLE = 6'b000001 ;

parameter ARBIT = 6'b000010 ;

parameter WR1 = 6'b000100 ;

parameter WR2 = 6'b001000 ;

parameter RD1 = 6'b010000 ;

parameter RD2 = 6'b100000 ;

reg [ 5:0] state ;

reg [ 2:0] rand_cnt ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

rand_cnt <= 3'd0;

else if(rand_cnt == 3'd3)

rand_cnt <= 3'd0;

else

rand_cnt <= rand_cnt + 1'b1;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

state <= IDLE;

else case(state)

IDLE : state <= ARBIT;

ARBIT : if(c3_p0_cmd_empty == 1'b0 && rand_cnt == 3'd0)

state <= WR1;

else if(c3_p1_cmd_empty == 1'b0 && rand_cnt == 3'd1)

state <= WR2;

else if(c3_p2_cmd_empty == 1'b0 && rand_cnt == 3'd2)

state <= RD1;

else if(c3_p3_cmd_empty == 1'b0 && rand_cnt == 3'd3)

state <= RD2;

else

state <= state;

WR1 : if(a7_wr_end_wr1 == 1'b1)

state <= ARBIT;

else

state <= state;

WR2 : if(a7_wr_end_wr2 == 1'b1)

state <= ARBIT;

else

state <= state;

RD1 : if(a7_rd_end_rd1 == 1'b1)

state <= ARBIT;

else

state <= state;

RD2 : if(a7_rd_end_rd2 == 1'b1)

state <= ARBIT;

else

state <= state;

default : state <= IDLE;

endcase

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

a7_wr_start_w1 <= 1'b0;

else if(state == ARBIT && c3_p0_cmd_empty == 1'b0 && rand_cnt == 3'd0)

a7_wr_start_w1 <= 1'b1;

else

a7_wr_start_w1 <= 1'b0;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

a7_wr_start_w2 <= 1'b0;

else if(state == ARBIT && c3_p1_cmd_empty == 1'b0 && rand_cnt == 3'd1)

a7_wr_start_w2 <= 1'b1;

else

a7_wr_start_w2 <= 1'b0;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

a7_rd_start_rd1 <= 1'b0;

else if(state == ARBIT && c3_p2_cmd_empty == 1'b0 && rand_cnt == 3'd2)

a7_rd_start_rd1 <= 1'b1;

else

a7_rd_start_rd1 <= 1'b0;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

a7_rd_start_rd2 <= 1'b0;

else if(state == ARBIT && c3_p3_cmd_empty == 1'b0 && rand_cnt == 3'd3)

a7_rd_start_rd2 <= 1'b1;

else

a7_rd_start_rd2 <= 1'b0;

always @(*)

case(state)

WR1 : begin

app_addr = app_addr_wr1;

app_cmd = app_cmd_wr1;

app_en = app_en_wr1;

app_wdf_data = app_wdf_data_wr1;

app_wdf_end = app_wdf_end_wr1;

app_wdf_wren = app_wdf_wren_wr1;

app_wdf_mask = app_wdf_mask_wr1;

end

WR2 : begin

app_addr = app_addr_wr2;

app_cmd = app_cmd_wr2;

app_en = app_en_wr2;

app_wdf_data = app_wdf_data_wr2;

app_wdf_end = app_wdf_end_wr2;

app_wdf_wren = app_wdf_wren_wr2;

app_wdf_mask = app_wdf_mask_wr2;

end

RD1 : begin

app_addr = app_addr_rd1;

app_cmd = app_cmd_rd1;

app_en = app_en_rd1;

app_rd_data_valid_rd1 = app_rd_data_valid;

end

RD2 : begin

app_addr = app_addr_rd2;

app_cmd = app_cmd_rd2;

app_en = app_en_rd2;

app_rd_data_valid_rd2 = app_rd_data_valid;

end

default : begin

app_addr = 28'd0;

app_cmd = 3'd0;

app_en = 1'b0;

app_wdf_data = 256'd0;

app_wdf_end = 1'b0;

app_wdf_wren = 1'b0;

app_rd_data_valid_rd1 = 1'b0;

app_rd_data_valid_rd2 = 1'b0;

app_wdf_mask = 32'd0;

end

endcase

endmodule

a7_wr_ctrl模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : a7_wr_ctrl.v

// Create Time : 2020-02-29 22:19:50

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module a7_wr_ctrl(

//System Interfaces

input rst_n ,

//DDR3 Interfaces

input ui_clk ,

input app_rdy ,

input app_wdf_rdy ,

output wire app_en ,

output wire [ 3:0] app_cmd ,

output reg [27:0] app_addr ,

output wire app_wdf_wren ,

output wire [255:0] app_wdf_data ,

output wire [31:0] app_wdf_mask ,

output wire app_wdf_end ,

//Communication Interfaces

input a7_wr_start ,

input [ 6:0] a7_wr_bl ,

input [27:0] a7_wr_init_addr ,

input [255:0] a7_wr_data ,

input [31:0] a7_wr_mask ,

output reg a7_wr_end ,

output wire a7_wr_req

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [ 6:0] wr_bl ;

reg wr_flag ;

reg [ 6:0] bl_cnt ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

assign app_en = wr_flag && app_rdy && app_wdf_rdy;

assign app_wdf_end = app_en;

assign app_wdf_wren = app_en;

assign app_wdf_data = a7_wr_data;

assign a7_wr_req = app_en;

assign app_wdf_mask = a7_wr_mask;

assign app_cmd = 3'd0;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

wr_flag <= 1'b0;

else if(bl_cnt == wr_bl && app_en == 1'b1)

wr_flag <= 1'b0;

else if(a7_wr_start == 1'b1)

wr_flag <= 1'b1;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

wr_bl <= 7'd0;

else if(a7_wr_start == 1'b1)

wr_bl <= a7_wr_bl;

else

wr_bl <= wr_bl;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

app_addr <= 28'd0;

else if(a7_wr_start == 1'b1)

app_addr <= a7_wr_init_addr;

else if(app_en == 1'b1)

app_addr <= app_addr + 8;

else

app_addr <= app_addr;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

bl_cnt <= 7'd0;

else if(bl_cnt == wr_bl && app_en == 1'b1 && wr_flag == 1'b1)

bl_cnt <= 7'd0;

else if(wr_flag == 1'b1 && app_en == 1'b1)

bl_cnt <= bl_cnt + 1'b1;

else

bl_cnt <= bl_cnt;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

a7_wr_end <= 1'b0;

else if(bl_cnt == wr_bl && app_en == 1'b1)

a7_wr_end <= 1'b1;

else

a7_wr_end <= 1'b0;

endmodule

a7_rd_ctrl模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : a7_rd_ctrl.v

// Create Time : 2020-03-01 14:32:05

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module a7_rd_ctrl(

//System Interfaces

input rst_n ,

//DDR3 Interfaces

input ui_clk ,

output reg app_en ,

output wire [ 3:0] app_cmd ,

output reg [27:0] app_addr ,

input [255:0] app_rd_data ,

input app_rd_data_valid ,

input app_rdy ,

//Communication Interfaces

input a7_rd_start ,

input [ 6:0] a7_rd_bl ,

input [27:0] a7_rd_init_addr ,

output reg [255:0] a7_rd_data ,

output reg a7_rd_data_valid ,

output reg a7_rd_end

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [ 6:0] rd_bl ;

reg [ 6:0] cmd_cnt ;

reg rd_flag ;

reg [ 6:0] data_cnt ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

assign app_cmd = 3'd1;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

rd_bl <= 7'd0;

else if(a7_rd_start == 1'b1)

rd_bl <= a7_rd_bl;

else

rd_bl <= a7_rd_bl;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

app_en <= 1'b0;

else if(a7_rd_start == 1'b1)

app_en <= 1'b1;

else if(cmd_cnt == rd_bl && app_rdy == 1'b1)

app_en <= 1'b0;

else

app_en <= app_en;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

cmd_cnt <= 7'd0;

else if(rd_flag == 1'b1 && cmd_cnt == rd_bl && app_rdy == 1'b1)

cmd_cnt <= 7'd0;

else if(rd_flag == 1'b1 && app_rdy == 1'b1 && app_en == 1'b1)

cmd_cnt <= cmd_cnt + 1'b1;

else

cmd_cnt <= cmd_cnt;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

rd_flag <= 1'b0;

else if(a7_rd_start == 1'b1)

rd_flag <= 1'b1;

else if(data_cnt == rd_bl && app_rd_data_valid == 1'b1)

rd_flag <= 1'b0;

else

rd_flag <= rd_flag;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

app_addr <= 28'd0;

else if(a7_rd_start == 1'b1)

app_addr <= a7_rd_init_addr;

else if(app_en == 1'b1 && app_rdy == 1'b1)

app_addr <= app_addr + 8;

else

app_addr <= app_addr;

always @(posedge ui_clk)

a7_rd_data <= app_rd_data;

always @(posedge ui_clk)

a7_rd_data_valid <= app_rd_data_valid;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

a7_rd_end <= 1'b0;

else if(data_cnt == rd_bl && app_rd_data_valid == 1'b1)

a7_rd_end <= 1'b1;

else

a7_rd_end <= 1'b0;

always @(posedge ui_clk or negedge rst_n)

if(rst_n == 1'b0)

data_cnt <= 7'd0;

else if(data_cnt == rd_bl && rd_flag == 1'b1 && app_rd_data_valid == 1'b1)

data_cnt <= 7'd0;

else if(rd_flag == 1'b1 && app_rd_data_valid == 1'b1)

data_cnt <= data_cnt + 1'b1;

else

data_cnt <= data_cnt;

endmodule

ddr3_drive模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : ddr3_drive.v

// Create Time : 2020-02-22 11:41:08

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module ddr3_drive(

//System Interfaces

input rst_n ,

//Write DDR3

input clk_24m ,

input data_wr_en ,

input [31:0] data_wr ,

//Read DDR3

input USB_clk ,

input wr_n ,

output wire [15:0] data_in ,

//DDR3 Interfaces

output c3_p0_cmd_clk ,

output reg c3_p0_cmd_en ,

output wire [ 2:0] c3_p0_cmd_instr ,

output reg [27:0] c3_p0_cmd_byte_addr ,

output wire [10:0] c3_p0_cmd_bl ,

output c3_p0_wr_clk ,

output reg c3_p0_wr_en ,

output wire [31:0] c3_p0_wr_mask ,

output reg [255:0] c3_p0_wr_data ,

input [ 6:0] c3_p0_wr_count ,

output c3_p1_cmd_clk ,

output reg c3_p1_cmd_en ,

output wire [ 2:0] c3_p1_cmd_instr ,

output reg [27:0] c3_p1_cmd_byte_addr ,

output wire [ 6:0] c3_p1_cmd_bl ,

output c3_p1_rd_clk ,

output reg c3_p1_rd_en ,

input [255:0] c3_p1_rd_data ,

input [10:0] c3_p1_rd_count

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

//parameter BURST_NUM = 1048576 ;

parameter BURST_NUM = 6144 ;

parameter BURST_LENFTH = 7'd15 ;

reg [ 3:0] data_cnt ;

reg [ 6:0] wr_data_cnt ;

reg [15:0] bl_cnt ;

reg wr_n_flag ;

reg [31:0] usb_data ;

reg [ 3:0] data_cnt_rd ;

reg [15:0] bl_cnt_r ;

reg rd_first ;

reg [255:0] c3_p1_rd_data_r ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

assign c3_p0_cmd_clk = clk_24m;

assign c3_p0_wr_clk = clk_24m;

assign c3_p0_cmd_instr = 3'd0;

assign c3_p0_cmd_bl = BURST_LENFTH;

assign c3_p0_wr_mask = 32'd0;

assign data_in = wr_n_flag == 1'b0 ? usb_data[31:16] : usb_data[15:0];

assign c3_p1_cmd_clk = USB_clk;

assign c3_p1_rd_clk = USB_clk;

assign c3_p1_cmd_instr = 3'd1;

assign c3_p1_cmd_bl = BURST_LENFTH;

always @(posedge clk_24m or negedge rst_n)

if(rst_n == 1'b0)

data_cnt <= 4'd0;

else if(data_cnt == 4'd7 && data_wr_en == 1'b1)

data_cnt <= 4'd0;

else if(data_wr_en == 1'b1)

data_cnt <= data_cnt + 1'b1;

else

data_cnt <= data_cnt;

always @(posedge clk_24m or negedge rst_n)

if(rst_n == 1'b0)

c3_p0_wr_data <= 256'd0;

else if(data_wr_en == 1'b1)

c3_p0_wr_data <= {c3_p0_wr_data[223:0],data_wr};

else

c3_p0_wr_data <= c3_p0_wr_data;

always @(posedge clk_24m or negedge rst_n)

if(rst_n == 1'b0)

c3_p0_wr_en <= 1'b0;

else if(data_cnt == 4'd7 && data_wr_en == 1'b1)

c3_p0_wr_en <= 1'b1;

else

c3_p0_wr_en <= 1'b0;

always @(posedge clk_24m or negedge rst_n)

if(rst_n == 1'b0)

wr_data_cnt <= 7'd0;

else if(wr_data_cnt == BURST_LENFTH && c3_p0_wr_en == 1'b1)

wr_data_cnt <= 7'd0;

else if(c3_p0_wr_en == 1'b1)

wr_data_cnt <= wr_data_cnt + 1'b1;

else

wr_data_cnt <= wr_data_cnt;

always @(posedge clk_24m or negedge rst_n)

if(rst_n == 1'b0)

c3_p0_cmd_en <= 1'b0;

else if(wr_data_cnt == BURST_LENFTH && c3_p0_wr_en == 1'b1)

c3_p0_cmd_en <= 1'b1;

else

c3_p0_cmd_en <= 1'b0;

always @(posedge clk_24m or negedge rst_n)

if(rst_n == 1'b0)

c3_p0_cmd_byte_addr <= 28'd0;

else if(bl_cnt == BURST_NUM - 1'b1 && c3_p0_cmd_en == 1'b1)

c3_p0_cmd_byte_addr <= 28'd0;

else if(c3_p0_cmd_en == 1'b1)

c3_p0_cmd_byte_addr <= c3_p0_cmd_byte_addr + 'd128;

always @(posedge clk_24m or negedge rst_n)

if(rst_n == 1'b0)

bl_cnt <= 16'd0;

else if(bl_cnt == BURST_NUM - 1'b1 && c3_p0_cmd_en == 1'b1)

bl_cnt <= 16'd0;

else if(c3_p0_cmd_en == 1'b1)

bl_cnt <= bl_cnt + 1'b1;

else

bl_cnt <= bl_cnt;

always @(posedge USB_clk or negedge rst_n)

if(rst_n == 1'b0)

wr_n_flag <= 1'b0;

else if(wr_n == 1'b0)

wr_n_flag <= wr_n_flag + 1'b1;

else

wr_n_flag <= wr_n_flag;

always @(posedge USB_clk or negedge rst_n)

if(rst_n == 1'b0)

data_cnt_rd <= 4'd0;

else if(data_cnt_rd == 4'd7 && wr_n_flag == 1'b1 && wr_n == 1'b0)

data_cnt_rd <= 4'd0;

else if(wr_n_flag == 1'b1 && wr_n == 1'b0)

data_cnt_rd <= data_cnt_rd + 1'b1;

else

data_cnt_rd <= data_cnt_rd;

always @(posedge USB_clk or negedge rst_n)

if(rst_n == 1'b0)

rd_first <= 1'b0;

else if(c3_p1_rd_count >= BURST_LENFTH/2 && rd_first == 1'b0)

rd_first <= 1'b1;

else

rd_first <= rd_first;

always @(posedge USB_clk or negedge rst_n)

if(rst_n == 1'b0)

c3_p1_rd_en <= 1'b0;

else if(c3_p1_rd_count >= BURST_LENFTH/2 && rd_first == 1'b0)

c3_p1_rd_en <= 1'b1;

else if(data_cnt_rd == 4'd7 && wr_n_flag == 1'b1 && wr_n == 1'b0)

c3_p1_rd_en <= 1'b1;

else

c3_p1_rd_en <= 1'b0;

always @(posedge USB_clk or negedge rst_n)

if(rst_n == 1'b0)

c3_p1_cmd_en <= 1'b0;

else if(c3_p1_rd_count <= BURST_LENFTH/2)

c3_p1_cmd_en <= 1'b1;

else

c3_p1_cmd_en <= 1'b0;

always @(posedge USB_clk or negedge rst_n)

if(rst_n == 1'b0)

c3_p1_cmd_byte_addr <= 28'd0;

else if(bl_cnt_r == BURST_NUM - 1'b1 && c3_p1_cmd_en == 1'b1)

c3_p1_cmd_byte_addr <= 28'd0;

else if(c3_p1_cmd_en == 1'b1)

c3_p1_cmd_byte_addr <= c3_p1_cmd_byte_addr + 128;

else

c3_p1_cmd_byte_addr <= c3_p1_cmd_byte_addr;

always @(posedge USB_clk or negedge rst_n)

if(rst_n == 1'b0)

bl_cnt_r <= 16'd0;

else if(bl_cnt_r == BURST_NUM - 1'b1 && c3_p1_cmd_en == 1'b1)

bl_cnt_r <= 16'd0;

else if(c3_p1_cmd_en == 1'b1)

bl_cnt_r <= bl_cnt_r + 1'b1;

else

bl_cnt_r <= bl_cnt_r;

always @(posedge USB_clk or negedge rst_n)

if(rst_n == 1'b0)

c3_p1_rd_data_r <= 256'd0;

else if(c3_p1_rd_en == 1'b1)

c3_p1_rd_data_r <= c3_p1_rd_data;

else

c3_p1_rd_data_r <= c3_p1_rd_data_r;

always @(*)

if(c3_p1_rd_en == 1'b1)

usb_data <= c3_p1_rd_data[255:224];

else case(data_cnt_rd)

0 : usb_data <= c3_p1_rd_data_r[255:224];

1 : usb_data <= c3_p1_rd_data_r[223:192];

2 : usb_data <= c3_p1_rd_data_r[191:160];

3 : usb_data <= c3_p1_rd_data_r[159:128];

4 : usb_data <= c3_p1_rd_data_r[127:96];

5 : usb_data <= c3_p1_rd_data_r[95:64];

6 : usb_data <= c3_p1_rd_data_r[63:32];

7 : usb_data <= c3_p1_rd_data_r[31:0];

default : usb_data <= 32'd0;

endcase

endmodule

gbit_top模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : gbit_top.v

// Create Time : 2020-03-17 09:43:00

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module gbit_top(

//System Interfaces

input clk_50m ,

input clk_125m ,

input rst_n ,

//Gigbit Interfaces

output reg phy_rst_n ,

input [ 3:0] rx_data ,

input rx_ctrl ,

input rx_clk ,

//Communication Interfaces

output wire [ 7:0] image_data ,

output wire image_data_en ,

output wire [31:0] rlst ,

output wire rlst_flag

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [20:0] phy_rst_cnt ;

wire rx_clk_90 ;

//iddr_ctrl_inst

wire [ 7:0] gb_rx_data ;

wire gb_rx_data_en ;

wire gb_rx_data_err ;

//run_clk_ctrl_inst

wire [ 7:0] dout_o ;

wire dout_en ;

wire [12:0] latch_max ;

//image_ctrl_inst

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

always @(posedge clk_50m or negedge rst_n)

if(rst_n == 1'b0)

phy_rst_cnt <= 21'd0;

else if(phy_rst_cnt[20] == 1'b0)

phy_rst_cnt <= phy_rst_cnt + 1'b1;

else

phy_rst_cnt <= phy_rst_cnt;

always @(posedge clk_50m or negedge rst_n)

if(rst_n == 1'b0)

phy_rst_n <= 1'b0;

else if(phy_rst_cnt[20] == 1'b1)

phy_rst_n <= 1'b1;

else

phy_rst_n <= phy_rst_n;

clk_wiz_1 clk_wiz_1_inst(

// Clock out ports

.clk_out1 (rx_clk_90 ), // output clk_out1

// Clock in ports

.clk_in1 (rx_clk )

);

//clk_wiz_1 clk_wiz_1_inst(

// // Clock out ports

// .clk_out1 (clk_50m ), // output clk_out1

// .clk_out2 (clk_125m ), // output clk_out2

// // Status and control signals

// .reset (~rst_n ), // input reset

// .locked (locked ), // output locked

// // Clock in ports

// .clk_in1 (sclk )

//);

iddr_ctrl iddr_ctrl_inst(

//System Interfaces

.rst_n (rst_n ),

//Gigabit Interfaces

.rx_data (rx_data ),

.rx_ctrl (rx_ctrl ),

.rx_clk (rx_clk_90 ),

//Communication Interfaces

.gb_rx_data (gb_rx_data ),

.gb_rx_data_en (gb_rx_data_en ),

.gb_rx_data_err (gb_rx_data_err )

);

run_clk_ctrl run_clk_ctrl_inst(

//System Interfaces

.sclk (clk_125m ),

.rst_n (rst_n ),

//Gigbit Interfaces

.rx_data (gb_rx_data ),

.rx_en (gb_rx_data_en ),

.rx_clk (rx_clk_90 ),

//Communication Interfaces

.latch_max (latch_max ),

.dout_o (dout_o ),

.dout_en (dout_en )

);

image_ctrl image_ctrl_inst(

//System Interfaces

.sclk (clk_125m ),

.rst_n (rst_n ),

//Gigbit Interfaces

.dout_o (dout_o ),

.dout_en (dout_en ),

//Communication Interfaces

.latch_max (latch_max ),

.image_data (image_data ),

.image_data_en (image_data_en ),

.rlst (rlst ),

.rlst_flag (rlst_flag )

);

//========================================================================================\

//******************************* Debug **********************************

//========================================================================================/

ila_2 ila_2_inst (

.clk (clk_125m ), // input wire clk

.probe0 (gb_rx_data ), // input wire [7:0] probe0

.probe1 (gb_rx_data_en ), // input wire [0:0] probe1

.probe2 (gb_rx_data_err ), // input wire [0:0] probe2

.probe3 (image_data ), // input wire [7:0] probe3

.probe4 (image_data_en ), // input wire [0:0] probe4

.probe5 (rlst ), // input wire [31:0] probe5

.probe6 (rlst_flag ) // input wire [0:0] probe6

);

endmodule

iddr_ctrl模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : iddr_ctrl.v

// Create Time : 2020-03-17 09:21:20

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module iddr_ctrl(

//System Interfaces

input rst_n ,

//Gigabit Interfaces

input [ 3:0] rx_data ,

input rx_ctrl ,

input rx_clk ,

//Communication Interfaces

output reg [ 7:0] gb_rx_data ,

output reg gb_rx_data_en ,

output reg gb_rx_data_err

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

wire [ 7:0] data ;

wire data_en ;

wire data_err ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

IDDR #(

.DDR_CLK_EDGE ("OPPOSITE_EDGE" ), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1 (1'b0 ), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2 (1'b0 ), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE ("SYNC" ) // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_ctrl (

.Q1 (data_en ), // 1-bit output for positive edge of clock

.Q2 (data_err ), // 1-bit output for negative edge of clock

.C (rx_clk ), // 1-bit clock input

.CE (1'b1 ), // 1-bit clock enable input

.D (rx_ctrl ), // 1-bit DDR data input

.R (~rst_n ), // 1-bit reset

.S (1'b0 ) // 1-bit set

);

genvar i;

generate

for (i = 0; i < 4; i = i+1) begin

IDDR #(

.DDR_CLK_EDGE ("OPPOSITE_EDGE" ), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1 (1'b0 ), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2 (1'b0 ), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE ("SYNC" ) // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_ctrl (

.Q1 (data[i] ), // 1-bit output for positive edge of clock

.Q2 (data[4+i] ), // 1-bit output for negative edge of clock

.C (rx_clk ), // 1-bit clock input

.CE (1'b1 ), // 1-bit clock enable input

.D (rx_data[i] ), // 1-bit DDR data input

.R (~rst_n ), // 1-bit reset

.S (1'b0 ) // 1-bit set

);

end

endgenerate

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

gb_rx_data <= 8'd0;

else

gb_rx_data <= data;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

gb_rx_data_err <= 1'b0;

else

gb_rx_data_err <= data_err;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

gb_rx_data_en <= 1'b0;

else

gb_rx_data_en <= data_en;

endmodule

run_clk_ctrl模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : run_clk_ctrl.v

// Create Time : 2020-03-17 21:57:11

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module run_clk_ctrl(

//System Interfaces

input sclk ,

input rst_n ,

//Gigbit Interfaces

input [ 7:0] rx_data ,

input rx_en ,

input rx_clk ,

//Communication Interfaces

output reg [12:0] latch_max ,

output wire [ 7:0] dout_o ,

output reg dout_en

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [ 2:0] cnt_55 ;

reg mac_en ;

reg mac_en_dly ;

reg [ 7:0] rx_data_dly ;

reg [12:0] rx_cnt ;

reg latch_flag ;

wire rx_clr_flag ;

reg mac_en_r1 ;

reg mac_en_r2 ;

reg mac_en_r3 ;

reg mac_en_r4 ;

reg mac_en_r5 ;

reg mac_en_r6 ;

reg mac_en_r7 ;

reg rd_start ;

reg rd_en ;

reg [12:0] rd_cnt ;

wire full ;

wire empty ;

wire [ 9:0] rd_data_count ;

wire [ 9:0] wr_data_count ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

assign rx_clr_flag = mac_en && ~mac_en_dly;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

cnt_55 <= 3'd0;

else if(mac_en == 1'b0 && rx_data == 8'h55 && rx_en == 1'b1)

cnt_55 <= cnt_55 + 1'b1;

else if(mac_en == 1'b0 && rx_data == 8'hd5 && rx_en == 1'b1)

cnt_55 <= 3'd0;

else

cnt_55 <= 3'd0;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

mac_en <= 1'b0;

else if(cnt_55 == 3'd7 && rx_data == 8'hd5 && rx_en == 1'b1)

mac_en <= 1'b1;

else if(rx_en == 1'b0)

mac_en <= 1'b0;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

mac_en_dly <= 1'b0;

else if(rx_en == 1'b0)

mac_en_dly <= 1'b0;

else if(mac_en == 1'b1)

mac_en_dly <= 1'b1;

else

mac_en_dly <= mac_en_dly;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

rx_data_dly <= 8'd0;

else

rx_data_dly <= rx_data;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

rx_cnt <= 13'd0;

else if(rx_clr_flag == 1'b1)

rx_cnt <= 13'd0;

else if(mac_en_dly == 1'b1)

rx_cnt <= rx_cnt + 1'b1;

else

rx_cnt <= 13'd0;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

latch_flag <= 1'b0;

else if(mac_en_dly == 1'b1 && rx_en == 1'b0)

latch_flag <= 1'b1;

else

latch_flag <= 1'b0;

always @(posedge rx_clk or negedge rst_n)

if(rst_n == 1'b0)

latch_max <= 13'h1fff;

else if(rx_clr_flag == 1'b1)

latch_max <= 13'h1fff;

else if(latch_flag == 1'b1)

latch_max <= rx_cnt - 1'b1;

else

latch_max <= latch_max;

always @(posedge sclk)begin

mac_en_r1 <= mac_en_dly;

mac_en_r2 <= mac_en_r1;

mac_en_r3 <= mac_en_r2;

mac_en_r4 <= mac_en_r3;

mac_en_r5 <= mac_en_r4;

mac_en_r6 <= mac_en_r5;

mac_en_r7 <= mac_en_r6;

end

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

rd_start <= 1'b0;

else if(mac_en_r7 == 1'b0 && mac_en_r6 == 1'b1)

rd_start <= 1'b1;

else

rd_start <= 1'b0;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

rd_en <= 1'b0;

else if(rd_start == 1'b1)

rd_en <= 1'b1;

else if(mac_en_r5 == 1'b0 && rd_cnt == latch_max)

rd_en <= 1'b0;

else

rd_en <= rd_en;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

rd_cnt <= 13'd0;

else if(mac_en_r5 == 1'b0 && rd_cnt == latch_max)

rd_cnt <= 13'd0;

else if(rd_en == 1'b1)

rd_cnt <= rd_cnt + 1'b1;

else

rd_cnt <= rd_cnt;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

dout_en <= 1'b0;

else

dout_en <= rd_en;

fifo_generator_3 fifo_generator_3_inst(

.rst (1'b0 ), // input wire rst

.wr_clk (rx_clk ), // input wire wr_clk

.rd_clk (sclk ), // input wire rd_clk

.din (rx_data_dly ), // input wire [7 : 0] din

.wr_en (mac_en_dly ), // input wire wr_en

.rd_en (rd_en ), // input wire rd_en

.dout (dout_o ), // output wire [7 : 0] dout

.full (full ), // output wire full

.empty (empty ), // output wire empty

.rd_data_count (rd_data_count ), // output wire [9 : 0] rd_data_count

.wr_data_count (wr_data_count ) // output wire [9 : 0] wr_data_count

);

//========================================================================================\

//******************************* Debug **********************************

//========================================================================================/

endmodule

image_ctrl模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : image_ctrl.v

// Create Time : 2020-03-18 10:51:41

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module image_ctrl(

//System Interfaces

input sclk ,

input rst_n ,

//Gigbit Interfaces

input [ 7:0] dout_o ,

input dout_en ,

//Communication Interfaces

input [12:0] latch_max ,

output reg [ 7:0] image_data ,

output reg image_data_en ,

output wire [31:0] rlst ,

output reg rlst_flag

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [12:0] rd_cnt ;

reg [ 2:0] cnt_aa ;

reg width_en ;

reg height_en ;

reg height_en_r ;

reg [15:0] width_data ;

reg [15:0] height_data ;

reg start_image_en ;

reg image_en ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

rd_cnt <= 13'd0;

else if(dout_en == 1'b1 && rd_cnt == latch_max)

rd_cnt <= 13'd0;

else if(dout_en == 1'b1)

rd_cnt <= rd_cnt + 1'b1;

else

rd_cnt <= rd_cnt;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

cnt_aa <= 3'd0;

else if(rd_cnt == 'd49 && (dout_o == 8'hfa || dout_o == 8'hf5 || dout_o == 8'hf6))

cnt_aa <= 3'd0;

else if(rd_cnt >= 'd42 && rd_cnt <= 'd48 && dout_o == 8'haa)

cnt_aa <= cnt_aa + 1'b1;

else

cnt_aa <= 3'd0;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

width_en <= 1'b0;

else if(rd_cnt == 'd49 && dout_o == 8'hfa)

width_en <= 1'b1;

else if(rd_cnt == 'd51)

width_en <= 1'b0;

else

width_en <= width_en;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

height_en <= 1'b0;

else if(rd_cnt == 'd51 && width_en == 1'b1)

height_en <= 1'b1;

else if(rd_cnt == 'd53)

height_en <= 1'b0;

else

height_en <= height_en;

always @(posedge sclk)

height_en_r <= height_en;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

width_data <= 16'd0;

else if(width_en == 1'b1)

width_data <= {width_data[7:0],dout_o};

else

width_data <= width_data;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

height_data <= 16'd0;

else if(height_en == 1'b1)

height_data <= {height_data[7:0],dout_o};

else

height_data <= height_data;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

rlst_flag <= 1'b0;

else if(height_en_r == 1'b1 && rd_cnt == 'd54)

rlst_flag <= 1'b1;

else

rlst_flag <= 1'b0;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

start_image_en <= 1'b0;

else if(rd_cnt == 'd49 && (dout_o == 8'hf5 || dout_o == 8'hf6))

start_image_en <= 1'b1;

else if(rd_cnt == 'd51)

start_image_en <= 1'b0;

else

start_image_en <= start_image_en;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

image_en <= 1'b0;

else if(rd_cnt == 'd51 && start_image_en == 1'b1)

image_en <= 1'b1;

else if(rd_cnt == latch_max - 4)

image_en <= 1'b0;

else

image_en <= image_en;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

image_data <= 8'd0;

else if(image_en == 1'b1)

image_data <= dout_o;

else

image_data <= 8'd0;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

image_data_en <= 1'b0;

else

image_data_en <= image_en;

mult_gen_0 mult_gen_0_inst (

.CLK (sclk ), // input wire CLK

.A (width_data ), // input wire [7 : 0] A

.B (height_data ), // input wire [7 : 0] B

.P (rlst ) // output wire [15 : 0] P

);

//========================================================================================\

//******************************* Debug **********************************

//========================================================================================/

ila_1 ila_1_inst (

.clk (sclk ), // input wire clk

.probe0 (dout_o ), // input wire [7:0] probe0

.probe1 (dout_en ), // input wire [0:0] probe1

.probe2 (rd_cnt ), // input wire [12:0] probe2

.probe3 (cnt_aa ), // input wire [2:0] probe3

.probe4 (width_en ), // input wire [0:0] probe4

.probe5 (height_en ), // input wire [0:0] probe5

.probe6 (height_en_r ), // input wire [0:0] probe6

.probe7 (start_image_en ), // input wire [0:0] probe7

.probe8 (image_en ), // input wire [0:0] probe8

.probe9 (image_data ), // input wire [7:0] probe9

.probe10 (image_data_en ) // input wire [0:0] probe10

);

endmodule

conver_bit模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : conver_bit.v

// Create Time : 2020-03-18 17:39:59

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module conver_bit(

//System Interfaces

input sclk ,

input rst_n ,

//Gigbit Interfaces

input [ 7:0] image_data ,

input image_data_en ,

//Communication Interfaces

output wire [31:0] rgb_data ,

output reg rgb_data_en

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

reg [ 1:0] image_cnt ;

reg [23:0] data ;

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

assign rgb_data = {8'h00,data};

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

image_cnt <= 2'b0;

else if(image_cnt == 2'd2 && image_data_en == 1'b1)

image_cnt <= 2'd0;

else if(image_data_en == 1'b1)

image_cnt <= image_cnt + 1'b1;

else

image_cnt <= image_cnt;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

data <= 24'd0;

else if(image_data_en == 1'b1)

data <= {data[15:0],image_data};

else

data <= data;

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0)

rgb_data_en <= 1'b0;

else if(image_cnt == 2'd2 && image_data_en == 1'b1)

rgb_data_en <= 1'b1;

else

rgb_data_en <= 1'b0;

endmodule

image模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : image.v

// Create Time : 2020-05-12 09:40:55

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module image(

//System Interfaces

input sclk ,

input rst_n ,

//Communication Interfaces

input [31:0] rgb_data ,

input rgb_data_en ,

output wire [31:0] data_wr ,

output reg data_wr_en