微机原理与接口技术二 微处理器与总线

文章目录

- 微处理器

- 功能

- 运算器

- 控制器

- 8088/8086微处理器

- 区别

- 指令流水线

- ※8086的引脚

- 两种工作模式

- 地址线和数据线

- 8088和8086引线功能比较

- 内部结构

- 执行单元

- 总线接口单元

- 结论

- 内部寄存器

- BX和BP的区别

- 变址寄存器

- 状态标志位

- 控制标志位

- 时序

- 系统总线

- 定义

- 常用系统总线

- 主线的主要性能指标

- 8088工作模式

微处理器

功能

- 是计算机系统的核心

- 根据指令实现各种相应的运算

- 能对指令进行译码、寄存并执行指令规定的操作

- 实现数据的暂存

- 实现与存储器和接口的信息通信

- 能够提供系统所需的定时和控制信号

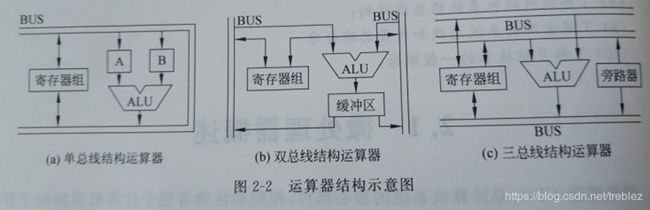

运算器

算术逻辑单元ALU(Arithmetic logic Unit)

又称运算器

以加法器为基础,辅以其它逻辑电路完成加、减、乘、除和各种逻辑运算;高级的ALU还可以完成浮点运算。

控制器

Ⅰ、指令寄存器IR(Instruction Register)

指令寄存器IR用来存放从存储器取出的将要执行的指令(实为其操作码)。

Ⅱ、指令译码器ID(Instruction Decoder)

指令译码器ID用来对指令寄存器IR中的指令进行译码,以确定该指令应执行什么操作。

Ⅲ、可编程逻辑阵列PLA(Programmable Logic Array)(也称为定时与控制电路)

功能:

指令控制

时序控制

操作控制

8088/8086微处理器

区别

8088与8086同属第三代CPU

8086 CPU 内●外D●B均为16位,是真正的16位机

8088 CPU 内部D●B为16位,外部D●B为8位,故为准16位机

它们已经用于各种智能控制系统。在最小配置下,只需4片外围芯片,便可构成一小型应用系统。

指令流水线

8088/8086 CPU内部有两个能立的部件:

总线接口单元BIU(Bus Interface Unit):

负责从内存取指送入指令流队列 从内存取操作数送至EU部份去执行

执行单元EU(Execution Unit):

负责指令的执行

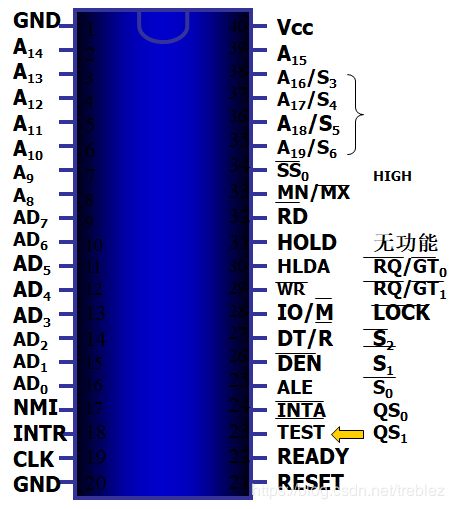

※8086的引脚

- S S 0 ‾ : 系 统 状 态 信 号 输 出 \overline{SS_{0}}:系统状态信号输出 SS0:系统状态信号输出

- M N / M X ‾ : 值 为 1 , 最 小 模 式 ; 值 为 0 , 最 大 模 式 MN/\overline{MX}:值为1,最小模式;值为0,最大模式 MN/MX:值为1,最小模式;值为0,最大模式

- W R ‾ 写 信 号 R D ‾ 读 信 号 ( 低 电 平 有 效 ) \overline{WR}写信号 \overline{RD}读信号(低电平有效) WR写信号RD读信号(低电平有效)

- DT/R:数据传送方向控制信号:值为1,CPU发送数据;值为0,CPU接受数据

- A16–A19:地址、段寄存器状态复用;S6=0, S5=IF,

S4S3=00,ES S4S3=01,SS S4S3=10,CS S4S3=11,DS - IO/M:=1,访问输入输出端口;

=0,访问存储器 - READY:输入信号,由内存或者I/O设备发出

- ALE:地址锁存允许信号,ALE=1

- INTR:可屏蔽中断请求输入信号

- NMI非屏蔽中断请求输入端

- I N T A ‾ : 中 断 响 应 输 入 端 \overline{INTA}:中断响应输入端 INTA:中断响应输入端

- ALE=1,地址信号;

DEN=0,数据信号; - RESET:复位信号

- HOLD:总线保持请求信号输入端。当CPU以外的其他设备要求占用总线时,通过该引脚向CPU发出请求。

- HLDA:总线保持响应信号输出端。CPU对HOLD信号的响应信号。

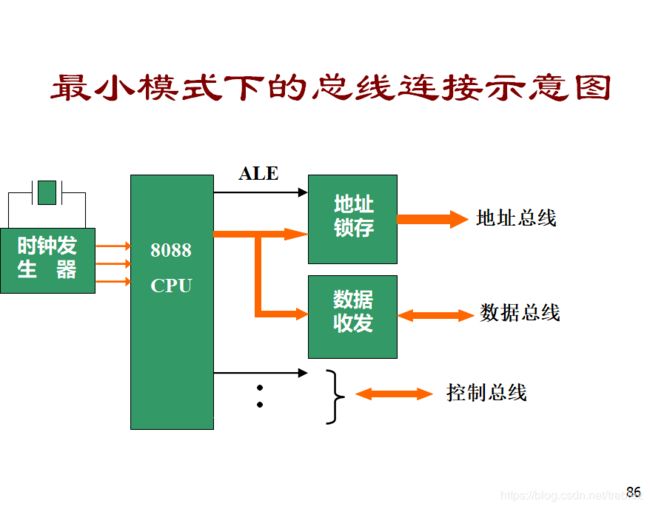

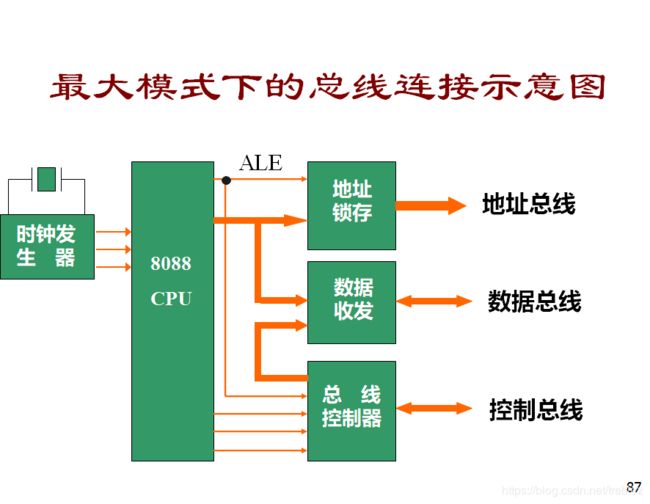

两种工作模式

最小模式为单处理器模式。

最大模式为多处理器模式。

地址线和数据线

AD0—AD7:低8位地址和低8位数据信号分时复用。在传送地址信号时为单向,传送数据信号时为双向。

A16–A19:高4位地址信号,与状态信号分时复用。

A8—A15 :8位地址信号

8088和8086引线功能比较

数据总线宽度不同

8088的外部总线宽度是8位,8086为16位。

访问存储器和输入输出控制信号含义不同

8088——IO/M=0表示访问内存;

8086——IO/M=1表示访问内存。

其他部分引线功能的区别

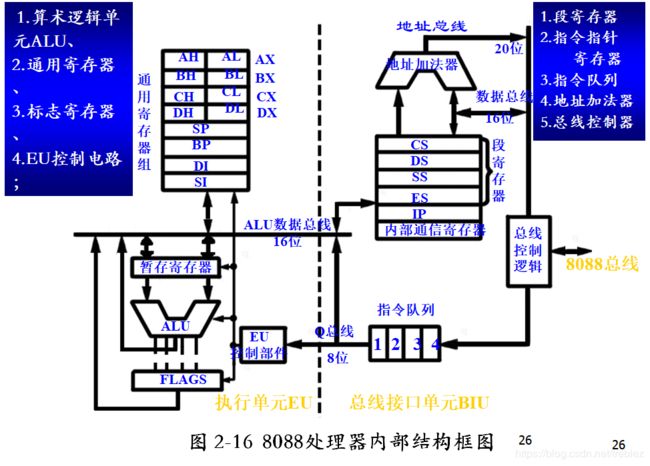

内部结构

执行单元

组成:

运算器

8个通用寄存器

EU部分控制电路

功能:

指令译码、指令执行、保存中间运算结果、保存运算结果特征

总线接口单元

功能:

从内存中取指令到指令预取队列

指令预取队列是并行流水线工作的基础

负责与内存或输入/输出接口之间的数据传送

在执行转移程序时,BIU使指令预取队列复位,从指定的新地址取指令,并立即传给执行单元执行

结论

指令预取队列的存在使EU和BIU两个部分可同时进行工作,从而:

提高了CPU的效率;

降低了对存储器存取速度的要求

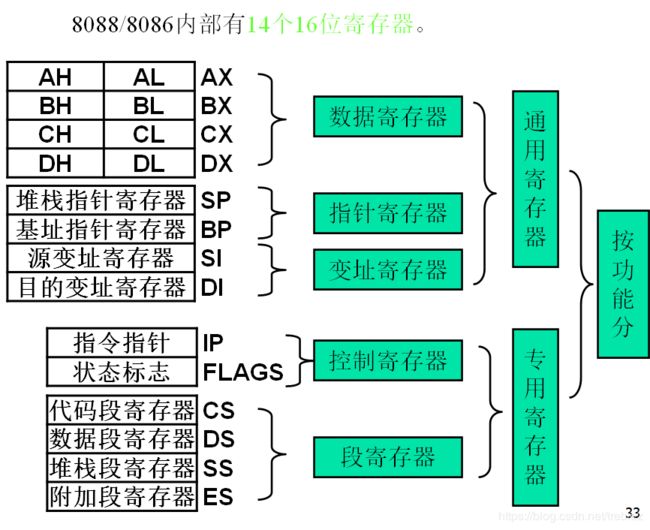

内部寄存器

含14个16位寄存器,按功能可分为三类:

8个通用寄存器

4个段寄存器

2个控制寄存器

习惯用法(?):

AX:累加器。所有I/O指令都通过AX与接口传送信息,中间运算结果也多放于AX中;

BX:基址寄存器。在间接寻址中用于存放基地址;

CX:计数寄存器。用于在循环或串操作指令中存放计数值;

DX:数据寄存器。在间接寻址的I/O指令中存放I/O端口地址;在32位乘除法运算时,存放高16位数。

SP:堆栈指针寄存器,其内容为栈顶的偏移地址;

BP:基址指针寄存器,常用于在访问内存时存放内存单元的基地址。

BX和BP的区别

作为通用寄存器,二者均可用于存放数据;

作为基址寄存器,用BX表示所寻找的数据在数据段;用BP则表示数据在堆栈段。

变址寄存器

SI:源变址寄存器

DI:目标变址寄存器

变址寄存器在指令中常用于存放数据在内存中的地址。

状态标志位

CF(Carry Flag)

进位标志位。加(减)法运算时,若最高位有进(借)位则CF=1

PF(Parity Flag)

奇偶标志位。运算结果的低8位中“1”的个数为偶数时PF=l

AF(Auxiliary Carry Flag)

辅助进位标志位。加(减)操作中,若Bit3向Bit4有进位(借位),AF=1

ZF(Zero Flag)

零标志位。当运算结果为零时ZF=1

SF(Sign Flag)

符号标志位。当运算结果的最高位为1时,SF=l

OF(Overflow Flag)

溢出标志位。当算术运算的结果超出了有符号数的可表达范围时,OF=l

控制标志位

TF(Trap Flag)

陷井标志位,也叫跟踪标志位。TF=1时,使CPU处于单步执行指令的工作方式。

IF(Interrupt Enable Flag)

中断允许标志位。IF=1使CPU可以响应可屏蔽断请求。

DF(Direction Flag)

方向标志位。在数据串操作时确定操作的方向

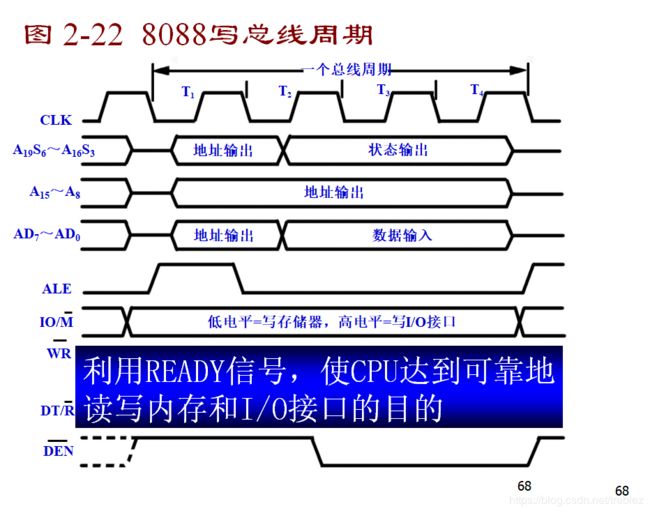

时序

时序的概念:CPU各引脚信号在时间上的关系。

时钟周期:每个时钟脉冲的持续时间成为一个时钟周期,用Ti表示,由时钟发生器产生,是CPU工作的基本时间单位。PC/XT时钟频率4.77MHz,时钟周期是210ns。

总线周期:CPU完成一次访问内存(或接口)操作所需要的时间。8088执行存储器读或存储器写操作需用4个时钟周期。 8088的总线周期由4个时钟周期组成,称为T1、T2、T3、T4状态;

指令周期P:由若干个总线周期组成。是从取指令开始到指令执行完毕所需要的时间。

系统总线

定义

是一组导线和相关的控制、驱动电路的集合。是计算机系统各部件之间传输地址、数据和控制信息的通道。

常用系统总线

ISA(8/16位)

PCI(32/64位)

AGP(加速图形端口,用于提高图形处理能力)

PCI-E(PCI Express )

目前最新的系统总线标准,采用串行方式传输数据,依靠高频率来获得高性能。

主线的主要性能指标

总线带宽(B/S):单位时间上总线可以传送的数据量

总线位宽(bit):能同时传送的数据位数

总线的工作频率:(MHz)

总线带宽=(位宽/8)*(工作频率/每个存取周期的时钟数)

8088工作模式

8088可工作于两种模式下:

最小模式为单处理器模式,控制信号较少,一般可不必接总线控制器。

最大模式为多处理器模式,控制信号较多,须通过总线控制器与总线相连。