zsim-memtrace-nvmain安装记录

zsim_trace

按照README 把 XED 和 DynamoRIO build and set path

XED build and set path

git clone https://github.com/intelxed/xed.git xed

git clone https://github.com/intelxed/mbuild.git mbuild

cd xed

./mfile.py

export XEDPATH=/home/taya/zsim_nvmain_memtrace/xed

export LD_LIBRARY_PATH=$XEDPATH/kits/xed-install-base-2017-12-18-lin-x86-64/lib/

DynamoRIO build and set path

git clone https://github.com/DynamoRIO/dynamorio

cd dynamorio

mkdir build

cmake ..

make -j4

export DRIOPATH=/home/taya/zsim_nvmain_memtrace/dynamori

解决错误

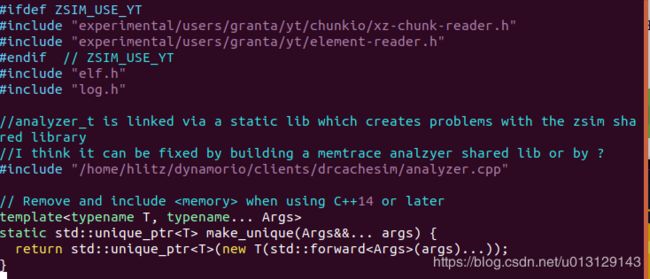

修改trace_reader.cpp的里 include的路径

不懂为什么这部分要include cpp

不懂为什么这部分要include cpp

//analyzer_t is linked via a static lib which creates problems with the zsim shared library

//I think it can be fixed by building a memtrace analzyer shared lib or by ?

#include "/home/hlitz/dynamorio/clients/drcachesim/analyzer.cpp"

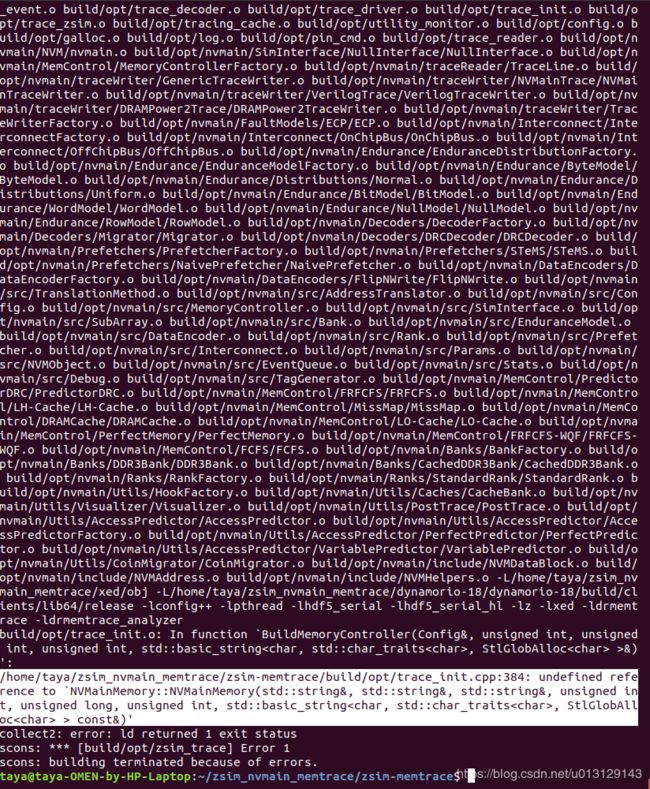

修改之后再次编译 还是报错

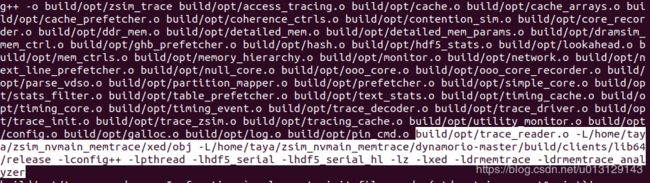

都是undefine referrnce 。我估计应该是链接库的问题,可能dynamorio路径没设置正确,可是检查输出的文字

都是undefine referrnce 。我估计应该是链接库的问题,可能dynamorio路径没设置正确,可是检查输出的文字

高亮的部分,到该路径检查有没有相对应的库

高亮的部分,到该路径检查有没有相对应的库

这个路径是有这些链接库的,所以应该不是路径的问题。

这个路径是有这些链接库的,所以应该不是路径的问题。

于是到GITHUB上请教下发布者,他说可能是memtrace(dynamorio)API 改了, 然后我尝试,下载旧版本的 dynamori ,分别下载了16年的和15年的,发现15年的 并没有dynamorio/clients/drcachesim/analyzer.cpp,所以使用16年的

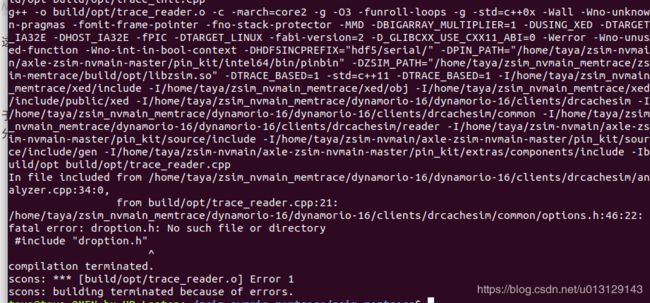

还是报错,对比两个版本的dynamorio 的common文件夹下的内容,发现16的少了不少东西

还是报错,对比两个版本的dynamorio 的common文件夹下的内容,发现16的少了不少东西

尝试17版本的dynamorio 也不行,

尝试17版本的dynamorio 也不行,

最后不断尝试 这个18年的版本的可以

接下来需要通过阅读代码找出Trace file 的格式

用GDB 断点调试,发现主程序是trace_zsim.cpp,但是因为是多线程的原因,最后GDB只能追踪到

pthread_create()这个函数

pthread_create()

https://www.cnblogs.com/amanlikethis/p/5537175.html

pthread_create(&simthread[i], NULL, simtrace, &ti[i]);

弄懂这个函数,知道他会创建线程 以ti[i]为参数条用simtrace

trace 的格式

#memtrace trace:

trace0 ="/mnt/sda/traces/XSBench.memtrace";

#modules.txt file:

trace_binaries = "/mnt/sda/traces/drmemtrace.XSBench.12086.8971.dir/";

不知道trace0 是怎么产生的

第二个为猜测是 dynamorio 产生的

dynamorio 一些工具的使用 http://dynamorio.org/docs/page_deploy.html

柳暗花明阿 在 http://dynamorio.org/docs/page_drcachesim.html#sec_drcachesim_offline 找到答案

$ bin64/drrun -t drcachesim -offline -- ls

产生一个trace_binaries所需的文件夹

$ bin64/drrun -t drcachesim -indir drmemtrace.app.pid.xxxx.dir/

用产生的 模拟跑一遍,之后会在文件夹产生trace0 所需的文件(需要解压)

成功的运行

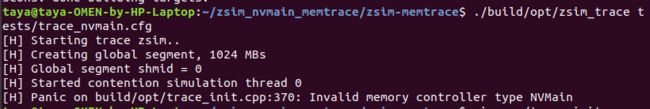

taya@taya-OMEN-by-HP-Laptop:~/zsim_nvmain_memtrace/zsim-memtrace$ ./build/opt/zsim_trace tests/trace.cfg

[H] Starting trace zsim..

[H] Creating global segment, 1024 MBs

[H] Global segment shmid = 0

[H] Started contention simulation thread 0

[H] mem-0: domain 0, 4 ranks/ch 8 banks/rank, tech DDR3-1066-CL8, boundLat 64 rd / 10 wr

[H] mem-0: Address mapping rank:col:bank row 63:15 col 12:3 rank 14:13 bank 2:0

[H] mem-1: domain 0, 4 ranks/ch 8 banks/rank, tech DDR3-1066-CL8, boundLat 64 rd / 10 wr

[H] mem-1: Address mapping rank:col:bank row 63:15 col 12:3 rank 14:13 bank 2:0

[H] mem-2: domain 0, 4 ranks/ch 8 banks/rank, tech DDR3-1066-CL8, boundLat 64 rd / 10 wr

[H] mem-2: Address mapping rank:col:bank row 63:15 col 12:3 rank 14:13 bank 2:0

[H] mem-3: domain 0, 4 ranks/ch 8 banks/rank, tech DDR3-1066-CL8, boundLat 64 rd / 10 wr

[H] mem-3: Address mapping rank:col:bank row 63:15 col 12:3 rank 14:13 bank 2:0

[H] Hierarchy: [ l1i_beefy-0 l1d_beefy-0 ] -> l2_beefy-0

[H] Hierarchy: [ l1i_beefy-1 l1d_beefy-1 ] -> l2_beefy-1

[H] Hierarchy: [ l1i_beefy-2 l1d_beefy-2 ] -> l2_beefy-2

[H] Hierarchy: [ l1i_beefy-3 l1d_beefy-3 ] -> l2_beefy-3

[H] Hierarchy: [ l1i_beefy-4 l1d_beefy-4 ] -> l2_beefy-4

[H] Hierarchy: [ l1i_beefy-5 l1d_beefy-5 ] -> l2_beefy-5

[H] Hierarchy: [ l2_beefy-0 l2_beefy-1 l2_beefy-2 l2_beefy-3 l2_beefy-4 l2_beefy-5 ] -> l3-0b0..l3-0b5

[H] Initialized system

[H] HDF5 backend: Opening .//zsim.h5

[H] HDF5 backend: Created table, 8520 bytes/record, 124 records/write

[H] HDF5 backend: Opening .//zsim-ev.h5

[H] HDF5 backend: Created table, 8520 bytes/record, 16 records/write

[H] HDF5 backend: Opening .//zsim-cmp.h5

[H] HDF5 backend: Created table, 2176 bytes/record, 1 records/write

[H] Initialization complete

/home/taya/zsim_nvmain_memtrace/dynamorio-master/build/clients/lib64/release/libdrmemtrace.so 0 7f79b7282000

/home/taya/zsim_nvmain_memtrace/dynamorio-master/build/clients/lib64/release/libdrmemtrace.so 265c8 7f79b74a8000

/bin/ls 0 7f7a37060000

/bin/ls 1eff0 7f7a3727e000

/lib/x86_64-linux-gnu/ld-2.27.so 0 7f7a3b058000

/lib/x86_64-linux-gnu/ld-2.27.so 27680 7f7a3b27f000

/home/taya/zsim_nvmain_memtrace/dynamorio-master/build/lib64/release/libdynamorio.so 0 7f7a3b283000

/home/taya/zsim_nvmain_memtrace/dynamorio-master/build/lib64/release/libdynamorio.so 15a180 7f7a3b5dd000

/lib/x86_64-linux-gnu/libc-2.27.so 0 7f7a39ab9000

/lib/x86_64-linux-gnu/libc-2.27.so 1e7620 7f7a39ea0000

/lib/x86_64-linux-gnu/libpthread-2.27.so 0 7f7a39424000

/lib/x86_64-linux-gnu/libpthread-2.27.so 19ba0 7f7a3963d000

/lib/x86_64-linux-gnu/libdl-2.27.so 0 7f7a39643000

/lib/x86_64-linux-gnu/libdl-2.27.so 2d70 7f7a39845000

/lib/x86_64-linux-gnu/libpcre.so.3.13.3 0 7f7a39847000

/lib/x86_64-linux-gnu/libpcre.so.3.13.3 70bd0 7f7a39ab7000

/lib/x86_64-linux-gnu/libselinux.so.1 0 7f7a39eaa000

/lib/x86_64-linux-gnu/libselinux.so.1 24cb8 7f7a3a0ce000

[H] Tid: 0 finished. Instruction trace size: 623212. Skipped instructions due to unavailable symbols: 0. BBLs in trace: 133818, dropped BBLs due to context switches: 0

Intergrate NVmain

-

尝试直接把

src/nvmain_mem_ctrl.*复制,再根据AX的SConstruct修改zsim-memtrace的SConstruct

用diff src/trace_init.cpp src/init.cpp 发现在初始化一些模拟硬件的时候,并没有不同。 可以直接复制AX的init.cpp关于创建NVM的部分

用diff src/trace_init.cpp src/init.cpp 发现在初始化一些模拟硬件的时候,并没有不同。 可以直接复制AX的init.cpp关于创建NVM的部分

再编译,出现下面的链接问题,估计是SConsript的问题了

接着修改

编译发现还是出错了,看来不仅仅是修改trace_init,cpp 和加入 nvm_mem_ctr.*就好了,查了下源码,发现zsim.*也要修改

修改 zsim.h siminfo结构体 修改zsim.cpp simEnd()函数

修改 zsim.h siminfo结构体 修改zsim.cpp simEnd()函数

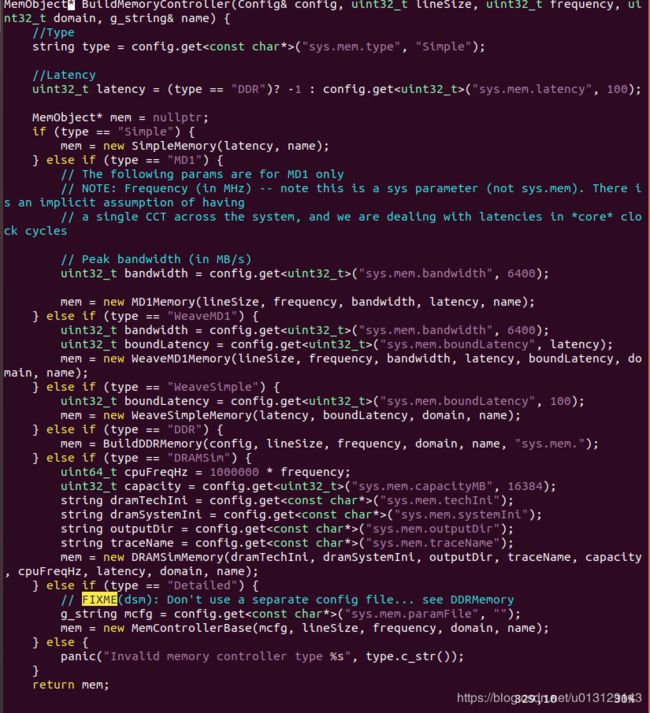

修改trace_init.cpp BuildmemoryCTl()那个函数,,InitSystem(Config& config) ()函数

修改stat.h 的VectorCounter

整合之后编译成功,,,,运行也成功。。但是没有产生mem-0-nvmain.out文件。。估计是那里出了问题,没有真正的整合成功,导致NVMain运行出错。。。需要找到那里调用了NVMAIN,估计是nvm_memory_ctr.cpp