(2009)

15.某计算机主存容量为 64KB,其中 ROM 区为 4KB,其余为 RAM 区,按字节编址。现用 2K×8 位的 ROM 芯片和 4K×4 位的 RAM 芯片来设计该存储器,则需要上述规格的 ROM芯片数和 RAM 芯片数分别是

A.1、15 B.2、15

C.1、30 D.2、30

答案:D

考点:存储器芯片的组成

首先确定ROM的个数,ROM区为4KB,选用2K×8位的ROM芯片,需要![]() 片,采用字扩展方式;RAM区为60KB,选用4K×4位的RAM芯片,需要

片,采用字扩展方式;RAM区为60KB,选用4K×4位的RAM芯片,需要![]() 片,采用字和位同时扩展方式。

片,采用字和位同时扩展方式。

(2010)

15.假定用若干个2K x 4位芯片组成一个8K x 8为存储器,则0B1FH所在芯片的最小地址是( )

A.0000H B.0600H

C.0700H D.0800H

答案:D

考点:主存储器扩展的地址分配

2K x 4位芯片组成一个8K x 8为存储器,需要2K x 4的芯片8片。如果按字节编址,对应一个大小为8K×8位的存储器,需要13位地址,其中高2位(先进行位扩展,再进行字扩展,所以两个芯片位扩展后变为8位,这样的8位芯片组需要4组)为片选地址,低11位为片内地址,而题目给出的地址0B1FH转换为二进制为0 1011 0001 1111,其高3位为010,即片选地址为2。因此,地址0B1FH对应第2片芯片,该芯片的起始地址(最小地址)为

0 1000 0000 0000,即0800H。

第一组的起始地址:

000 00 0000 0000 001 11 1111 1111

第二组的起始地址: 010 00 0000 0000 011 11 1111 1111

第三组的起始地址 100 00 0000 0000 101 11 1111 1111

第四组的起始地址 110 00 0000 0000 111 11 1111 1111

16.下列有关RAM和ROM得叙述中正确的是( )

I RAM是易失性存储器,ROM是非易失性存储器

II RAM和ROM都是采用随机存取方式进行信息访问

III RAM和ROM都可用做Cache

IV RAM和ROM都需要进行刷新

A. 仅I和II B. 仅II和III

C. 仅I ,II, III D. 仅II,III,IV

答案:A

考点: RAM和ROM的区别

RAM是易失性存储器,ROM是非易失性存储器,都是采用随机存取方式进行信息访问,SRAM可以用来做Cache,RAM需要刷新。

(2011)

14.下列各类存储器中,不采用随机存取方式的是

A.EPROM B.CDROM

C.DRAM D.SRAM

答案:B

考点:随机存取方式的定义,光盘采用顺序存储

15.某计算机存储器按字节编址,主存地址空间大小为64 MB,现用4M × 8位的RAM芯片组成32 MB的主存储器,则存储器地址寄存器MAR的位数至少是

A.22位 B.23位 C.25位 D.26位

答案:D

考点:主存地址空间和地址寄存器位数关系

64MB的主存地址空间,故而MAR的寻址范围是64M,故而是26位。而实际的主存的空间不能代表MAR的位数。

(2012)

16.下列关于闪存(Flash Memory)的叙述中,错误的是

A. 信息可读可写,并且读、写速度一样快

B. 存储元由 MOS 管组成,是一种半导体存储器

C. 掉电后信息不丢失,是一种非易失性存储器

D. 采用随机访问方式,可替代计算机外部存储器

答案:A

解析:闪存的写操作必须在空白区域进行,如果目标区域已经有数据,必须先擦除后写入,而读操作不必如此,所以闪存的读速度比写速度快。其他三项均为闪存的特征。

引申一个问题:通用微机是否可以采用Flash Memory作为主机?

不可以,闪存需要将整片或这个分区擦除后才能写入,而且擦除写入时间又长,不能作为一般微机的主存,但可以作为磁盘的补充设备

(2014)

15. 某容量为256M的存储器,由若干4M*8位的DRAM芯片构成,该DRAM芯片的地址引脚和数据引脚总数是:

A 19 B 22 C 30 D 36

答案:A

DRAM 芯片的地址线,在芯片中,是分时复用的,仅需一半的引脚数,即够用。

A.SRAM B.SDRAM

C.ROM D.FLASH

答案:B

A.8004和8008 B.8002和8007

C.8001和8008 D.8000 和8004

解析:交叉存储器,又称低位交叉编址。

本题中,主存地址模4后对应的体号分别是:1,2,3,4,1,2,3,4,4。地址为8004和8000都是存取的四号储存器,可能导致8004存储还未完成而又存取8000地址,因此可能发生缓存冲突。

A. 7 B. 8 C. 14 D. 16

解析: ROM地址空间4000H~5FFFH为8K,则RAM容量=64-8=56KB=56K*8,采用字和位同时扩展方式(56K*8)/(8K*4)=14

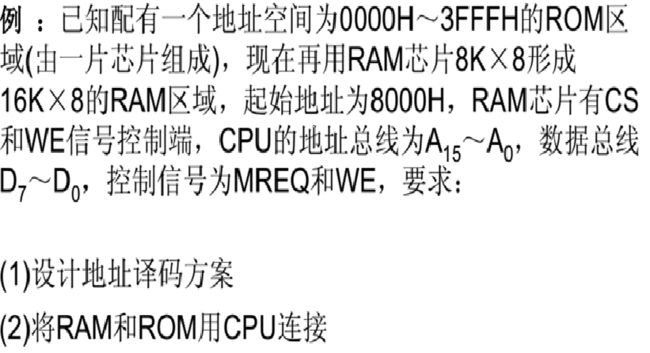

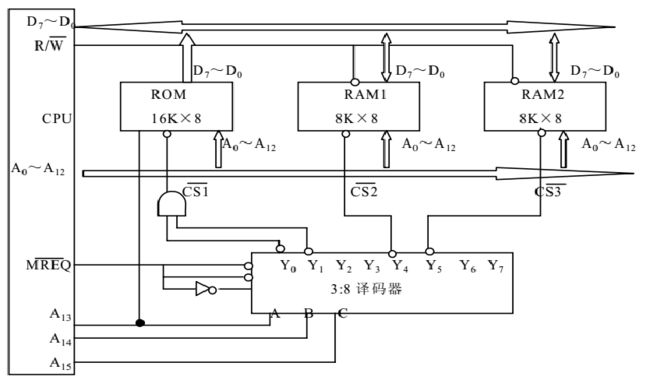

存储器设计

通过对ROM和RAM的地址分析,我们会发现一个问题,二者由于基本芯片的容量不同导致了需要的片选地址不同,该如何解决?下面给出两个方案。

方案一:

以内部地址少为主,地址译码方案:

Y0和Y1选ROM

Y4选RAM1,Y5选RAM2

方案二:

以内部地址多为主,地址译码方案:

用A15和A14作译码器输入

Y0选ROM;Y2选RAM1和RAM2

当A13=0时选RAM1,当A13=1时选RAM2