第二章里面已经说过了,MIZ701 PL部分没有输入时钟,因此驱动PL资源必须是通过PS来提供时钟,所以这个流水灯实验也得建立一个最小系统了,然后再添加一个流水灯的自定义IP。

3.0本章难度系数★★☆☆☆☆☆

3.1 硬件图片

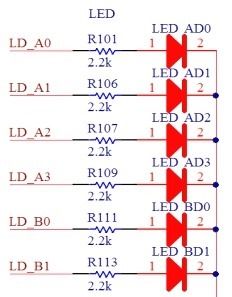

先来熟悉一下开发板的硬件:LED部分及按钮部分

![]()

3.2 硬件原理图

PIN脚定义:

| LD_A0:F17 LD_A1:J15 LD_A2:G14 LD_A3:D18 LD_B0:M14 LD_B1:M15 |

BIN0:R18 BIN1:T17 SW0:MIO50 SW1:MIO51 |

3.3VIVADO创建自定义图形IP

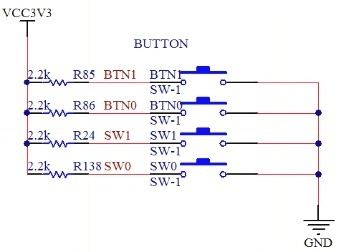

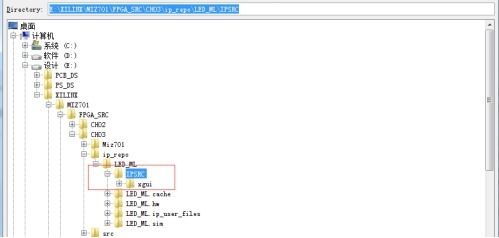

Step1:创建一个新的空的工程,这个前面已经讲过了,唯一要注意的是规范,笔者在创建之前就新建了ip_repo文件夹用于管理自定义IP,读者可以参考笔者的文件管理方式。

![]()

Step2:新建工程LED_ML 并且保存到ip_repo文件夹下,方便自定义管理,后面的过程参考第二章新建工程部分。

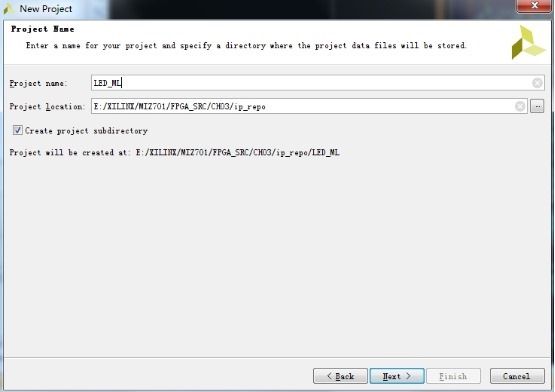

Step3:新建完成后,可以看到下面大红框的文件,然后在新建一个IPSRC的文件夹,并且把led_ml.v文件复制进去

| LED_ML.v源码 |

| // Target Devices: XC7Z020-FGG484 // Tool versions: VIVADO2015.4 // Description: water led // Revision: V1.1 // Additional Comments: //1) _i PIN input //2) _o PIN output //3) _n PIN active low //4) _dg debug signal //5) _r reg delay //6) _s state machine ////////////////////////////////////////////////////////////////////////////// module LED_ML( input CLK_i, input RSTn_i, output reg [3:0]LED_o ); reg [31:0]C0; always @(posedge CLK_i) if(!RSTn_i) begin LED_o <= 4'b0001; C0 <= 32'h0; end else begin if(C0 == 32'd50_000_000) begin C0 <= 32'h0; if(LED_o == 4'b1000) LED_o <= 4'b0001; else LED_o <= LED_o << 1; end else begin C0 <= C0 + 1'b1; LED_o <= LED_o; end end endmodule |

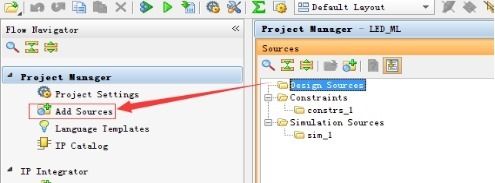

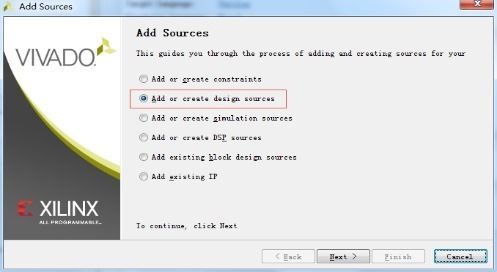

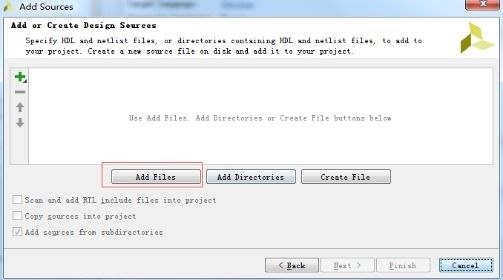

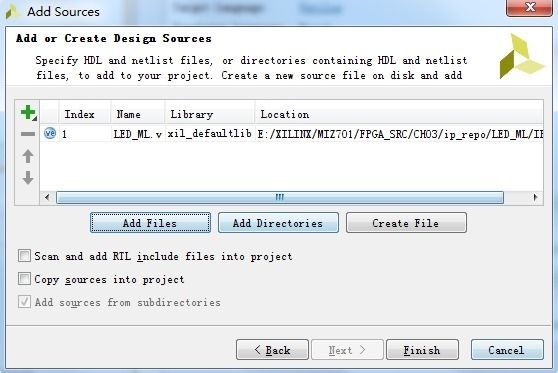

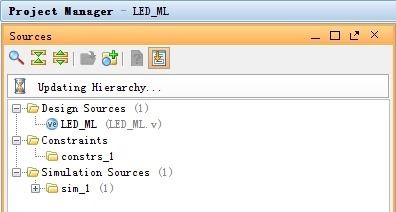

Step4:选择Add Sources添加LED_ML.v文件

Step5:添加完成后如图

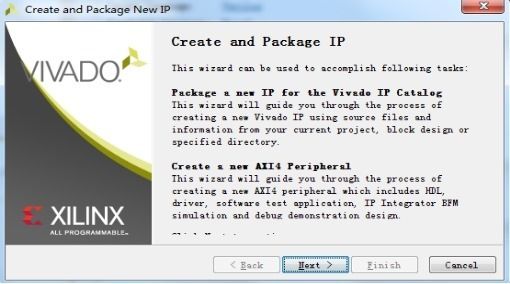

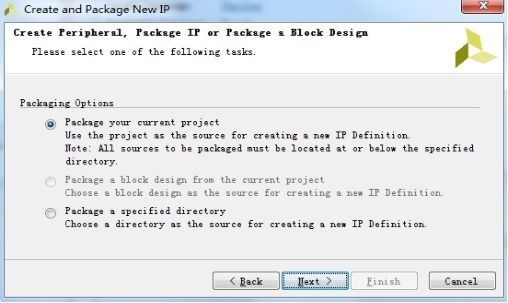

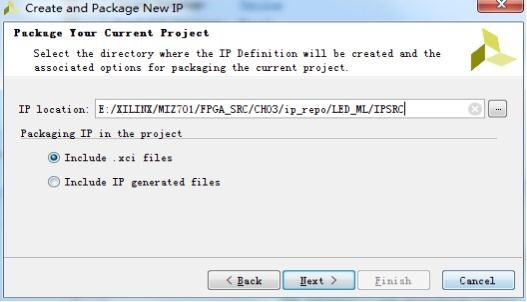

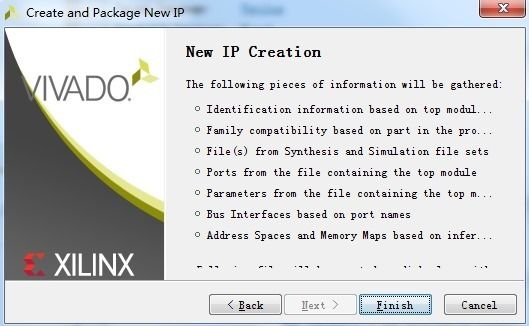

Step6:添加完成进行创建IP 选择Tools-> Create and Package IP

![]()

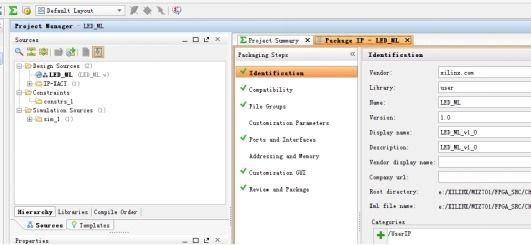

Step7:创建完成后如下图

3.4VIVADO添加自定义IP

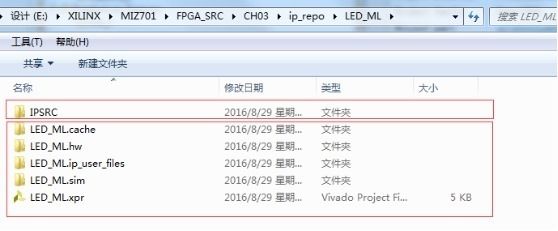

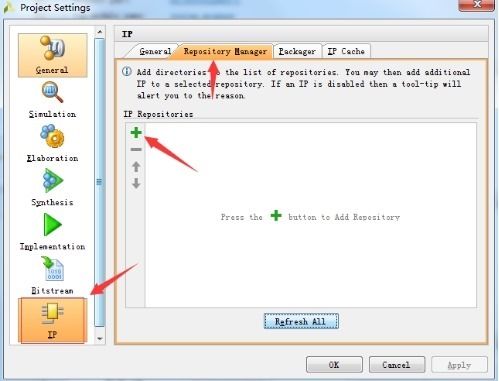

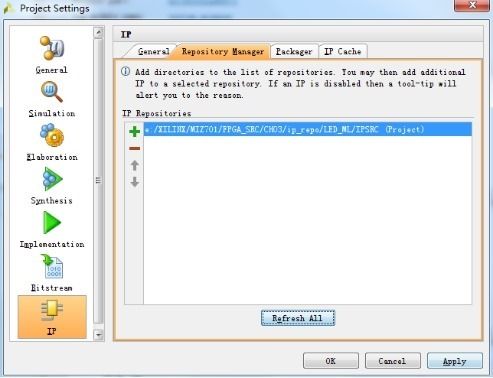

Step1:打开VIVADO工程,笔者这里直接复制上一章节的工程后打开工程文件,打开工程后,单机Project Setting

![]()

Step2:添加IP

Step2:添加完成后如下图,单击OK 完成

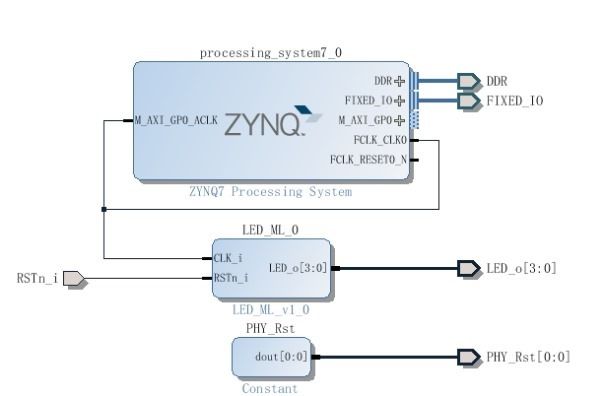

Step3:双击system工程,然后可以可拿到出来了添加IP的控件,选择添加IP

![]()

Step4:添加LED_ML IP

![]()

Step5:完成连线注意引出到外部的端口,只要把鼠标放到相应的端口上,右击

Make Exteral就可以了

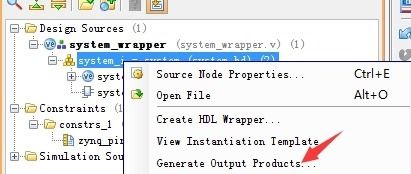

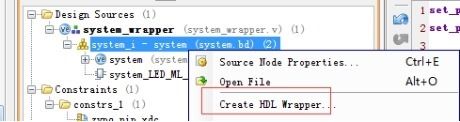

Step6:右击 system 选择Generate Output Products

Step7:右击 system 选择 Create HDL Wrapper

Step8:添加PIN 约束

| Zynq_pin.xdc |

| set_property PACKAGE_PIN E17 [get_ports PHY_Rst[0]] set_property IOSTANDARD LVCMOS33 [get_ports PHY_Rst[0]] set_property PACKAGE_PIN F17 [get_ports {LED_o[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[0]}] set_property PACKAGE_PIN J15 [get_ports {LED_o[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[1]}] set_property PACKAGE_PIN G14 [get_ports {LED_o[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[2]}] set_property PACKAGE_PIN D18 [get_ports {LED_o[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED_o[3]}] set_property PACKAGE_PIN R18 [get_ports {RSTn_i}] set_property IOSTANDARD LVCMOS33 [get_ports {RSTn_i}] |

3.5 编译并且产生bit文件

Step1:单击综合

Step2:单击执行

Step3:单击产生bit(可以直接最后一步)

3.6导出到SDK直接运行任何一个程序

导出到SDK后直接运行任何一个程序,FCLK_CLK0就会运行了

3.7实验结果

下载过程下载完成后LED流水灯就运行起来了。

3.8本章小结

本章详细讲解了VIVADO 下如何创建自定义的工程,并且通过IP连线快速完成工程设计。由于LED 是PL资源需要PL时钟才能工作,本章从PS部分的PLL引出的时钟输入给PL部分的LED程序。之后启动SDK,SDK C程序运行后,由于FCLK_CLK0就启动了,之后流水灯就跑起来了。

源码下载地址;链接:http://pan.baidu.com/s/1c2fuVPe 密码:s9ig