微电子电路——例题期末总结

本次主要是对经典题目的汇总,如果想看对知识点的汇总,可以看我另一篇博客:微电子电路——期末总结

一、绪论

1、第一个晶体管发明年份?:1947

2、发明者当时供职于哪家公司?:bell lab

3、第一块集成电路发明年份?:1958

4、发明者当时供职于哪家公司?:TI

5、第一台计算机诞生年份?:1946

6、发明者当时供职于哪家公司?:bell lab

7、第一个mos管诞生年份?:1960

8、cmos管诞生年份?:1963

二、基本元件

1、考虑标准0.13µm CMOS工艺下NMOS管,零衬偏时阈值电压VT=0.3V,栅氧厚度为tox=260nm,衬底掺杂浓度NA=2×1017cm-3,衬底接地。如果源极VS=0.3V时,室温下NMOS管阈值电压变化多少?

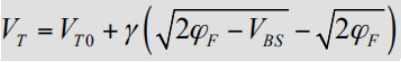

这道题主要考察阈值电压公式:

重点是我们需要根据他给出来的值来计算体效应系数

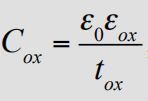

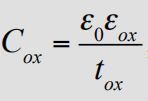

其中的ε是常量,q也是常量,而Na题目中已经给出,我们需要计算的仅仅是删氧化层的电容,根据公式:

综上可以计算出体效应系数,然后需要计算两个费米能级φ,费米能级的公式为:

其中的KT/q是常温下的热电压,ni是本证载流子的浓度,都是应该给出来的常量,代入计算即可。由于源极电压VS=0.3,那么源底电压=-0.3,带入最初的共识,便可以计算出最终的阈值电压

这道题很难,但要知道,在考试的时候,所有的公式,常量老师都会给出来的,重点是我们怎么用(~~希望吧)。

2、考虑标准0.13µm CMOS工艺下NMOS管,宽长比为W/L=0.26µm/0.13µm,栅氧厚度为tox=26Å,室温下电子迁移率µn=220cm2/V·s,阈值电压VT=0.3V,计算VGS=1.0V,VDS=0.2V和1.0V时ID的大小。

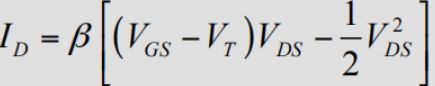

这道题我们要算的是漏源电流的大小,首先根据给出的VGS和VT可以知道VGS>VT,而当VDS=0.2的时候,VDS

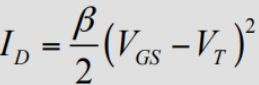

相应的,当VDS=1的时候,VDS>VDS-VT,说明此时处于饱和区,使用公式:

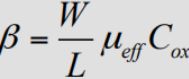

此时我们要计算的只不过是这个常数β,代入公式:

同样,W和L已经给出,μn也已经给出,只有Ctox删氧化层电容需要计算,代入公式:

至此,所有的参数已经计算完毕,就可以得到漏电流的值。

各位可以看到,标准0.13μm的nmos管经常出现,大家可以记一下他的ε的值或者Ctox删氧化层电容的值,是3.98.8510-14/tox,而tox的单位A是10-8

3、以N型半导体为例,他的多数载流子是自由电子,即自由电子浓度n>空穴浓度p,那么他是否保持电中性?为什么?

是保持电中性。

从微观上讲,不管是多子还是少子,都是在原子核之外而言的。就以题目中的N型半导体为例。由于N型半导体是掺杂了五族元素制作而成的,导致在晶格中存在较多的自由电子,构成了多数载流子。

从宏观上来看,本征半导体为电中性,掺杂也是电中性,故**所有电子(不管是不是自由电子)**的数目和原子核中质子的数目是相等的,所以对外不显电性。

4、在半导体中,哪些是带正电的?:电离施主、空穴

5、在半导体中,哪些是带负电的?:电离受主、自由电子

6、对一个半导体而言会有如下公式:

对于施主杂质,可以认为是电子数d=空穴数d+施主离子数。其中注意,这里的电子数并不等于n,而是仅仅由施主杂质产生的电子。

对于受主杂质,可以认为是空穴数a=电子数a+受主离子数。其中注意,这里的空穴数并不等于p,而是仅仅由受主杂质产生的空穴。

7、下图的 MOS 晶体管各是什么类型,标明每个 MOS 晶体管的栅、源、漏极,分析它们的工作状态,设所有晶体管的阀值电压的绝对值都是 1V。

(a)增强型nmos,左为栅极,上位漏极,下为源极,VT=1V,VG-VT>VDS。工作于线性区

(b)增强型nmos,左为源极,上位栅极,下为漏极,VT=1V,VDS>VG-VT。工作于饱和区

©耗尽型nmos,左为栅极,上位漏极,下为源极,VT=-1V,VDS>VG-VT。工作于饱和区

(d)增强型pmos,左为栅极,上位源极,下为漏极,VT=-1V,VDS>VG-VT。工作于线性区

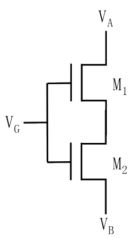

8、如图所示,M1 和 M2 两管串联,且 VB < VG-VT < VA,请问:

(1) 若都是 NMOS,它们各工作再什么状态?

(2) 若都是 PMOS,它们各工作在什么状态?

(3) 证明两管串联的等效导电因子是 Keff = K1K2/(K1 +K2)。

解:

(1)假定VC的值,根据VB

假设M1截止、M2饱和,则上nmos电流为0,下nmos电流大于0,VC被下拉,电路处于非稳态,所以VC会继续下降到VC

(3)假设都是nmos管,由于VB

ID2=K2[(VG-VT-VB)2-(VG-VT-VC)2]

IDeff=Keff(VG-VT-VB)^2

由此可以得到:

又因为ID1=ID2=IDeff

化简后可得Keff=K1K2/(K1 +K2)

三、反相器

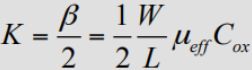

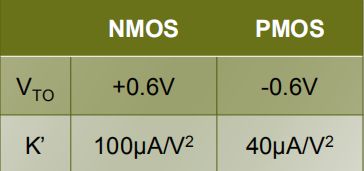

1、对于W/L=20/1的晶体管,其 KP和KN分别是多少?

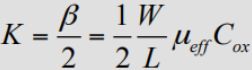

我们可以根据K值的公式:

题目中给出的K‘实际上就是除去了宽长比的K值,即K‘=1/2μCox

所以,这道题已经很简单了,直接代入公式就可以。

2、CMOS反相器中(W/L)P=(W/L)N时,KR为多少? 计算这个KR值时,CMOS反相器由逻辑阈值点确定的最大噪声容限为多少?(VDD=2.5V, VTN=0.6V, VTP=-0.6V)

这道题我们需要计算Kr=KN/KP,直接带入公式可以求出大概为2.5

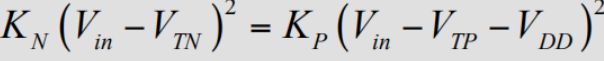

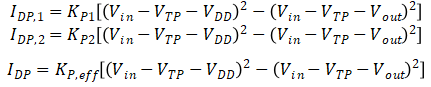

要计算最大噪声容限,我们需要计算出转换电平Vit的值,即公式:

此时我们已经有所有的值,那么直接算出转换电平的值,而最大噪声容限是VDD-Vit与Vit之间的小值,可以计算出

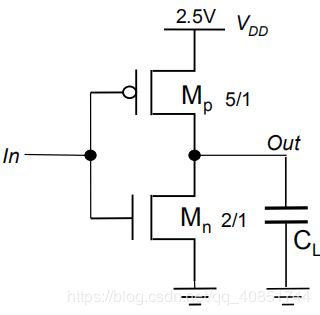

3、求图中反相器的最大电流?

想要计算最大电流说明是双饱和区的时候,即公式:

由于K‘都已经给出,且VT都给出了,宽长比在图中给出分别是5/1和2/1,VDD为2.5V,那么就可以直接计算出此时的Vin,然后带入等式两边任意一个就可以计算出此时的漏电流大小。

4、计算图中反相器平均传输延迟tP,其中CL=1pF

想要计算平均延迟时间,我们需要用到公式:

题目中已经给出了负载电容的值,高电平为2.5V,K值可计算,VT已经给出,直接带公式就可以。

四、基本单元电路

1、用静态 CMOS 电路:

(a) 实现两输入或非门

解:这道题可以看出,我们假设输入是A和B,输出为Y,此时nmos下拉电路负责A+B,pmos上拉电路负责!A·!B,或者可以通过真值表得到相同的结果,我们最终知道,或非的话,pmos是串联的,nmos是并联的

(b) 如果电路中各管的导电因子相同,即 KN=KP, VTN=-VTP,求输入 A 和 B 同步变化下的 KN,eff, KP,eff, Vit;求输入 A=0V,B 变化下的 KN,eff, KP,eff, Vit

解:这道题实际上就是让我们求等效的但cmos电路,我们需要知道串联和并联时候的电流关系,一nmos模块为例,并联的时候,可有如下的电流关系

![]()

所以可以有

![]()

同理,对pmos上拉电路,由于是串联的,同样有

![]()

即

![]()

综上,我们带入求Vit的公式,就可以有如下的结果:

当A和B都是高电平的时候

当A是低电平,B变化的情况下,上述电路中MN1截止,只有MN2起作用,而MP1\MP2都起作用,此时有

![]()

带入有

© 根据(b)的结果参考教材图 4.1-9 试定性的画出两输入或非门直流电压传输特性

解:根据第二问的结果我们知道,我们需要画出两条线,分别针对两种情况,故此可以有:

2、 画出利用静态电路实现![]() 的电路图,要求使用的 MOS 管最少;假定

的电路图,要求使用的 MOS 管最少;假定![]() ,NMOS 载流子迁移率为 PMOS 管的 2.5 倍,设计每个管子的宽长比,使得电路在最坏情况下的上升时间和下降时间相等。(假设 NMOS 工艺的最小 W/L 为 2/1)

,NMOS 载流子迁移率为 PMOS 管的 2.5 倍,设计每个管子的宽长比,使得电路在最坏情况下的上升时间和下降时间相等。(假设 NMOS 工艺的最小 W/L 为 2/1)

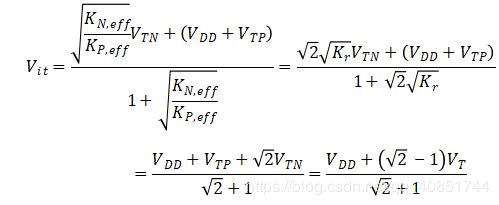

解:首先我们要对上式进行处理,化成这种形式的时候所用到的mos管是最少的

根据公式![]()

![]() 其中

其中![]()

要使得电路在最坏情况下的上升时间与下降时间相等,即需要使NMOS管的等效反相器宽长比与PMOS管的等效反相器宽长比满足关系式:

![]()

这里指的是我们计算得到的等效mos管的宽长比

最终我们可以得到这样的电路

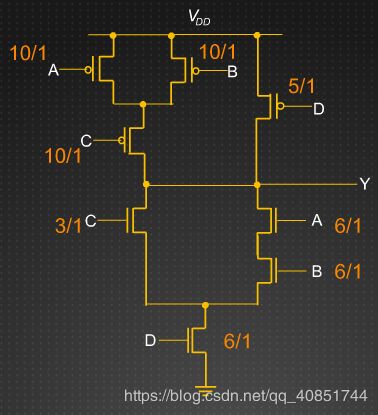

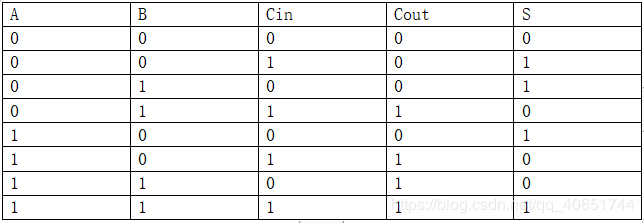

3、一位全加器的输入为A,B,Cin,其中A,B为操作数,Cin为进位输入,设此一位全加器的进位输出为Cout 。

(a)请根据 A, B, Cin 的不同逻辑取值真值表,列出的真值表;

解:

(b)根据上问得到的真值表,选取下面正确的一些CMOS静态电路的组件拼接成镜像一位加法器的进位电路。

解:

尽可能的让输出为0的一组,输出为1的一组,如图所示: