目录:

-

系统时钟的时钟源

-

HSE时钟

-

HSI时钟

-

锁相环时钟PLLCLK

-

配置系统时钟流程(重要!)

-

SystemInit固件库函数

-

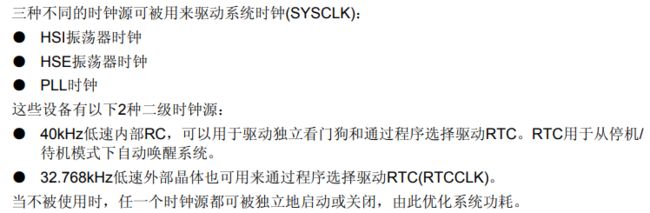

系统时钟的时钟源

系统时钟来源可以是HSI内部晶振(上)、HSE外部晶振(下)、(中间)PLL锁相环时钟(由(HSI/2或HSE)经过倍频所得)。

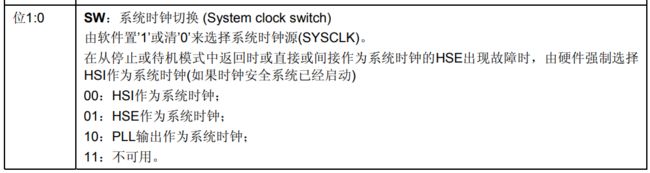

控制选择系统时钟源:RCC_CFGR寄存器的位1:0 SW:系统时钟切换

-

HSE时钟

HSE:High Speed-External Clock signal,即高速的外部时钟。

来源:无源晶振(4-16M),通常使用8M,硬件电路如下

控制:RCC_CR时钟控制寄存器的位16:HSEON控制

因为是无源晶振,要接电容接地,启动需要一定时间,RCC_CR的位17用来读取外部晶振就绪标志

-

HSI时钟

HSI:Low Speed Internal Clock signal,高速的内部时钟。(相比于HSE,HSE更精确)

来源:芯片内部,大小为8M,当HSE故障时,系统时钟会自动切换到HSI,直到HSE启动成功。

控制:RCC-CR时钟控制寄存器的位0:HSION控制

-

锁相环时钟PLLCLK

来源:(HSI/2、HSE)经过倍频所得。一般常用HSE的8M*PLL9倍频=72M。

控制:CFGR:PLLXTPRE,PLLMUL

注意:PLL时钟源头使用HSI/2的时候,PLLMUL最大只能是16,这个时候PLLCLK最大只能是64M,小于ST官方推荐的最大时钟72M

-

HCLK时钟

配置好系统时钟后,AHB下有很多总线,APB1、APB2下挂着很多外设。

HCLK:AHB高速总线时钟,速度最高为72M,为AHB总线的外设提供时钟、为Cortex系统定时器提供时钟(SysTick)、为内核提供时钟(FCLK)

来源:系统时钟分频得到,一般设置HCLK-SYSCLK-72M

控制:CFGR:HPRE

-

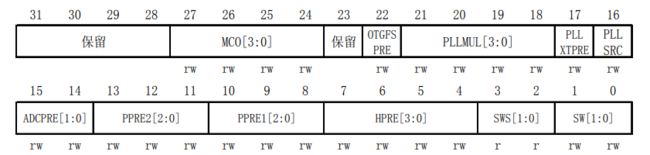

配置系统时钟流程(重要!)

- 选择HSE的8M,PLL选择为9倍频后,8*9为72M。

- 选择系统时钟源为PLL锁相环时钟。

- 选择AHB高速总线时钟(HCLK)为1分频,即为72M。

- 因为APB1最大为36M,设置APB1时钟为2分频,即为36M。

- 设置APB2时钟为1分频,即为72M。

补充:CSS时钟安全系统:

时钟安全系统可以通过软件被激活。一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被 使能,并在HSE时钟关闭后关闭。 如果HSE时钟发生故障,HSE振荡器被自动关闭,时钟失效事件将被送到高级定时器(TIM1和 TIM8)的刹车输入端,并产生时钟安全中断CSSI,允许软件完成营救操作。此CSSI中断连接到 Cortex™-M3的NMI中断(不可屏蔽中断)。

如果HSE振荡器被直接或间接地作为系统时钟,(间接的意思是:它被作为PLL输入时钟或通过 PLL2,并且PLL时钟被作为系统时钟),时钟故障将导致系统时钟自动切换到HSI振荡器,同时 外部HSE振荡器被关闭。在时钟失效时,如果HSE振荡器时钟(直接的或通过PLL2)是作为PLL 的输入时钟,PLL也将被关闭。

-

SystemInit固件库函数

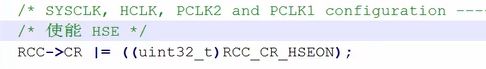

系统在复位程序时调用SystemInit固件库函数配置系统时钟为72MHz。

会调用SetSysClockTo72(void)函数,粗线条地配置好各总线的时钟:

1、使能HSE,配置RCC_CR寄存器的位16 HSEON:外部高速时钟使能(0:HSE振荡器关闭; 1:HSE振荡器开启。)

2、等待HSE就绪,读取RCC_CR寄存器的位17 HSERDY:外部高速时钟就绪标志(0:外部3-25MHz时钟没有就绪; 1:外部3-25MHz时钟就绪。)

3、HSE启动成功后,做对应处理。

配置RCC_CFGR的位4:13,设置AHB时钟不分频、APB1时钟2分频(100)、APB2时钟不分频(000)

配置RCC_CFGR的位16:21,设置PLL输入时钟源为HSE、PLL9倍频。

4、PLL、AHB、APB1、APB2分频或倍频配置好后,使能锁相环时钟PLL,配置PCC_CR寄存器位24 PLLON:PLL使能 (0:PLL关闭; 1:PLL使能。)

5、使能PLL以后,选择PLL为系统时钟,配置RCC_CFGR寄存器位1:0 SW:系统时钟切换(00:HSI作为系统时钟; 01:HSE作为系统时钟; 10:PLL输出作为系统时钟; 11:不可用。)