https://mp.weixin.qq.com/s/5J74euYsxkjlS1QSWU6_Ow

简单介绍BaseTile的实现。

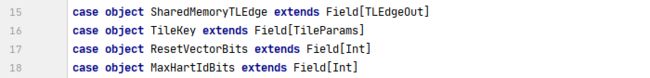

1. Keys

定义了一组配置的Key:

其中:

a. SharedMemoryTLEdge:从实现上看,是系统总线的第一条连接边:

b. TileKey:用于定义TileParams;

c. ResetVectorBits:用于定义复位向量的位宽;

d. MaxHartIdBits:用于定义表示核心数量所需要的最大位数;

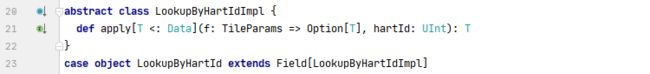

2. LookupByHartId

根据HartId查找一个值(T):

已在HasTiles中介绍,这里略去。

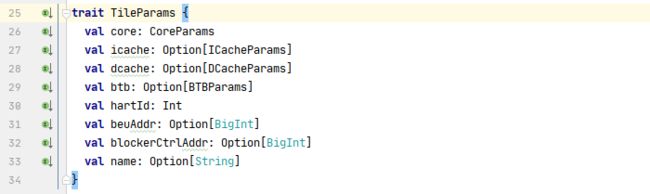

3. TileParams

定义核心需要的参数:

a. core:核心参数;

b. icache:指令缓存参数;

c. dcache:数据缓存参数;

d. btb:分支预测相关参数;

e. hartId:核心编号;

f. beuAddr:bus error unit地址;

g. blockerCtrlAddr:BasicBusBlocker的控制地址;

h. name:名称;

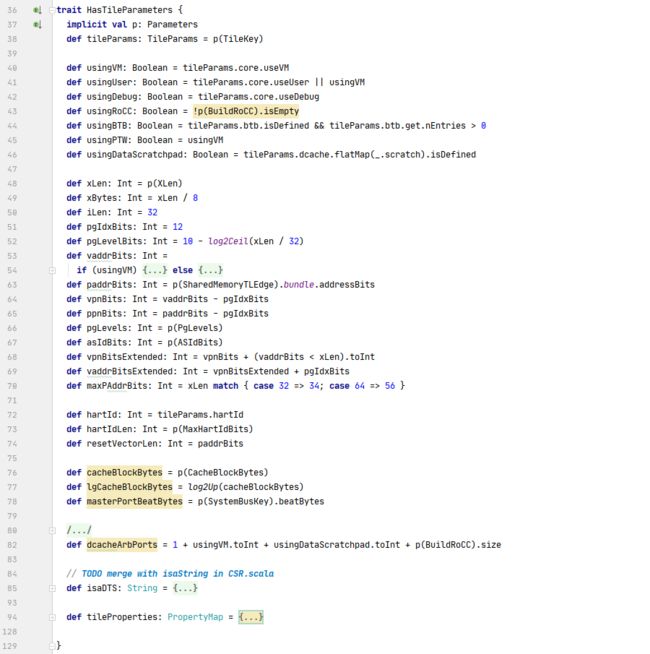

4. HasTileParameters

定义一组获取参数的方法,简化参数的使用:

这里不展开逐个介绍。

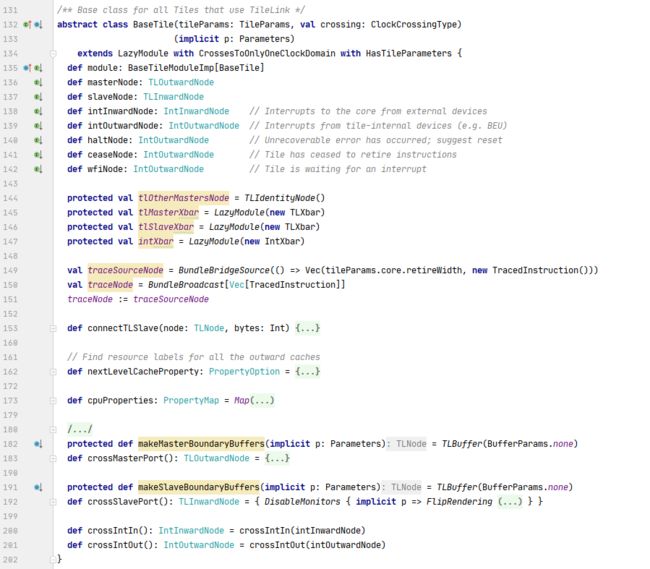

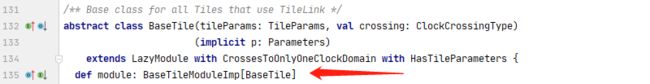

5. BaseTile

BaseTile是一个LazyModule,BaseTileModuleImp实现BaseTile引入的节点的逻辑。两者配对进行使用:

1) 抽象的lazy val module

在子类中实现:

2) 抽象的diplomacy nodes

其中:

a. masterNode/slaveNode:用于与其他节点相连的上下游节点;

b. intInwardNode/intOutwardNode:用于连接中断相关的节点;

c. haltNode:这是一个IntOutwardNode,用于发出不可恢复的错误中断,建议进行复位动作;

d. ceaseNode:这是一个IntOutwardNode,用于通知外部自己的停止状态;

e. wfiNode:这是一个IntOutwardNode,用于通知外部自己在等待中断;

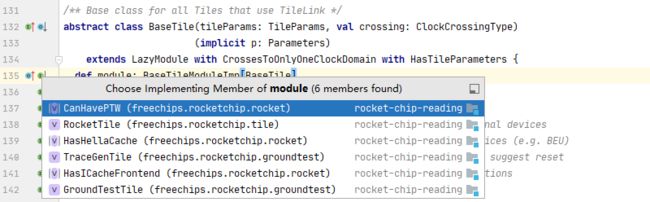

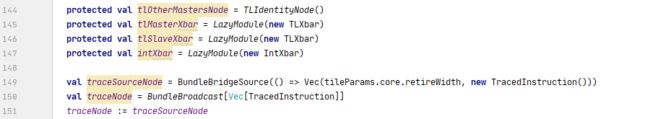

3) 其他nodes

还定义了一些其他的diplomacy node:

4) connectTLSlave

用于把tile与一个下游节点node相连接:

其结构示意图如下:

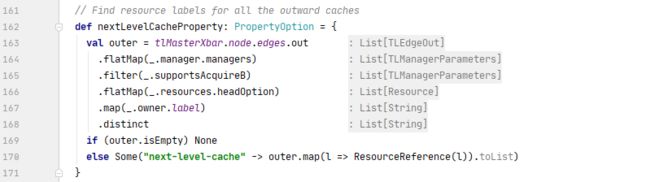

5) nextLevelCacheProperty

6) cpuProperties

7) makeMasterBoundaryBuffers

当前实现是一个深度为0的buffer:

8) crossMasterPort

a. tlMasterXing是一个TLOutwardCrossingHelper,用于根据crossing类型生成跨时钟结构;

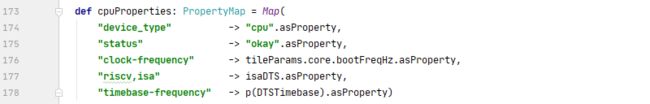

b. 根据需要在masterNode下游添加一个Buffer:

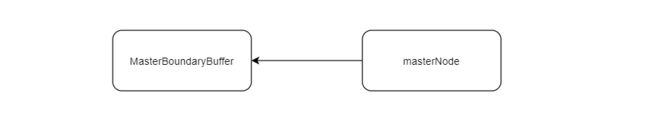

c. 根据跨域类型,生成最终的跨时钟结构。以RationalCrossing为例,其结构示意图如下:

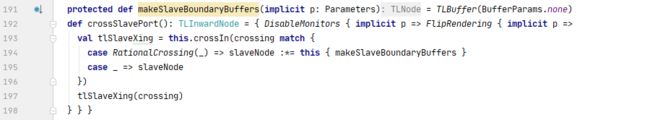

9) makeSlaveBoundaryBuffers

参考makeMasterBoundaryBuffers。

10) crossSlavePort

参考crossMasterPort。

11) crossSlavePort

生成上游中断节点连接到当前tile的跨时钟结构:

12) crossIntOut

生成当前tile的中断节点连接到下游节点的跨时钟结构。

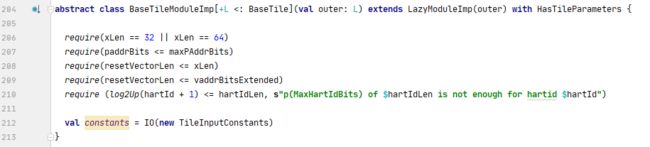

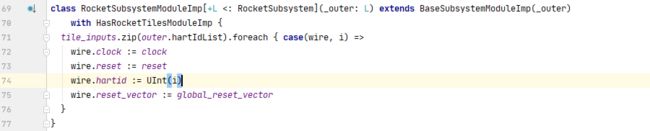

6. BaseTileModuleImp

BaseTileModuleImp作为LazyModuleImp的子类,与BaseTile成对使用,以实现BaseTile中的具体逻辑:

a. 增加一些有效性验证;

b. 添加一组静态IO: TileInputConstants;之所以成为静态是因为其值都是固定不变的;

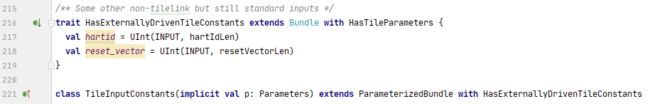

7. TileInputConstants

TileInputConstants是一个参数化的Bundle:

8. HasExternallyDrivenTileConstants

TileInputConstants继承了HasExternallyDrivenTileConstants中的输入输出端口:

a. hartId:核心编号;

b. reset_vector:复位向量;

Constants意指二者的值在生成时即确定,后续保持不变: