STM32 FSMC简介(二)

以下内容整理自《STM32中文参考手册》、正点原子《STM32F1开发指南--库函数版》、野火《零死角玩转STM32F103霸道V2》,仅为个人学习方便所整理

4.AHB接口的作用:(1)为内部CPU和其它总线控制设备访问外部静态存储器提供了通道;(2)AHB操作被转换到外部设备的操作,当选择的外部存储器的数据通道是16或8位时,在AHB上的32位数据会被分割成连续的16或8位的操作;(3)AHB时钟(HCLK)是FSMC的参考时钟。

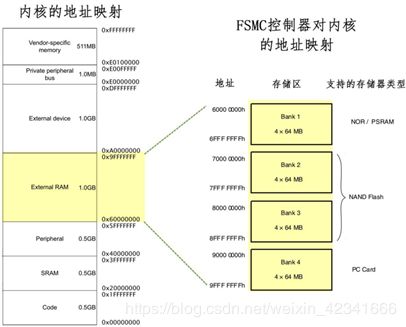

5.外部设备地址映像:使用FSMC外接存储器时,其存储单元是映射到STM32的内部寻址空间的;在程序里,定义一个指向这些地址的指针,然后就可以通过指针直接修改该存储单元的内容,FSMC外设会自动完成数据访问过程,读写命令之类的操作不需要程序控制。FSMC的地址映射见图2。

图2 FSMC的地址映射

图中左侧的是Cortex-M3内核的存储空间分配,右侧是STM32 FSMC外设的地址映射。可以看到FSMC的NOR/PSRAM/SRAM/NAND FLASH以及PC卡的地址都在External RAM地址空间内。正是因为存在这样的地址映射,使得访问FSMC控制的存储器时,就跟访问STM32的片上外设寄存器一样(片上外设的地址映射即图中左侧的“Peripheral”区域)。

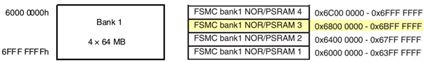

FSMC把整个External RAM存储区域分成了4个Bank区域,并分配了地址范围及适用的存储器类型,如NOR及SRAM存储器只能使用Bank1的地址。 在每个Bank的内部又分成了4个小块,每个小块有相应的控制引脚用于连接片选信号,如FSMC_NE[4:1]信号线可用于选择BANK1内部的4小块地址区域,见图3,当STM32访问 0x68000000-0x6BFFFFFF地址空间时,会访问到 Bank1的第3小块区域,相应的FSMC_NE3信号线会输出控制信号。

图3 Bank1内部的小块地址分配

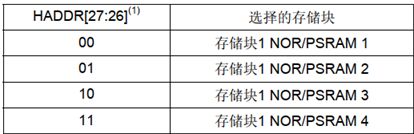

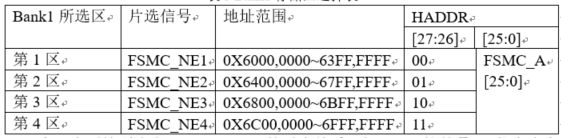

Bank1的256M字节空间由28根地址线(HADDR[27:0])寻址。这里HADDR 是内部AHB地址总线,其中HADDR[25:0]来自外部存储器地址FSMC_A[25:0],而HADDR[26:27]对4个区进行寻址,如表4所示。

表4 NOR/PSRAM存储卡选择

HADDR是字节地址,而存储器访问不都是按字节访问,因此接到存储器的地址线依存储器的数据宽度有所不同,如表5:

表5 Bank1存储区选择表

表5中要特别注意HADDR[25:0]的对应关系:当Bank1接的是16位宽度存储器的时候:HADDR[25:1]à FSMC-A[24:0];当Bank1接的是8位宽度存储器的时候:HADDR[25:0]à FSMC_A[25:0]。不论外部接8 位/16位宽设备, FSMC_A[0]永远接在外部设备地址A[0]。另外,HADDR[27:26]的设置是不需要我们干预的,比如当选择使用Bank1的第三个区,要做的就是配置对应第 3 区的寄存器组,来适应外部设备即可。

6.SRAM时序结构体:控制FSMC使用SRAM存储器时主要是配置时序寄存器以及控制寄存器,利用ST标准库的SRAM时序结构体以及初始化结构体可以很方便地写入参数。SRAM时序结构体的成员见代码清单1。

代码清单1 SRAM时序结构体 FSMC_NORSRAMTimingInitTypeDef

这个结构体成员定义的都是 SRAM 读写时序中的各项时间参数,这些成员的参数都与FSMC_BRT及FSMC_BWTR寄存器配置对应,各个成员介绍如下:

(1) FSMC_AddressSetupTime:设置地址建立时间,可以被设置为0-0xF个 HCLK周期数,按STM32标准库的默认配置,HCLK的时钟频率为72MHz,即一个HCLK周期为1/72微秒。

(2) FSMC_AddressHoldTime:设置地址保持时间,可以被设置为0-0xF个 HCLK周期数。

(3) FSMC_DataSetupTime:设置数据建立时间,可以被设置为0-0xF个 HCLK周期数。

(4) FSMC_BusTurnAroundDuration:设置总线转换周期,在 NOR FLASH存储器中,地址线与数据线可以分时复用,总线转换周期就是指总线在这两种状态间切换需要的延时,防止冲突。控制其它存储器时这个参数无效,配置为0即可。

(5) FSMC_CLKDivision:设置时钟分频,以HCLK时钟作为输入,经过 FSMC_CLKDivision分频后输出到FSMC_CLK引脚作为通讯使用的同步时钟。 控制其它异步通讯的存储器时这个参数无效,配置为0即可。

(6)FSMC_DataLatency:设置数据保持时间,表示在读取第一个数据之前要等待的周期数,该周期指时钟的周期,仅用于同步NOR FLASH类型的存储器,控制其它类型的存储器时无效。

(7) FSMC_AccessMode:设置存储器访问模式,不同的模式下FSMC访问存储器地址时引脚输出的时序不一样,可选FSMC_AccessMode_A/B/C/D 模式。 一般来说控制SRAM时使用A模式。

FSMC_NORSRAMTimingInitTypeDef时序结构体配置的延时参数,将作为FSMC SRAM初始化结构体的一个成员。

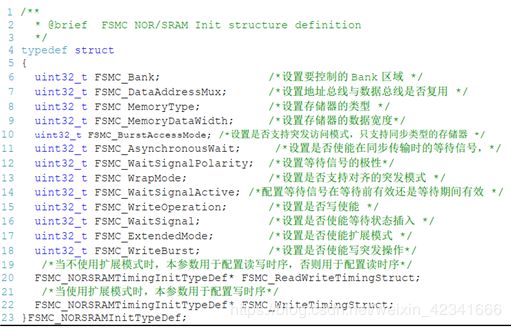

7.SRAM初始化结构体:FSMC的SRAM初始化结构体见代码清单2

代码清单2 SRAM初始化结构体FSMC_NORSRAMInitTypeDef

这个结构体,除最后两个成员是时序配置外,其它结构体成员的配置都对应到FSMC_BCR中的寄存器位。各个成员意义介绍如下,括号中的是STM32标准库定义的宏:

(1) FSMC_Bank:用于选择FSMC映射的存储区域,可选参数以及相应的内核地址映射范围见表6。

表6 可以选择的存储器区域及区域对应的地址范围

| 可以输入的宏 |

对应的地址区域 |

| FSMC_Bank1_NORSRAM1 |

0x60000000-0x63FFFFFF |

| FSMC_Bank1_NORSRAM2 |

0x64000000-0x67FFFFFF |

| FSMC_Bank1_NORSRAM3 |

0x68000000-0x6BFFFFFF |

| FSMC_Bank1_NORSRAM4 |

0x6C000000-0x6FFFFFFF |

(2) FSMC_DataAddressMux:设置地址总线与数据总线是否复用,在控制 NOR FLASH 时,地址总线与数据总线可以分时复用,以减少使用STM32信号线的数量。

(3) FSMC_MemoryType:设置要控制的存储器类型,它支持控制的存储器类型为 SRAM、 PSRAM以及 NOR FLASH。

(4) FSMC_MemoryDataWidth:设置要控制的存储器的数据宽度,可选择设置 成8或16位。

(5) FSMC_BurstAccessMode:设置是否使用突发访问模式,突发访问模式是指发送一个地址后连续访问多个数据,非突发模式下每访问一个数据都需要输入一个地址,仅在控制同步类型的存储器时才能使用突发模式。

(6) FSMC_AsynchronousWait:设置是否使能在同步传输时使用的等待信号,在控制同步类型的NOR或PSRAM时,存储器可以使用FSMC_NWAIT引脚通知STM32需要等待。

(7) FSMC_WaitSignalPolarity:设置等待信号的有效极性,即要求等待时,使用高电平还是低电平。

(8)FSMC_WrapMode:设置是否支持把非对齐的AHB突发操作分割成2次线性操作,该配置仅在突发模式下有效。

(9) FSMC_WaitSignalActive:配置在突发传输模式时,决定存储器是在等待状态之前的一个数据周期有效还是在等待状态期间有效。

(10)FSMC_WriteOperation:设置是否写使能,禁止写使能的话FSMC只能从存储器中读取数据,不能写入。

(11) FSMC_WaitSignal:设置当存储器处于突发传输模式时,是否允许通过 NWAIT信号插入等待状态。

(12) FSMC_ExtendedMode:设置是否使用扩展模式,在非扩展模式下,对存储器读写的时序都只使用FSMC_BCR 寄存器中的配置,即下面的FSMC_ReadWriteTimingStruct结构体成员;在扩展模式下,对存储器的读写时序可以分开配置,读时序使用 FSMC_BCR寄存器,写时序使用FSMC_BWTR寄存器的配置,即下面的FSMC_WriteTimingStruct结构体。

(13) FSMC_ReadWriteTimingStruct:本成员是一个指针,赋值时使用时序结 构体FSMC_NORSRAMInitTypeDef设置, 当不使用扩展模式时,读写时序都使用本成员的参数配置。

(14) FSMC_WriteTimingStruct:本成员也是一个时序结构体的指针,只有当使用扩展模式时,本配置才有效,它是写操作使用的时序。

对本结构体赋值完成后,调用 FSMC_NORSRAMInit 库函数即可把配置参数写入到FSMC_BCR 及 FSMC_BTR/BWTR 寄存器