Vivado浮点数计算IP核介绍及简单运用仿真

1、Vivado浮点数计算IP核介绍

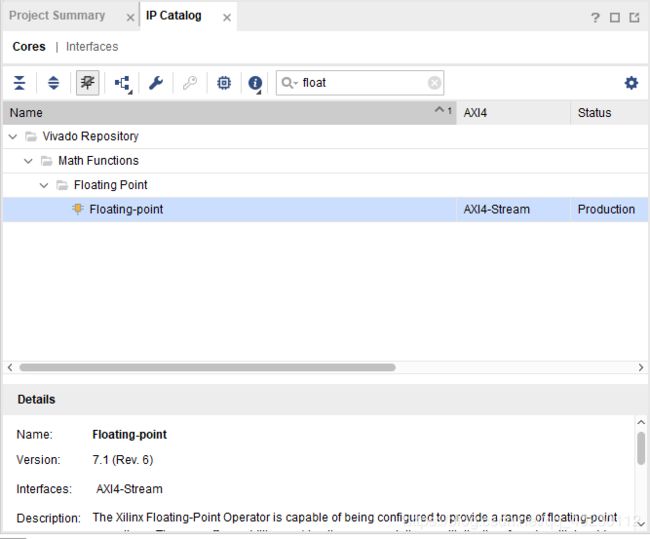

打开Vivado软件,点击IP Catalog,输入float关键词进行搜索,可以看到有Float-point这个IP核,双击打开

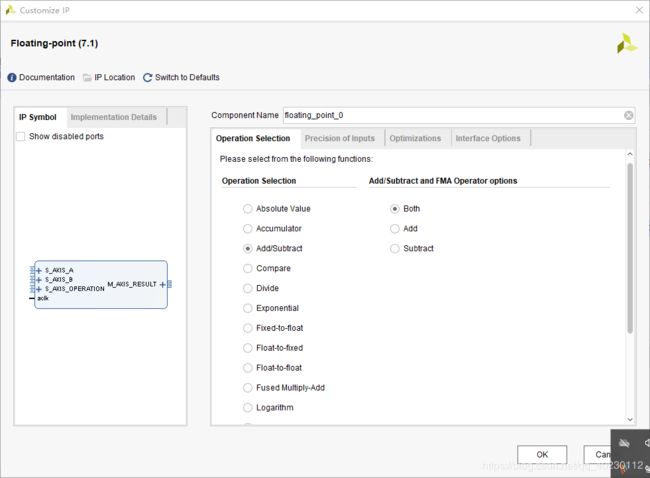

在Operation Selection中可以按照自己的需求配置成加法器,减法器,乘法器,除法器,乘加器等,如果在这里选择加法和减法同时用的话,接口会增加一个操作模式选择信号。

在Precision of Inputs中可以设置数据的存储格式,一般不做修改,保持默认。

在Optimizations中可以根据需要进行优化,优化选项有高速,低延时以及面积优化,根据实际需求看要求是高速度,还是低延时,还是要求很少的资源利用面积来进行选择。

在Interface Options中可以根据需要配置所需要的接口,看是否选择时钟使能端口,复位端口等。

2、简单运用仿真

我们在Modelsim2019.2中对浮点数计算IP核进行独立仿真,首先在Vivado中创建浮点数计算IP核,然后将IP核仿真文件添加到Modelsim2019.2仿真工程中,进行仿真。相关测试文件如下:

`timescale 1ns / 1ps

module Tb();

reg aclk;

reg aresetn;

initial

begin

aclk=1'b1;

aresetn=1'b1;

#5 aresetn=1'b0;

#5 aresetn=1'b1;

end

always #5 aclk=~aclk;

//32'h3E4CCCCD=0.2,32'h4047AE14=3.12,32'h4084CCCD=4.15

//计算结果应该是0.2*3.12+4.15=4.774=32'h4098C49C

wire m_axis_result_tvalid;

wire [31:0] m_axis_result_tdata ;

float_mul_add float_mul_add_1 (

.aclk(aclk), // input wire aclk

.aresetn(aresetn), // input wire aresetn(active low)

.s_axis_a_tvalid(1'b1), // input wire s_axis_a_tvalid

.s_axis_a_tdata(32'h3E4CCCCD), // input wire [31 : 0] s_axis_a_tdata

.s_axis_b_tvalid(1'b1), // input wire s_axis_b_tvalid

.s_axis_b_tdata(32'h4047AE14), // input wire [31 : 0] s_axis_b_tdata

.s_axis_c_tvalid(1'b1), // input wire s_axis_c_tvalid

.s_axis_c_tdata(32'h4084CCCD), // input wire [31 : 0] s_axis_c_tdata

.m_axis_result_tvalid(m_axis_result_tvalid), // output wire m_axis_result_tvalid

.m_axis_result_tdata(m_axis_result_tdata) // output wire [31 : 0] m_axis_result_tdata

);

endmodule

注:如何在Modelsim中独立仿真Vivado的IP核详见链接:https://blog.csdn.net/weixin_38712697/article/details/80720428

Modelsim2019.2仿真结果如下图所示:

从上图中的仿真结果可以看出,仿真结果是32’h4098c49c ,与预期计算结果一致。