基于proteus的51单片机仿真实例十、51单片机的P0口的工作原理

单片机系统功能实现的最基本和最主要方式是:检测I/O端口输入的各种数据、控制I/O端口输出各种数据。

单片机系统的工作过程通常是:外部电路的运行情况通过I/O端口输入到单片机,单片机程序读取输入的数据并进行分析后,根据不同情况控制I/O端口输出不同的数据,从而实现控制相关外围电路执行相应操作的功能。

所以,学习单片机的第一步就是学会如何让单片机的I/O口实现输入和输出功能。

本例实现用单片机的P0口控制8个LED点亮和熄灭,实现流水灯的效果。

通过这个实例,了解以下知识:

硬件电路:LED的工作原理及控制电路;

程序设计:编写程序,控制单片机I/O口输出电平的高低。

1、51单片机的引脚(端口)

单片机是通过它的一个个引脚来实现对外部事件的检测和控制的,所以拿到一个单片机时,首先应对它的管脚进行分析。只有弄清楚一个单片机的各个管脚的功能和作用,才能够实现外围电路的设计和程序设计。

2、51单片机管脚的分类和功能介绍

AT89C51单片机共有40个引脚,按照各自功能可以分为三类:电源和时钟引脚、系统控制引脚、输入/输出引脚(也即I/O口)。下面分别介绍:

1)电源和时钟引脚:这些引脚主要为单片机系统提供工作电源和时钟信号,包括电源和地引脚VCC(40脚)、GND(20脚),时钟信号输入输出引脚XTAL1(19脚)、XTAL2(18脚)

2)系统控制引脚:系统控制改制引脚有:PSEN(29脚) ,EA/VPP(31脚), ALE(30脚) ,RST(9脚),功能分别是:

PSEN 外部程序存储器读选通信号:在读外部ROM时PSEN低电平有效,以实现外部ROM单元的读操作。

EA/VPP 访问程序序存储器控制信号。

ALE 地址锁存控制信号。

RST 复位信号:当输入的信号连续2个机器周期以上高电平时即为有效,用以完成单片机的复位初始化操作。

3)输入/输出引脚(I/O口)

AT89S52单片机有4个8位的I/O口,分别是P0(P0.0~P0.7,引脚39-32),P1(P1.0~P1.7,引脚1-8),P2(P2.0~P2.7,引脚21-28),P3(P3.0~P3.7,引脚10-17)。这4个I/O端口的结构功能各不相同,本例中用到的是P0口,我们先讲解P0口的工作原理,另外3个I/O端口的工作原理将在后面逐步了解。

P0口有三个功能:

外部扩展存储器时,当做数据总线

外部扩展存储器时,当作地址总线

不扩展时,可做一般的I/O使用,但内部无上拉电阻,作为输入或输出时应在外部接上拉电阻。

3、P0口的结构和工作原理

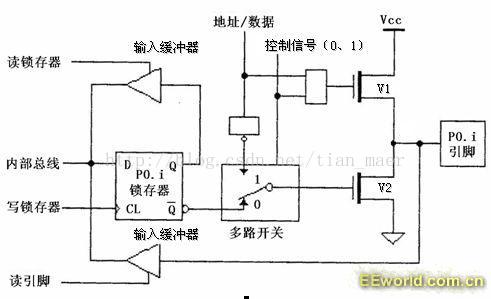

P0口有8位,分别对应P0-P7这8个引脚,下图是其中一个引脚的内部结构图。从图中可以看出,该引脚内部包括1个输出锁存器、2个三态缓冲器、1个输出驱动电路1个输出控制端。

输出驱动电路有两个场效应管组成,其工作状态受输出端的控制。

输出控制端由1个与门、一个反相器和一个多路转换开关组成。

我们先来分析组成P0口的每个单元部份:

输入缓冲器:在P0口中,有两个三态的缓冲器,所谓的三态,是指在缓冲器的输出端可以输出高电平、低电平、高阻态(禁止状态)这三种状态,在上图中,在读锁存器端口,要读取D锁存器输出端Q的数据,必须使使读锁存器的这个缓冲器的三态控制端(图中标号为‘读锁存器’端)有效。而在读引脚端口,要读取P0.i引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,这样引脚上的数据才会传输到单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,我们知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。上图中的D锁存器,D端是数据输入端,CL是控制端(即时序控制信号输入端),Q是输出端,/Q是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CL没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。一旦时序控制端CL的时序脉冲到了,D端输入的数据就会传输到Q及Q非端。数据传送过来后,当CL时序控制端的时序信号消失了,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(不需要外扩展存储器时,这里说的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O口)使用,当需要外扩存储器时,P0口就作为‘地址/数据’总线使用。这个多路选择开关就是用于选择是做为普通I/O口使用还是作为‘数据/地址’总线使用的选择开关。在上中,当多路开关与下面接通时,P0口作为普通的I/O口使用,当多路开关与上面接通时,P0口作为‘地址/数据’总线使用。

输出驱动部份:从上图可以看出,P0口的输出是由两个MOS管组成的推拉式结构,也就是说,这两个MOS管一次只能导通一个,当V1导通时,V2就截止,当V2导通时,V1截止。

与门、与非门:与门电路的逻辑原理是:将输入端的所有输入信号进行“逻辑与”运算,然后将结果输出;与非门电路的逻辑原理是:将输入端的所有输入信号进行“逻辑与非”运算,然后将结果输出。

前面我们已将P0口的各单元部件进行了一个详细的讲解,接下来我们来研究一下P0口做为I/O口及地址/数据总线使用时的具体工作过程。

1、作为I/O端口使用时的工作原理

P0口作为I/O端口使用时,多路开关的控制信号为0(低电平,即多路开关向下闭合),在上图中,多路开关的控制信号同时与与门的一个输入端相连,与门的逻辑特点是“全1出1,有0出0”,那么如果控制信号是0的话,这时与门输出的也是一个0(低电平),由于该与门的输出是0,V1管就截止,在多路控制开关的控制信号是0(低电平)时,多路开关是与锁存器的/Q端相接的(即P0口作为I/O口线使用)。

P0口用作I/O口线时,由数据总线向引脚输出(即输出状态Output)的工作过程是:当写锁存器信号CL有效,数据总线的信号→锁存器的输入端D→锁存器的反向输出端/Q→多路开关→V2管的栅极→V2的漏极到输出端口P0.i。前面已经介绍,当多路开关的控制信号为低电平0时,与门输出为低电平,V1管截止,所以作为输出口时,P0是漏极开路输出,类似于OC门,也就是说,当数据总线输出0时,V2导通,则引脚直接接到地,输出的电平自然就是低电平了,但是当数据总线输出1时,V2截止,由于这时V也截止了,这时引脚既没有接高电平VCC,也没有接低电平GND,相当于处在一个悬空状态。但是我们的目的是要输出高电平,这时就需要在引脚上外接上拉电阻,确保数据总线输出1时,引脚也输出高电平(这就是我们平时说P0口需要接上拉电阻的原因)。

下图就是由内部数据总线向P0口输出数据的数据流向图(黑色加粗箭头指示)。

P0口用作I/O口线时,由引脚向内部数据总线输入(即输入状态Input)的工作过程:

数据输入时(读P0口)有两种情况

1、读引脚

读芯片引脚上的数据,读引脚数时,读引脚缓冲器打开(即三态缓冲器的控制端要有效),通过内部数据总线输入,如下图所示(黑色加粗箭头指示)。

P0口做输入端口时,输入信号将被送到读引脚的三态缓冲器和V2的漏极,如果锁存器之前锁存的是信号“0”,那么VT2导通,这时无论引脚上的电平信号是高电平还是低电平,由于引脚直接与地相连,都只能读到“0”。所以,在读取引脚的输入信号之前,需要先通过内部数据总线向锁存器写入“1”信号,使V2截止,这时才能争取读取到引脚上的输入信号(这就是常说的在读P0引脚输入信号前,先要向该引脚输出信号”1“的原因)

2、读锁存器

通过打开读锁存器三态缓冲器读取锁存器输出端Q的状态,如下图所示(黑色加粗箭头指示):

在输入状态下,从锁存器和从引脚上读来的信号一般是一致的,但也有例外。例如,当从内部总线输出低电平后,锁存器Q=0,/Q=1,场效应管T2开通,端口呈低电平状态。此时无论端口线上外接的信号是低电乎还是高电平,从引脚读入单片机的信号都是低电平,因而不能正确地读入端口引脚上的信号。又如,当从内部总线输出高电平后,锁存器Q=1,Q非=0,场效应管T2截止。如外接引脚信号为低电平,从引脚上读入的信号就与从锁存器读入的信号不同。因此,51单片机在对端口P0一P3的输入操作上,需要注意:凡属于读-修改-写方式的指令,从锁存器读入信号,其它指令则从端口引脚线上读入信号。

读-修改-写指令的特点是,从端口输入(读)信号,在单片机内加以运算(修改)后,再输出(写)到该端口上。这样安排的原因在于读-修改-写指令需要得到端口原输出的状态,修改后再输出,读锁存器而不是读引脚,可以避免因外部电路的原因而使原端口的状态被读错。