Vivado开发套件设计笔记(1)——入门简介

目录

- 1 简介

- 2 加速高层次设计

- 3 加速IP集成

- 4 加速设计验证

- 5 总结

- 6 参考文章

1 简介

Vivado™设计套件是一种新的以IP和系统为中心的设计环境,可加速未来十年全可编程设备的设计生产力。该套件采用一种基于下一代C/C++和基于IP的设计方式,为超高生产率提供了一种新方法。新的HLx版本包括HL System Edition,HL Design Edition和HL WebPACK™Edition。 与新的UltraFast™高级生产力设计方法指南相结合,用户可以实现比传统方法高10-15倍的生产率。

全可编程器件超越了可编程逻辑和I/O,它集成了3D堆叠硅互连技术、软件可编程ARM®处理系统、可编程模拟混合信号(AMS)和大量知识产权(IP)内核的各种组合。 这些新一代器件使设计人员能够超越可编程逻辑到可编程系统集成,将更多系统功能集成到更少的部件中,提高系统性能,降低系统功耗并降低BOM成本。

Vivado™设计套件在过去4年内从头开始构建,可以解决可编程系统集成和实施中的关键设计瓶颈,与竞争开发环境相比,可实现高达4倍的生产力优势。 对于传统的以逻辑为中心的FPGA,它还可以更轻松地创建设计,更快地满足时序要求,并自动化(无需指定),这会是开发者们偏爱的一种设计流程。

用一句话说,Vivado™设计套件利用了一种新的技巧使得开发者能更快地完成硬件上的设计,包括了FPGA电路设计和ARM程序设计,通过ARM与FPGA的配合使用使得开发者能更直观更简单地操作硬件。

本系列博文着眼于这一新的技巧,为刚入门的朋友们指明道路,从完整的大框架设计流程到每一个细节处的处理和优化,笔者都尽可能多地去提及,把踩过的坑都与各位分享,希望各位能少走弯路,不仅避开传统纯RTL级设计这一复杂的流程,更节省在新型设计方法中踩坑脱坑的时间。

2 加速高层次设计

传统的设计开发流程一般是,经验丰富的系统架构师估计如何在新技术中实现其设计,同时捕获系统连接要求和增值分配逻辑。反过来,RTL设计实现了这些要求。 RTL设计周期通常包括每个块的验证和设计闭环迭代,乃至整个综合的设计。作为该方法的结果,平台连接设计永远不会稳定,因为差异化逻辑中的任何变化都可能导致IO接口(例如DDR存储器,以太网,PCIe等等)不满足时序要求。此外,RTL验证周期不再允许在硬件启动之前进行详尽的功能测试。其设计流程大致如下图所示。

首先根据功能需求构建框架,将各功能模块化,接着定义模块之间的数据接口,最后利用一个时序模块控制各个功能模块的工作与空闲状态,最后再到硬件上布线。每一个模块都需要利用VHDL-Verilog模块设计,对于一些复杂的算法,RTL级别的设计相当复杂,代码量庞大,之后进行反复RTL仿真验证和修改,最后做完硬件上的布局后再做整体系统的验证。可以说,一个有复杂功能的系统,需要大量的人力和时间,而高层次设计方法则大大缩短了这一耗费。

高层次设计方法(HLx)将开发工作放在首位,使设计人员可以花更多的时间设计增值逻辑,减少在使得模块正常工作上反复尝试的时间。与RTL设计流程相比,此流程可将设计周期缩短15倍。这种高级方法的主要特征是:

- 指令驱动型架构感知综合可提供最优的 QoR;

- 在竞争对手还在手动开发 RTL 的时候快速实现 QoR;

- 使用 C/C++ 测试平台仿真、自动 VHDL 或 Verilog 仿真和测试平台生成加速验证;

- 自动使用 Xilinx 片上存储器、DSP 元素和浮点库;

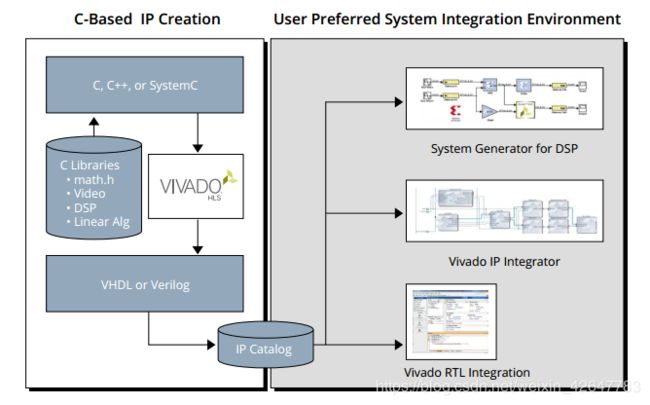

使用高层次设计的流程大致如下图所示。

开发者从C/C++或者SystemC语言入手,灵活运用HLS提供的各种库函数,然后再C层级上做验证,之后综合成VHDL或者Verilog语言,并封装成IP核,该过程相较于RTL级别功能块的直接VHDL-Verilog构建要省时的多。然后在Vivado软件上利用可视化人机交互布线工具快速完成IP核之间的连接。最终利用ARM核控制通过AXI协议等控制IP核之间的协调工作。整体过程的闭环迭代验证速度更快,准确性更高。

3 加速IP集成

Vivado® Design Suite 可提供业界首款即插即用型 IP 集成设计环境并具有IP 集成器特性,从而解决了 RTL 设计生产力问题。

Vivado IP Integrator 可提供基于 Tcl、设计期正确的图形化设计开发流程。IPI 特性可提供具有器件和平台意识的互动环境,能支持关键 IP 接口的智能自动连接、一键式 IP 子系统生成、实时 DRC 和接口修改传递等功能,此外还提供强大的调试功能。在 IP 之间建立连接时,设计人员工作在“接口”而不是“信号”的抽象层面上,从而大幅提升了生产力。 这通常采用业界标准的 AXI4 接口,不过 IP 集成器也支持数十个其它接口。

设计团队在接口层面上工作,能快速组装复杂系统,充分利用 Vivado HLS、System Generator、Xilinx SmartCore™ 和 LogiCORE™ IP 创建的 IP、联盟成员 IP 和自己的 IP。通过利用 Vivado IPI 和 HLS 的完美组合,客户能将开发成本相对于采用 RTL 方式而言节约高达 15 倍。

Vivado IP 集成器的优势包括:

- 在 Vivado 集成型设计环境中的紧密集成

- IP Integrator 层次化子系统在整个设计中的无缝整合

- 快速捕获与支持重复使用的 IP Integrator 设计封装

- 支持图形和基于 Tcl 的设计流程设计

- 快速仿真与多设计视窗间的交叉探测

- 支持所有设计域

- 支持处理器或无处理器设计

- 算法集成 (Vivado HLS 和 System Generator) 和 RTL-level IP

- 融 DSP、视、模拟、嵌入式、连接功能和逻辑为一体

- 注重设计生产力

- 可在设计装配过程中,通过复杂接口层面连接实现 DRC

- 常见设计错误的识别和纠正

- 互联 IP 的自动 IP 参数传递

- 系统级优化

- 自动设计辅助

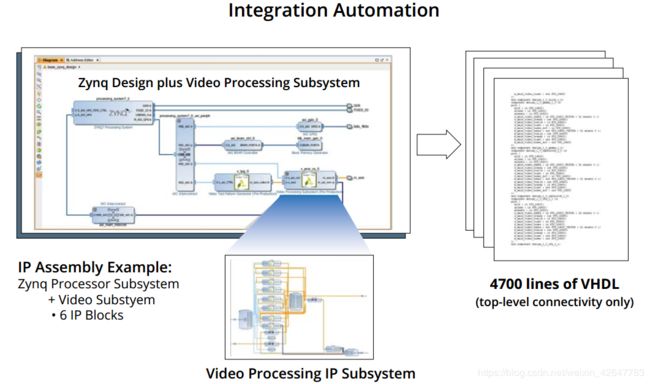

Vivado IP 集成器的例图如下所示:

对于用户自定义IP核的集成过程大致为:首先在IP Catalog中加入自定义IP核,然后在Block Design中将IP核导入,然后添加ZYNQ处理系统,之后对简单的应用可以自动连线,自动引出必要端口,然后对设计创建HDL Wrapper并生成输出的硬件,最后验证硬件并导出bit文件,即完成硬件电路上的集成,剩下的工作就是在ZYNQ上做程序设计了。

4 加速设计验证

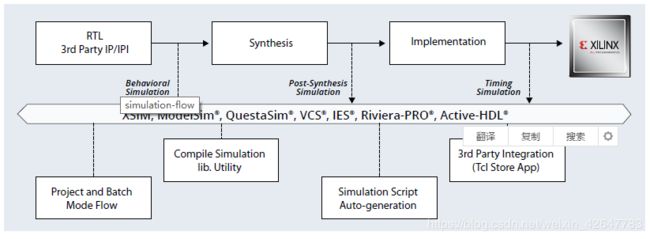

Vivado® Design Suite 可为单个业界一流集成设计环境 (IDE) 中所包含的第三方仿真器提供设计入口、时序分析、硬件调试以及仿真等一系列功能。对于所有所支持的仿真器而言,该流程都可满足集成型及企业验证需求。

Vivado 可为全面集成型 Vivado 仿真器以及第三方 HDL 仿真器实现行为、后期综合与后期实现功能或时序仿真。设计周期早期阶段多花点时间在仿真上,有助于提早识别问题,相对于在流程后期阶段多用时间而言,可显著减少转换时间。

为帮助在用户验证环境中实现高灵活性,Vivado 不仅提供对集成环境的支持,而且还提供各种脚本与外部验证设置联用。

Vivado 集成设计环境 (IDE) 有助于用户使用各种仿真集探索多种仿真策略。仿真集不仅允许用户在 Vivado IDE 下管理验证流程,而且还可根据验证需求创建不同的仿真流程。

5 总结

Vivado® Design Suite HLx 版本可为设计团队提供实现基于 C 的设计、重用优化、IP 子系统重复、集成自动化以及设计收敛加速所需的工具和方法。与 UltraFast™ 高层次生产力设计方法指南相结合,这种特殊组合经过验证,不仅可帮助设计人员以高层次抽象形式开展工作,同时还可促进重复使用,从而可加速生产力。

依据笔者的经验,简单系统的设计流程大致如下:首先在Vivado HLS软件上设计需要的IP核,然后在Vivado软件上添加IP核以及ZYNQ处理系统,完成相应的电路连接,最后在SDK软件上设计程序操作FPGA的电路,实现我们想要的功能。

6 参考文章

[1]: Xilinx官方文档 《wp416-Vivado Design Suite》

原创性声明:本文属于作者原创性文章,小弟码字辛苦,转载还请注明出处。谢谢~

如果有哪些地方表述的不够得体和清晰,有存在的任何问题,亦或者程序存在任何考虑不周和漏洞,欢迎评论和指正,谢谢各路大佬。

需要代码和有需要相关技术支持的可咨询QQ:297461921