56--vivado带通滤波器的设计

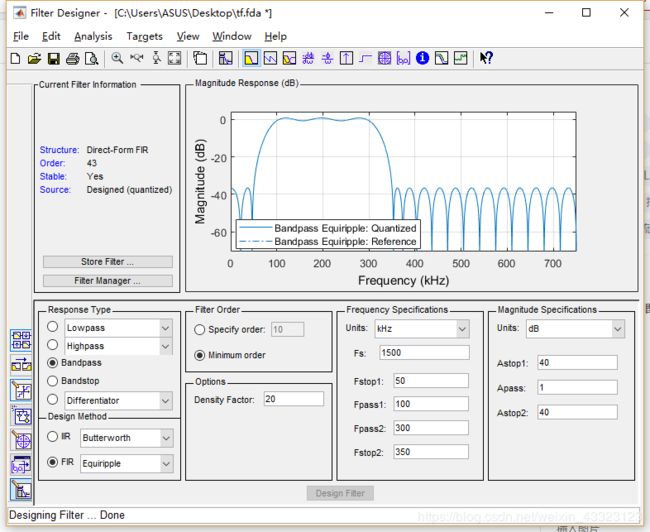

实现数字带通滤波器。参数如下:

通过频率1:100KHz;

通过频率2:300KHz;

阻带频率1:50KHz;

阻带频率2:350KHz;

通带波动:<1dB;

阻带衰减:>40dB。

ip核配置可参考之前文章。可在ip catalog 搜索fir,adder,dds来找到。(分别是滤波,加法器,波形生成)

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2020/06/06 16:52:59

// Design Name:

// Module Name: bandpass_top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module bandpass_top(

input clk,

input m_axis_data_tvalid,

input s_axis_data_tvalid,

output [15:0]m_axis_data_tdata_1,

output [15:0]m_axis_data_tdata_2,

output [15:0]m_axis_data_tdata_3,

output [16:0]s1,

output [17:0]S,

output [39:0] m_axis_data_tdata_fir

);

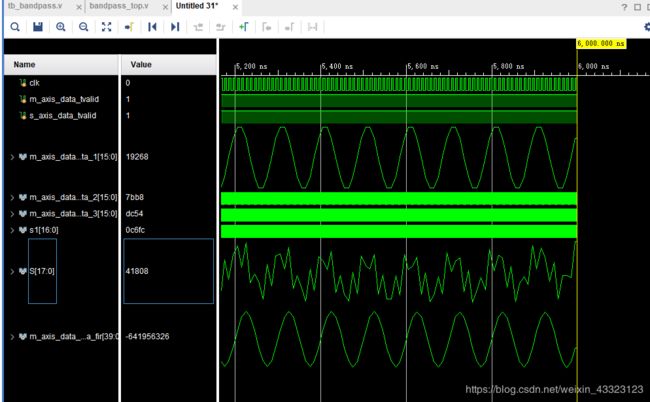

//200kHz

wire event_pinc_invalid_1,event_pinc_invalid_2,event_pinc_invalid_3;

wire event_poff_invalid_1,event_poff_invalid_2,event_poff_invalid_3;

wire m_axis_phase_tvalid_1,m_axis_phase_tvalid_2,m_axis_phase_tvalid_3;

wire m_axis_phase_tdata_1,m_axis_phase_tdata_2,m_axis_phase_tdata_3;

dds_compiler_0 dds_200 (

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata_1), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid_1), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata_1), // output wire [15 : 0] m_axis_phase_tdata

.event_pinc_invalid(event_pinc_invalid_1), // output wire event_pinc_invalid

.event_poff_invalid(event_poff_invalid_1) // output wire event_poff_invalid

);

//800kHz

dds_compiler_1 dds_800 (

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata_2), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid_2), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata_2), // output wire [15 : 0] m_axis_phase_tdata

.event_pinc_invalid(event_pinc_invalid_2), // output wire event_pinc_invalid

.event_poff_invalid(event_poff_invalid_2) // output wire event_poff_invalid

);

//10kHz

dds_compiler_2 dds_10(

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata_3), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid_3), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata_3), // output wire [15 : 0] m_axis_phase_tdata

.event_pinc_invalid(event_pinc_invalid_3), // output wire event_pinc_invalid

.event_poff_invalid(event_poff_invalid_3) // output wire event_poff_invalid

);

c_addsub_0 add1 (

.A(m_axis_data_tdata_1), // input wire [15 : 0] A

.B(m_axis_data_tdata_2), // input wire [15 : 0] B

.S(s1) // output wire [16 : 0] S

);

c_addsub_1 add2 (

.A(s1), // input wire [16 : 0] A

.B(m_axis_data_tdata_3), // input wire [15 : 0] B

.S(S) // output wire [17 : 0] S

);

wire s_axis_data_tready;

fir_compiler_0 fir1 (

.aclk(clk), // input wire aclk

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.s_axis_data_tdata(S), // input wire [23 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata_fir) // output wire [39 : 0] m_axis_data_tdata

);

endmodule

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2020/06/06 19:29:55

// Design Name:

// Module Name: tb_bandpass

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module tb_bandpass(

);

reg clk;

reg m_axis_data_tvalid;

reg s_axis_data_tvalid;

wire [15:0]m_axis_data_tdata_1;

wire [15:0]m_axis_data_tdata_2;

wire [15:0]m_axis_data_tdata_3;

wire [16:0]s1;

wire [17:0]S;

wire [39:0]m_axis_data_tdata_fir;

bandpass_top u1(.clk(clk),. m_axis_data_tvalid( m_axis_data_tvalid),.m_axis_data_tdata_1(m_axis_data_tdata_1),.m_axis_data_tdata_2(m_axis_data_tdata_2),.m_axis_data_tdata_3(m_axis_data_tdata_3),

.s1(s1),.S(S),.s_axis_data_tvalid(s_axis_data_tvalid),.m_axis_data_tdata_fir(m_axis_data_tdata_fir));

initial begin

clk<=1'b0;

s_axis_data_tvalid<=1'b1;

m_axis_data_tvalid<=1'b1;

end

always #5 clk<=~clk;

endmodule