IC设计中的功耗分析的流程

首先声明本文所讲的范围,在这篇文章中,是采用synopsys的设计流程,对数字电路进行功耗分析,生成功耗分析报告的流程。分析的对象是逻辑综合之后布局布线之前的功耗分析,以及布局布线之后的功耗分析。

Synopsys做功耗分析使用到的工具是:Primetime PX, PrimeRail。PTPX可以在逻辑综合之后就进行功耗预估。PrimeTimePX是集成在PrimeTime里面的工具,虽然他可以做功耗分析,但是毕竟不是sign-off工具。真正到最后的sign-off,如果对功耗的要求很高的话,依然要用PrimeRail进行分析,所以,我们只要用到PrimeTime PX来做功耗分析就够了。

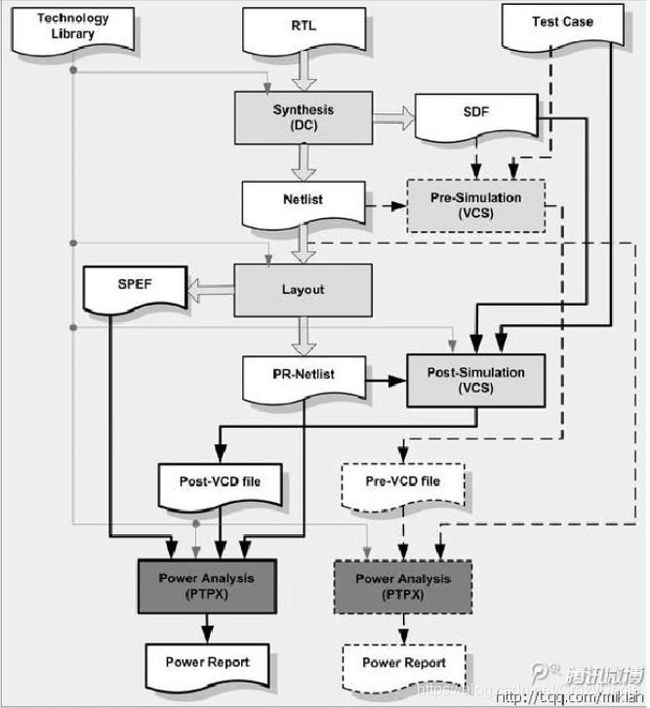

上图是布局布线后和逻辑综合后进行功耗分析的流程。

一. 逻辑综合后的功耗分析

所用到的文件有:

1. 逻辑综合后的verilog文件 2.静态时序分析时用到的约束文件 3.RTL的仿真文件,我用的是VCD,毕竟标准各个仿真器都支持~ 4.有功耗信息的库文件.db,这个库文件可以report一个库里的cell,看是否有。

有了这些文件之后,就可以做功耗分析了。下面说一下功耗分析的流程:

- 允许功耗分析功能 set power_enable_analysis

- 设置分析模式 setpower_analysis_mode。他的模式有两种,一种是average模式,不用仿真文件,另一种是time-based模式,是根据时序仿真文件来确定activityfactor。

- 读入设计和库文件

- 指定operating condition

- 时序分析 update_timing

- 获取activity data 如果是RTL级别的网表文件,要用-rtl来告诉pt之前指定的vcd file是布局布线之前的。如果VCD是zero_delay的仿真,也就是说是纯纯的functional

simulation的话,应该家用-zero_delay选项。如果都为指定,pt默认是gate-level。- 设置功耗分析选项 set_power_analysis_options :

-static_leakage_only option of the set_power_analysis_optionscommand is supported only in theaveraged power analysis mode.

-waveform_interval, -cycle_accurate_cycle_count,-cycle_accurate_clock,-waveform_format, - waveform_output, -include, and -include_groupsoptions are supported

only in the time- based poweranalysis mode.- 功耗分析 update_power

- 生成功耗分析报告 report_power

要说明的是,PTPX是primetime的一个增强功能,只用一个PT脚本就可以了,我把自己的pt脚本拿出来分享一下:

file: pt.tcl

###########################################

# Set the power analysis mode

###########################################

set power_enable_analysis true;

set power_analysis_mode averaged;

###########################################

# read and link the gatelevel netlist

###########################################

set search_path "../source db ./ ./result"

set link_library "typical.db"

set target_library "typical.db"

read_verilog jnd_90s.v

set top_name jnd

current_design JND

link

###########################################

# Read SDC and set transition time orannotate parasitics

###########################################

read_sdc pt_con.tcl

###########################################

# Check, update, or report timing

###########################################

check_timing

update_timing

report_timing

###########################################

# read switching activity file

###########################################

read_vcd -rtl jnd_all.vcd -strip_path testbench

report_switching_activity -list_not_annotated

###########################################

# check or update or report power

###########################################

check_power

update_power

report_power -hierarchy

二. 布局布线后的功耗分析

现在ptpx也支持多电压域的功耗分析,并提供了一个范例脚本,这里描述多时钟域时要用到UPF,叫unified powerformat。这里不介绍。

# Read libraries, design, enable power analysis

# and link design

set power_enable_analysis true

set link_library slow_pgpin.db

read_verilog power_pins.v

link

# Create back-up power nets

create_power_net_info vdd_backup -power

create_power_net_info vss_backup -gnd

# Create domain power nets

create_power_net_info t_vdd -power -switchable \

-nominal_voltages{1.2} -voltage_ranges{1.1 1.3}

create_power_net_info a_vdd -power

create_power_net_info b_vdd -power

# Create domain ground nets

create_power_net_info t_vss -gnd

create_power_net_info a_vss -gnd

create_power_net_info b_vss -gnd

# Create internal power nets

create_power_net_info int_vdd_1 -power \

-nominal_voltages{1.2} -voltage_ranges[1.1 1.3} \

-switchable

create_power_net_info int_vdd_2 -power \

-nominal_voltages{1.25} -voltage_ranges{1.1 1.3}

create_power_net_info int_vdd_3 -power \

-nominal_voltages{1.2} -voltage_ranges{1.1 1.3}

create_power_net_info int_vdd_4 -power

# Create power domains

create_power_domain t

create_power_domain a -object_list[get_cells PD0_inst]\

-power_down -power_down_ctrl[get_nets a] \

-power_down_ctrl_sense 0

create_power_domain b -object_list [get_cells PD1_inst]\

-power_down

# Connect rails to power domains

connect_power_domain t -primary_power_net t_vdd \

-primary_ground_net t_vss

connect_power_domain a -primary_power_net a_vdd \

-primary_ground_net a_vss \

-backup_power_net vdd_backup \

-backup_ground_net vss_backup

connect_power_domain b -primary_power_net b_vdd \

-primary_ground_net b_vss

# Set voltages of power nets

set_voltage 1.15 -object_list{t_vdd a_vdd b_vdd}

# Read SDC and other timing or power assertions

set_input_transition 0.0395 [all_inputs]

set_load 1.0 [all outputs]

# Perform timing analysis

update_timing

# Read switching activity

set_switching_activity...

set_switching_activity...

...

report_power

三. 关于报告

一个标准的报告:

Power Group Power Power Power Power ( %) Attrs

---------------------------------------------------------------

io_pad 0.0000 0.0000 0.0000 0.0000 ( 0.00%)

memory 0.0000 0.0000 0.0000 0.0000 ( 0.00%)

black_box 0.0000 0.0000 0.0000 0.0000 ( 0.00%)

clock_network 0.0000 0.0000 0.0000 0.0000 ( 0.00%)

register 8.442e-05 1.114e-05 9.208e-09 9.557e-05 (29.97%)i

combinational 0.0000 0.0000 0.0000 0.0000 ( 0.00%)

sequential 0.0000 0.0000 0.0000 0.0000 ( 0.00%)

Attributes

----------

i - Including driven register power

Internal Switching Leakage Total Clock

Power Power Power Power ( %) Attrs

---------------------------------------------------------------

clk 1.813e-04 4.199e-05 4.129e-10 2.233e-04

---------------------------------------------------------------

Estimated Clock1.813e-04 4.199e-054.129e-102.233e-04(70.03%)

Net Switching Power = 5.313e-05 (16.66%)

Cell Internal Power = 2.657e-04 (83.33%)

Cell Leakage Power = 9.627e-09 ( 0.00%)

---------

Total Power = 3.188e-04 (100.00%)

关于门控时钟的报告:

report_clock_gate_savings

****************************************

Report : Clock Gate Savings

power_mode: Averaged

Design : mydesign

Version: D-2009.12

Date : Thu Oct 29 12:08:20 2009

****************************************

------------------------------------------------------------------

Clock: clk

+ Clock Toggle Rate: 0.392157

+ Number of Registers: 19262

+ Number of Clock Gates: 12

+ Average Clock Toggle Rate at Registers: 0.305872

+ Average Toggle Savings at Registers: 22.0%

------------------------------------------------------------------

Toggle Savings Number of % of

Distribution Registers Registers

------------------------------------------------------------------

100% 0 0.0%

80% - 100% 76 0.4%

60% - 80% 5660 29.4%

40% - 60% 0 0.0%

20% - 40% 8 0.0%

0% - 20% 0 0.0%

0% 13518 70.2%

------------------------------------------------------------------