3.5 双端口RAM和多模块存储器

为了提高CPU访问存储器的速度,可以采用双端口存储器,多模式存储器等技术,他们都属于并行技术,前者为空间并行,后者是时间并行。

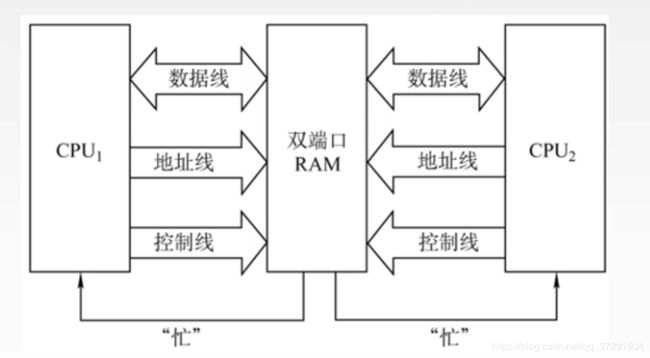

双端口RAM

双端口RAM是同一个存储器有左,右两个独立的端口,两组相互独立的地址线,数据线和读写控制线,允许两个独立的控制器同时异步地访问存储单元。但两个端口同时存取存储器的同一地址单元时,会因数据冲突造成数据存储或读取错误。两个端口对同一主存操作有4种情况。

1> 两个端口不同时对同一地址单元存取数据。

2> 两个端口同时对同一地址单元读出数据。

3> 两个端口同时对同一地址单元写入数据。

4> 两个端口同时对同一地址单元操作,一个写入数据,一个读出数据。

1,2种情况不会出现错误,3会出现写入错误,4会出现读出错误

解决方法是可以设置一个“忙”信号0,暂时关闭一个端口。

多模块存储器

多模块存储器,常用的有单体多字存储器和多体低位交叉存储器

1> 单体多字存储器

单体多存储器只有一个存储体,每个存储单元存储m个字,总线宽度也为m个字。一次并行读出m个字,地址必须顺序排列并处于同一存储单元。

缺点:指令和数据在主存内必须是连续存放的,一旦遇到转移指令,或操作数不能连续存放,这种方法的效果就不明显。

多体并行存储器

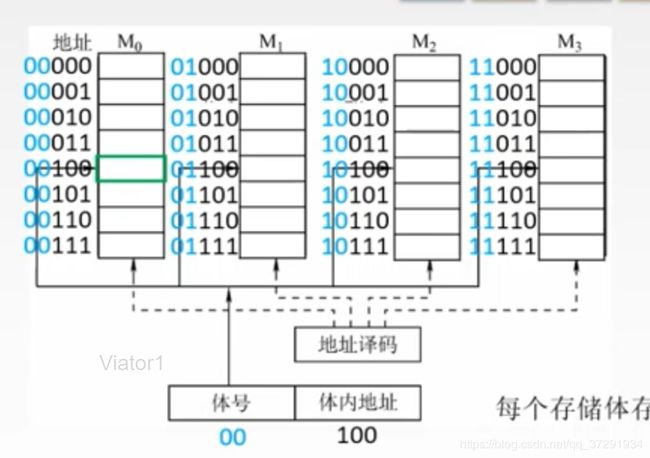

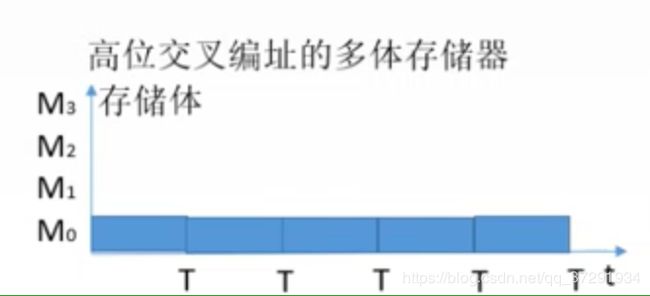

1> 高位交叉编址

高位地址表示体号,低位地址为体内地址

此编址仍是顺序存储器时间不变,只是扩大了容量。

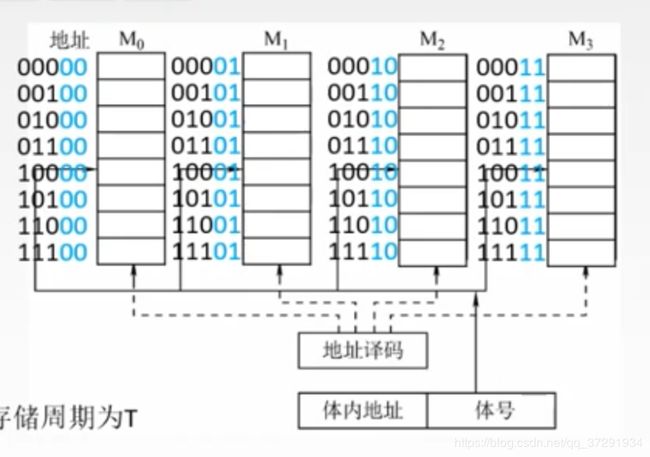

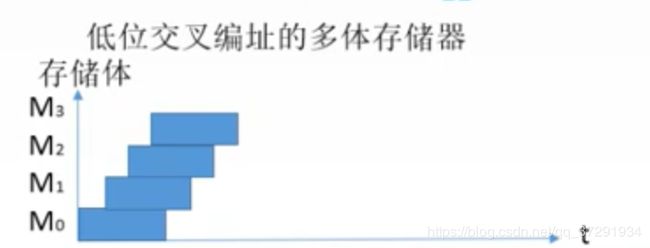

2> 低位交叉编址

采用流水线的方式并行存取,提高存储器的带宽

设模块字长对于数据总线的宽度,模块存取一个字的存取周期为T,总线传送周期为r,为实现流水线方式存取,存储器交叉模块数应大于等于 ![]() ,m称为交叉存取度。

,m称为交叉存取度。

连续存取m个字所需的时间 ![]() ,顺序方式连续读取m个字所需的时间为

,顺序方式连续读取m个字所需的时间为![]() 。

。