SoC中异步复位同步释放问题

1.同步复位和异步复位比较

大多数采用FPGA和ASIC的电路设计都是使用大量触发器或寄存器的同步系统。 这些同步元件能够启动或返回到已知状态(逻辑“ 1”或“ 0”)通常很重要。 此功能通常由复位处理。 通常有一个或多个复位信号被带入设备并单独使用或与其他电路配合使用以执行此功能。

同步电路通常通过两种类型的复位之一复位。 同步或异步复位。

我们讨论异步复位同步释放的复位方法,结合了两者的优点。

同步复位:

同步复位基于这样的前提,即复位信号仅会在该寄存器的时钟信号有效沿上影响该寄存器的状态。 同步复位的优势在于,它们通常可确保电路100%同步。 它们还具有可以通过静态时序分析工具轻松进行时序分析的优势。 由于复位信号是通过彼此同步的时钟启动和锁存的,因此可以轻松确定数据到达时间和所需数据时间,以进行适当的延迟分析。 同步复位的另一个优点是,在使用基于周期的仿真器时,它们可以更轻松地使用。

但是,同步复位确实有其缺点。 例如,它们可能需要脉冲展宽器以确保复位脉冲宽度足够宽,以确保在时钟的有效沿期间存在复位。 也许甚至更重要的是,这些复位需要一个时钟才能复位电路。 如果由于某种原因导致启动时钟发生故障,则产生的电路将无法复位。

常见的同步复位:

通过使用数据输入进行门控(参见图1)

异步复位:

长期以来,异步复位一直是电路设计中最常用的复位形式。 先有一个异步复位进入设备,然后放入一个全局缓冲区,然后连接到设备中每个(或几乎每个)寄存器的异步复位引脚,这是非常普遍的。

异步复位的最大优点之一是,它们不像同步复位那样插入数据路径。 因此,它们不会对寄存器之间的数据到达时间产生负面影响。 另一个优点是它们基本上立即生效。 一旦寄存器获得复位脉冲,无论相对于时钟的时序关系如何,寄存器都将复位。 它不像同步复位一样依赖于时钟。

异步复位没有任何问题。 但是,当释放复位时也可能会出现问题,也称为“复位移除(reset removal)”。 取消复位后,它必须满足寄存器的setup和hold time时间,才能保证数据正确。否则有亚稳态可能。

当复位信号无效时,并且未通过恢复或移除时间检查,则边缘被认为落在亚稳区内,如上面的图11所示。 这样的结果是增加了寄存器输出稳定到正确状态所花费的时间(基于输入到寄存器的数据)。 此额外的延迟可能导致下游的寄存器建立时间失败,从而导致系统故障。 显然,应不惜一切代价避免这种情况。

避免这种情况的一种方法是在具有异步复位的寄存器之后添加几个跟随器寄存器,并在设计中使用这些寄存器的输出。 从动寄存器以消除亚稳性问题的方式使数据与时钟同步。 这些寄存器在设备中可以放置得越近,越能使路由延迟最小,从而减少数据到达时间并增加MTBF。 请注意,重要的是,这些跟随器寄存器本身不要复位,而是通过“刷新”其当前状态或初始状态在几个时钟周期内初始化。 下面的图12显示了该电路的原理图示例。

通常,对于没有反馈电路的初始化这样的没有反馈电路的流水线设计,当设计在退出复位后可以等待几个周期再开始操作时,这种复位是可以接受的。

等效的Verilog代码显示在下面的图13中。 请注意,这与同步重置代码有何不同。 现在,复位的有效沿在程序块的灵敏度列表中。 同样重要的是,跟随器寄存器不在第一个程序块的“其他”部分中,因为这将推断出跟随器寄存器上的时钟使能,而复位信号的反相与时钟使能相关。 跟随器寄存器应位于单独的程序块中,如使用非阻塞分配所示。

图13:带有跟随器寄存器的异步复位的Verilog代码

约束异步复位很简单。 根据定义,异步复位与其正在复位的寄存器的时钟域具有不确定的关系。 因此,无法对这些复位进行静态时序分析。 通常使用set_false_path语句剪切它们(如图14底部所示)。 由于不知道寄存器中复位与时钟之间的关系,因此无法在TimeQuest中为此路径运行恢复和删除分析。 尝试这样做将不会报告任何路径。 即使没有错误的路径声明切入该路径,也不会报告要恢复和删除的路径。

除了异步复位可能带来的亚稳态问题外,另一个问题是它们对噪声的敏感性。 嘈杂的异步复位可能导致虚假复位。 因此,对异步复位进行去抖动和过滤非常重要。 如前所述,同步复位不太容易受到此问题的影响(尽管不是免疫的),因为它们是由时钟记录的。 在下一节“同步异步复位”中,讨论了完全避免此问题的方法。

异步重置的最大问题也许又与reset removal有关。 除了潜在的亚稳态问题外,由于器件内的寄存器放置和布线,不能保证与复位连接的每个寄存器与时钟的时序关系相同。 这样做的结果是,在给定的时钟周期内,某些寄存器将退出复位状态,而另一些寄存器直到下一个时钟周期才复位。 这可能会对反馈电路造成灾难性影响,其中一个寄存器的下一个输出取决于其他寄存器的当前输出。 一个常见的例子是状态机。 one hot状态机特别有问题,因为一次只设置一个状态位。 如果某个状态位由于复位而退出,而不是其他状态位,则状态位高,则该状态机可能会进入非法状态。[幸运的是,现在可用的综合设置之一称为“安全状态机”, 从非法状态中恢复。 但是,此设置默认情况下为OFF,必须将其设置为ON才能生效。]对于二进制编码状态机,可以为未使用的状态创建返回到复位状态的转换,这使其成为确定性状态机。 这将允许从非法或未使用状态正常恢复。

---------------------------------------------------------------------------------------------------------------下面是异步复位同步释放--------------------

同步异步复位为了避免与纯同步复位和纯异步复位相关的某些问题,可以使用第三类复位,称为同步异步复位。 这些复位结合了异步复位的优势(几乎不涉及数据路径的速度和几乎立即生效)和同步复位的优势(对于时序分析和抗噪声性能为100%同步)。 这些复位通过异步声明和同步取消声明以实现这些目标。 如前所述,异步进行复位是可以的,但异步进行复位会导致潜在的亚稳性问题,以及涉及反馈的同步电路会带来有害情况。

下面讨论实现这些重置的一些方法。 图15所示的电路使用同步寄存器的方式与同步复位类似,但是异步复位与寄存器的输出进行门控,以异步方式声明所产生的复位。 该电路将异步置位复位并异步取消置位。 然而,其缺点在于,在所产生的复位路径中将存在门延迟。

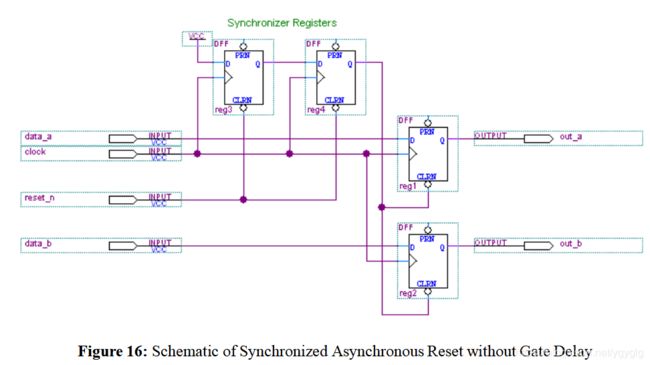

图16显示了一种更好的实现方法。这使门控延迟脱离了产生的复位路径。 异步复位输入直接连接到同步器寄存器的CLRN引脚,从而立即声明复位结果。 当复位无效时,通过同步器输出逻辑“ 1”,以同步使无效复位无效。

等效的Verilog代码在下面的图17中显示。第一个过程块创建同步的重置rst_n,然后它成为第二个过程块的异步重置。 在这两个模块中,灵敏度列表中都使用了复位的有效沿。

图17:用于同步异步复位的Verilog代码

结果表明,对两个路径(reg4到reg1和reg4到reg2)都进行了恢复和删除检查。 在此示例中,恢复时间检查(类似于设置时间检查)的松弛时间接近9 ns,而移除时间检查(类似于保持时间检查)的松弛时间少于1 ns。 两项检查均通过,并且在此示例设计中没有失败的路径。

瞬时断言同步异步复位所付出的代价之一是,它们容易受到噪声和欠幅脉冲的影响。 同样,如果可能,异步复位应在进入设备之前进行去抖动和过滤。 图16中的电路保证了同步异步复位的长度至少为一个完整的时钟周期。 为了将此时间延长至n个时钟周期,请将同步寄存器的数量增加到n +1。确保将异步输入reset reset_n连接到所有同步寄存器的CLRN引脚,以保持同步的异步断言。 异步复位。

当涉及PLL时钟时,需要特别考虑。 考虑上面图19中的电路。 同步复位像以前一样连接到寄存器reg1和reg2的CLRN,并且还连接到PLL的areset引脚。 用于为所有寄存器(包括同步器寄存器)提供时钟的时钟是PLL的输出时钟。 虽然将同步复位用于PLL似乎很有意义,但这实际上是行不通的。 当PLL复位时,c0输出没有时钟输出,因此同步器寄存器将无法清除复位。 结果,该电路将永远不会复位!

图20:使用PLL正确实现同步异步复位的示意图

要解决此问题,应使用输入reset_n(在这种情况下为反相)而不是同步复位来复位PLL的复位。 另外,优良作法是将PLL的锁定输出用作同步器寄存器的时钟使能。 这样可以防止同步复位在PLL时钟稳定之前消失。

此原理图的Verilog等效图如图21所示。

请注意,同步器寄存器的程序块现在具有锁定信号的条件,该条件会合成为寄存器的时钟使能。 还要注意靠近底部的PLL实例,第二个程序块的时钟现在是PLL的输出时钟pll_clk。 这些是向电路添加PLL时所需的唯一更改。

图22所示的时序约束与不带PLL的时序约束类似,不同之处在于,现在必须为PLL输出时钟添加create_Generated_clock语句。[请注意,本示例以及本文档示例中使用的所有SDC约束, 为简单起见,仅限制了输入和内部。]

还有另一种情况值得一提。 如前所述,要求寄存器复位的设计中的每个时钟域都应具有自己的一组同步器寄存器。 有时可能有必要先释放设计的不同部分,然后再进行复位。

在有序清除复位的情况下,可以按以下所示方式链接同步器寄存器,最高优先级的复位在顶部,最先出现。 在下面的图23中,所有复位都同时声明,但是rst_a_n是最高优先级,首先退出复位,其次是rst_b_n,处于中等优先级,最后是rst_c_n最后退出复位。 当然,如果在两次复位之间需要更长的时间,则可以将同步器中的寄存器数量增加到任意长度。

图23:优先清除同步器寄存器的复位

---------------------------------------------------------总结---------------------------------------------------------

本技术说明描述了各种类型的复位的优缺点:同步,异步和同步异步。

同步复位需要一个时钟,因此可能会错过短的复位脉冲。 但是,这也使它们具有更好的抗噪性。 它们是100%同步的,因此亚稳定不是问题,但是它们会消耗额外的资源并增加数据路径的延迟。 因此,同步复位通常不是最佳选择。 像其他任何数据路径一样,在TimeQuest中对同步重置进行计时。

异步复位是立即的,易于实现的,并且是最快的,因为它们不涉及数据路径。 它们还消耗最少的资源。 不幸的是,它们不能在TimeQuest(或任何其他静态时序分析器)中时序分析,如果处理不当,可能导致亚稳性问题。 异步复位的最大缺点是它们不能保证所有寄存器都将在同一时钟沿退出复位。 这对于带有反馈的同步设计(例如状态机)是有问题的。

在将复位器添加到寄存器的异步输入之前,将同步器添加到复位会创建同步的异步复位。 由于不涉及数据路径,这些复位提供了异步复位的即时断言优势,并提高了速度。 它们还避免了亚稳性问题,并且将确保所有寄存器都在与同步复位相同的时钟沿上退出复位。 与异步重置不同,可以使用恢复和删除分析在TimeQuest中对它们进行计时。 由于这些原因,对于大多数FPGA设计而言,同步异步复位通常是首选的使用方法。