AD7760转换原理及采集程序设计 (24位Σ-Δ型ADC)

1 AD7760(Σ-Δ模数转换器)

1.1 Σ-Δ型ADC的工作原理

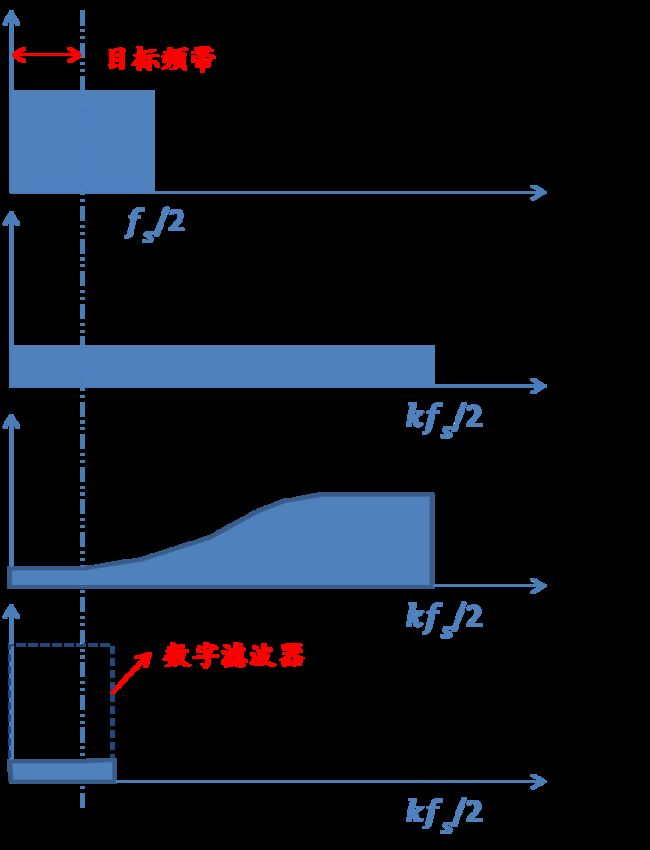

的ADC不同,Σ-Δ型ADC不是直接根据采样数据的每一个样值的大小进行量化编码,而是根据前一量值与后一量值的差值即所谓的增量的大小来进行量化编码,Σ-Δ调制器以极高的采样频率( k f s kf_s kfs)对输入模拟信号进行采样,并对两个抽样之间的差值进行低位量化(通常为1bit),从而得到用低位数码表示的数字信号即Σ-Δ码,由于Σ-Δ调制器具有极高的采样速率(与 C L K CLK CLK相关),通常比奈奎斯特采样频率高出许多倍,因此Σ-Δ调制器又称为过采样ADC转换器;之后将Σ-Δ码送给第二部分的数字抽取滤波器进行抽取滤波,以频率输出N位数字信号,从而得到高分辨率的线性脉冲编码调制的数字信号,因此抽取滤波器实际上相当于一个码型变换器。

调制器输出中“1”的密度正比于输入信号,如果输入电压上升,比较器将产生更多数量的"1",反之亦然。积分器对于输入信号表现为低通滤波器,而对于量化噪声则表现为高通滤波。这样,大部分量化噪声就被推向更高的频段,实现噪声整形。通过数字滤波器则可滤除目标频段外的大部分噪声,从而提高了信噪比。

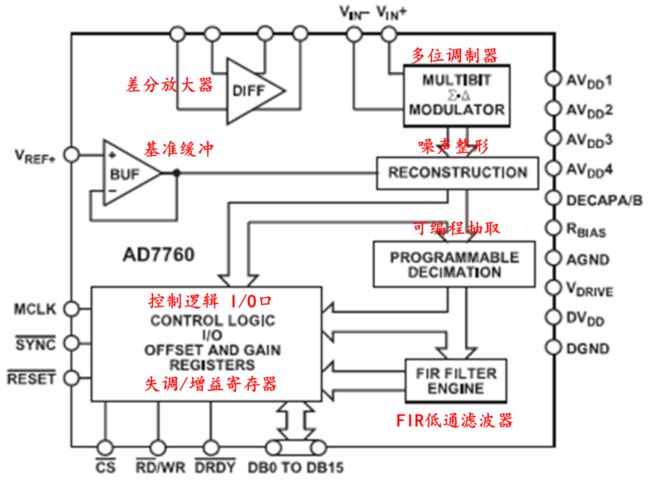

1.2 AD7760功能框图

AD7760采用Σ-Δ转换技术将模拟信号转换为等效的数字串流。采用与ICLK等效的速率向滤波器输出等效数字串流。该技术将噪声扩展到0~频段,并且将大部分噪声能量移出目标频段之后采用三个串联的数字滤波器实现可编程抽取以及噪声滤除。

1.3 转换时序

要从AD读取一个转换结果,需进行两次16位读操作,如图1.5所示,每次有新的转换结果,DRDY引脚上输出一个低电平有效脉冲,随后严格按给定时序先将nRD/WR置低,然后将nCS置低,在其均变为低电平不久,数据总线将为有效状态,然后输出高16位有效位,保持一定时间的低电平后先将nCS电平置高,再将nRD/WR电平置高,则完成一次16读操作,高电平需至少保持一个完整的ICLK周期才能进行第二次低16位有效位的读取。

当nCS为低电平,nRD/WR为高电平时为AD7760寄存器写操作,寄存器写入顺序为先写地址,再写寄存器的值。

1.4 ADC传递函数

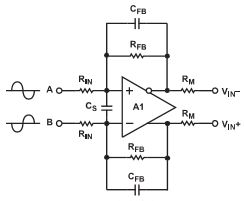

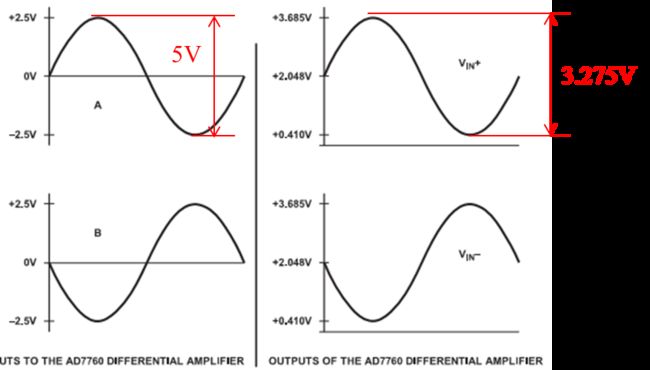

AD7760内部有个差分放大器使得使得输出电压始终偏置在的最佳共模电压上,当采用5V供电时,。另外由于构成反馈放大电路,且,因此输出信号的差值减小为3.275V,对应该电压基准下容许的最大电压摆幅:

为了得到满量程的输出,经过增益寄存器的放大使最大负值获得1倍的增益,即当输入为的80%,即最大模拟输入范围时,对应满量程数字输出。

另外,由于,因此会发现2.5V与正向满量程之间会差一点

根据上图可以得到传递函数表达式为:

V O U T = C o d e 2 23 × 4.09375 V × 0.8 × R I N R F B = C o d e 2 23 × 5 V ; ( R I N = 1 K Ω , R F B = 655 Ω ) V_{OUT}=\frac{Code}{2^{23}} \times\ 4.09375V \times\ 0.8 \times\ \frac{R_{IN}}{R_{FB}} =\frac{Code}{2^{23}} \times\ 5V; (R_{IN}=1K \Omega ,R_{FB}=655 \Omega ) VOUT=223Code× 4.09375V× 0.8× RFBRIN=223Code× 5V;(RIN=1KΩ,RFB=655Ω)

2 采集卡

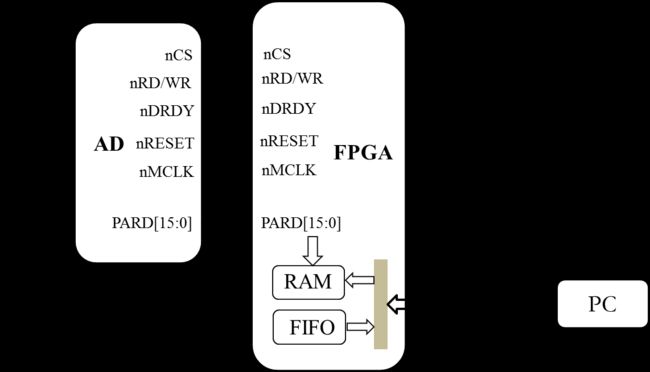

2.1 技术路线

2.2采集卡工作原理

上电后,采集卡进入复位状态,上位机发送任意8个字节命令(如FA FB

FC FD FE FF FF FF)后,采集卡首先按给定的地址写入四个寄存器的值,然后进入数据采集状态,先输出低16位有效位,再输出高16位有效位,并且都是低8位在前,高8为在后,其中低16位有效位的低8位为状态位;在此期间若再次发送8个字节命令,则采集卡停止采集,即奇数次命令为采集,偶数次命令为停止。

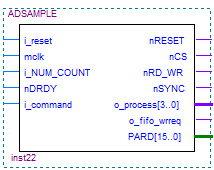

2.3 AD采集模块状态机

将AD采样模块的控制位(NUM_COUNT)置1,使其模块状态机进入“采样”状态,将NUM_COUNT置0,则停止采集。

Fifo模块采用异步通信,即读写时钟不同步,可以边采边发,每次有新数据传来,

wrreq就置为高电平,则fifo进行写操作;当采样数据量达到所设定的值时,将数据发送准备控制位置为有效,同时调用USB 数据发送模块,开始从fifo读取数据,当数据发送完成,将fifo的读使能置低,至此,完成一次数据的传输。

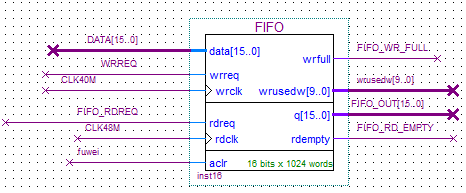

2.4 FIFO读写控制

2.4.1 FIFO写使能( WRREQ)

每次有新数据传来,则需将FIFO写使能WRREQ置为高电平,将数据写入FIFO。为了实现数据正确的读取,考虑有以下四种方法:

1) 根据nRD/WR的上升沿信号控制FIFO的读使能;

2) 根据nCS的上升沿信号控制FIFO的读使能;

3) 根据nCS的下降沿延时信号控制FIFO的读使能;

4) 根据nDRDY的下降沿延时信号控制FIFO的读使能;

由于两次数据的保持时间间隔不一致,若是采用nCS或者nRD/WR进行控制,会使得必有一次数据读取不准,而两次数据与nDRDY的时间间隔可以通过程序进行控制,因此采用nDRDY经过设定的延时进行FIFO读使能的控制。

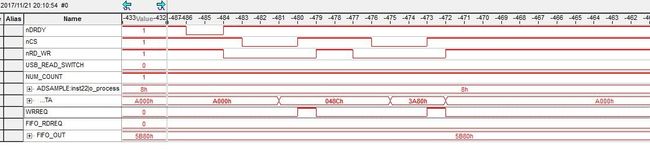

另外由下图可以看出,

NUM_COUNT为1时,一直在进行数据采集,当fifo数据量达到设定值,将USB_READ_SWITCH置为高电平,通过USB将数据发送至上位机。

2.4.2 读使能控制(RDREQ)

当USB准备发送数据,将RDREQ置为高电平,从FIFO读取数据,由下图可以看出, NUM_COUNT为1时,一直在进行数据采集,当fifo数据量达到设定值,USB_READ_SWITCH和FIFO_RDREQ置为高电平,通过USB将数据发送至上位机,待数据发送完成,将USB_READ_SWITCH和FIFO_RDREQ重新置为低电平。

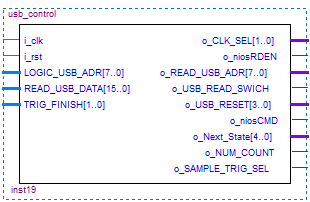

2.4 USB控制模块状态机

USB控制模块用于解析上位机命令,并检测相关状态位的变化,从而实现USB的读写操作。

2.5 信号采集测试

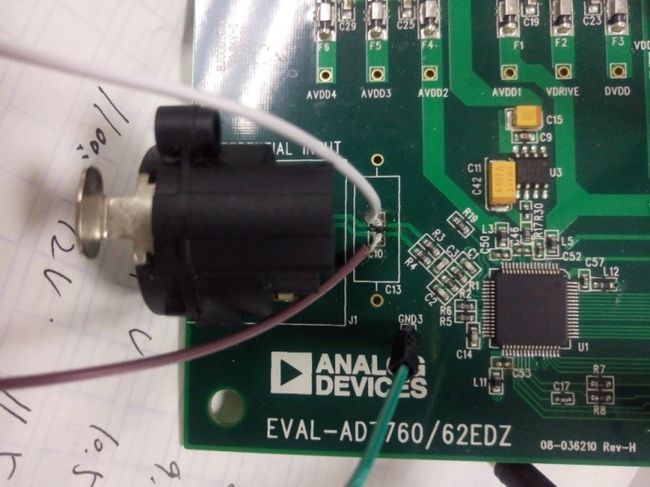

2.5.1 测试条件

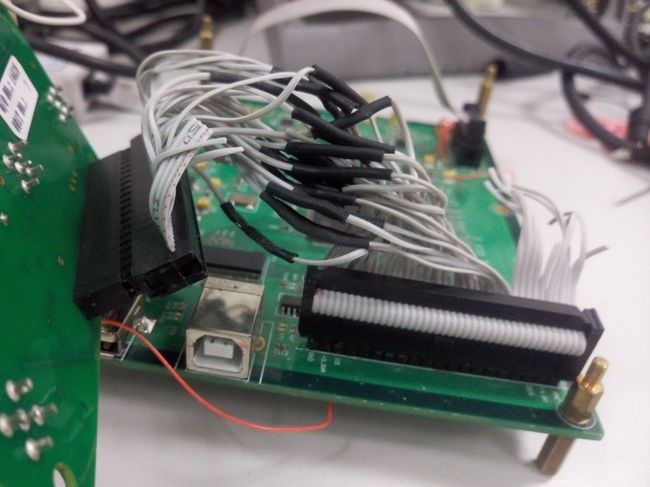

测试过程采用信号发生器,示波器以及220V转24V开关电源,信号通过BNC头从信号发生器输出,另一端直接焊在AD采集卡信号输入端。

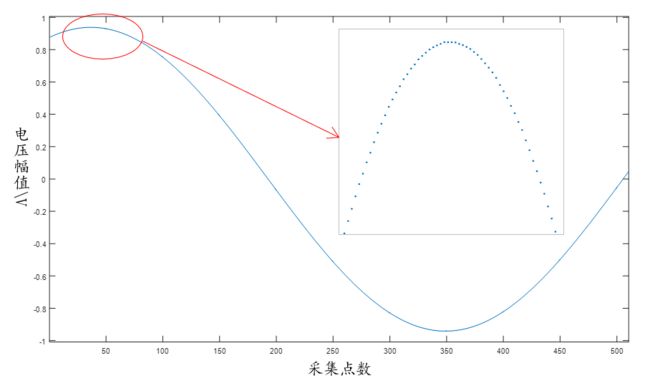

2.5.2 正弦信号采集

通过设置信号发生器,使两个通道分别输出相位差为180°的正弦波,峰-峰值为1V,频率为1KHz。(注:在计算出最后结果时将其除以了2,因此最后结果为输入信号差值的一半)

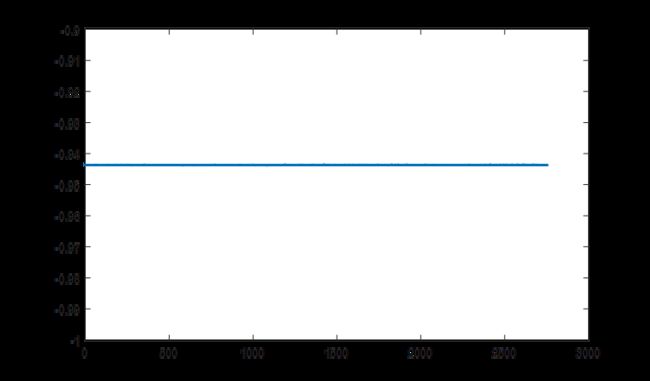

2.5.3 直流信号采集

通过信号发生器输出直流信号,由于信号从信号发生器到采集卡有一定压降。

将所得信号放大,可以得到其噪声及波动量,如下图所示。

通过示波器观测采集卡信号输入端的信号波形,发现输入信号本身的波动较大,对测试结果的影响不可避免。

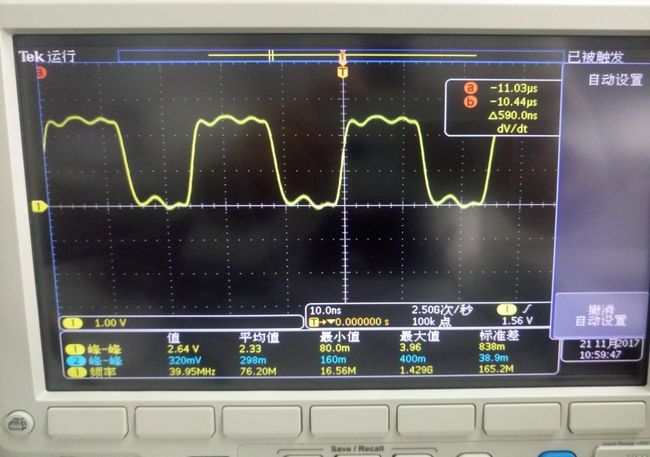

2.5.4 系统时钟

高速数据经过长的PCB线或者导线会因为介质损耗的影响而发生一定的畸变,AD采集卡采用的时钟为40M,通过插针和排线引出至FPGA板,分别测量AD采集卡与FPGA板排针处时钟的信号,得到如图2.19以及2.20所示的波形,可以发现通过该方式进行时钟信号的传输会使得信号发生较大畸变。

由于AD7760采用的Σ-Δ转换技术是根据前一量值与后一量值的差值大小来进行量化编码,并以极高的抽样频率对输入模拟信号进行抽样,然后对两个抽样之间的差值进行低位量化,而对于AD7760而言,其抽样频率是晶振产生时钟频率的1/2,因此采样时钟的畸变将直接影响到两个抽样之间的差值,从而影响到转换结果的精确度。

3 存在问题

- 由信号发生器输出至AD采集卡端口的信号存在较大压降,且信号波动较大,为了更好的进行实验和测试,应重新做信号输出线;

- 插排线两端存在较大压降,导致MCLK波形发生畸变,对于信号采集会存在一定的影响

- 目前采用双晶振进行工作,由AD板上的40M晶振为AD_SAMPLE模块提供时钟基准MCLK,其余模块的时钟基准由FPGA板上的50M晶振提供,此涉及跨时钟域的概念,信号采集模块与数据发送模块通过fifo异步传输作了缓冲,因此可在一定程度上避免亚稳态的产生,但由于这部分并未做深究,因此若是能解决问题2中MCLK信号由AD板传输至FPGA板波形发生畸变的问题,则尽量采用AD板上的晶振为整个系统提供时钟基准,以避免涉及到跨时钟域数据传输的问题。