FPGA入门实验四:时间基准电路 和 带使能的多周期计数器

1.根据参考代码,将计数器范围改为0~15,verilog 代码如下:

module CNT_EN(

input wire CLK,

input wire EN,

output reg [4-1:0] OUT,

output reg OV

);

always@ (posedge CLK)

begin

if(EN==1&&OUT<15)

OUT<=OUT+1'b1;

else if(EN==1&&OUT==15) OUT<=1'b0;

if(EN==0)

OUT<=OUT;

end

always @ (OUT)

begin

if(OUT==15)

OV<=1'b1;

else

OV<=1'b0;

end

endmodule

2.将0-15经过译码后,通过数码管显示0-9-F

i)查阅开发板原理图可知,数码管为共阳连接,低电平有效,进而得出0~F每个数字的段选码。

ii)将输入的0~15数字通过verliog编写译码成对应的段选码,其代码如下:

module sel4_16(

input wire [4-1:0] IN,

output reg [8-1:0] OUT

);

always @ (IN) begin

case (IN)

4'b0000:OUT=8'b11000000;

4'b0001:OUT=8'b11111001;

4'b0010:OUT=8'b10100100;

4'b0011:OUT=8'b10110000;

4'b0100:OUT=8'b10011001;

4'b0101:OUT=8'b10010010;

4'b0110:OUT=8'b10000010;

4'b0111:OUT=8'b11111000;

4'b1000:OUT=8'b10000000;

4'b1001:OUT=8'b10010000;

4'b1010:OUT=8'b10001000;

4'b1011:OUT=8'b10000011;

4'b1100:OUT=8'b11000110;

4'b1101:OUT=8'b10100001;

4'b1110:OUT=8'b10000110;

4'b1111:OUT=8'b10001110;

endcase

end

endmodule

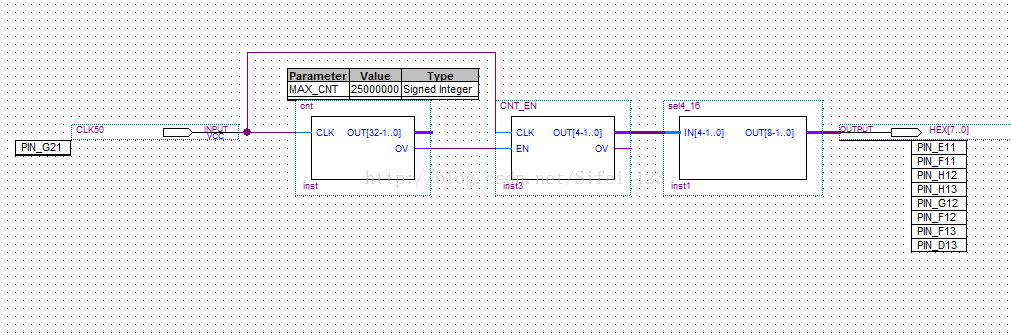

iii) 添加BDf文件,添加Symbol后指派数码管对应的引脚,完成后的Bdf如下

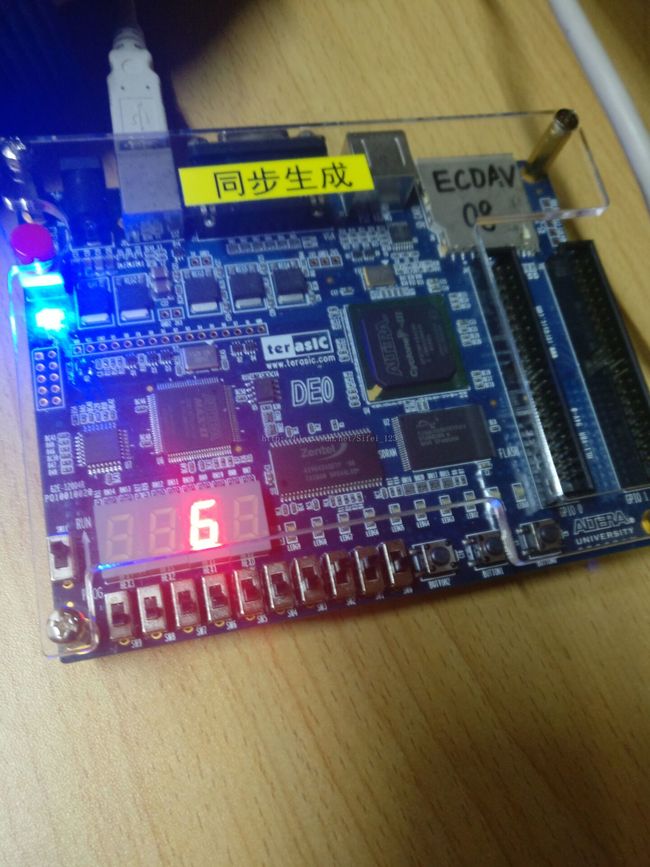

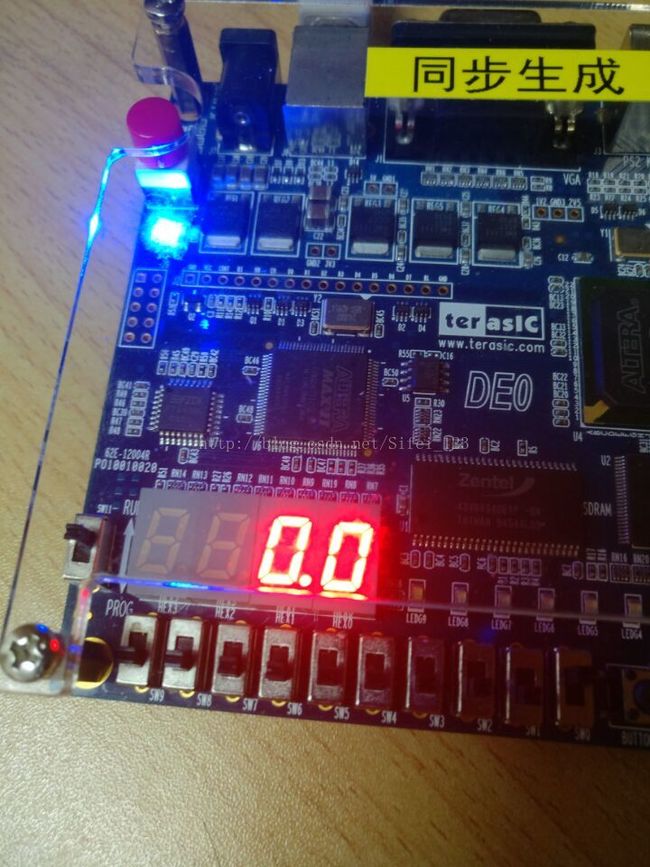

iv) 编译、下载,通过拨动拨码开关观察显示的数字,其结果如下图所示

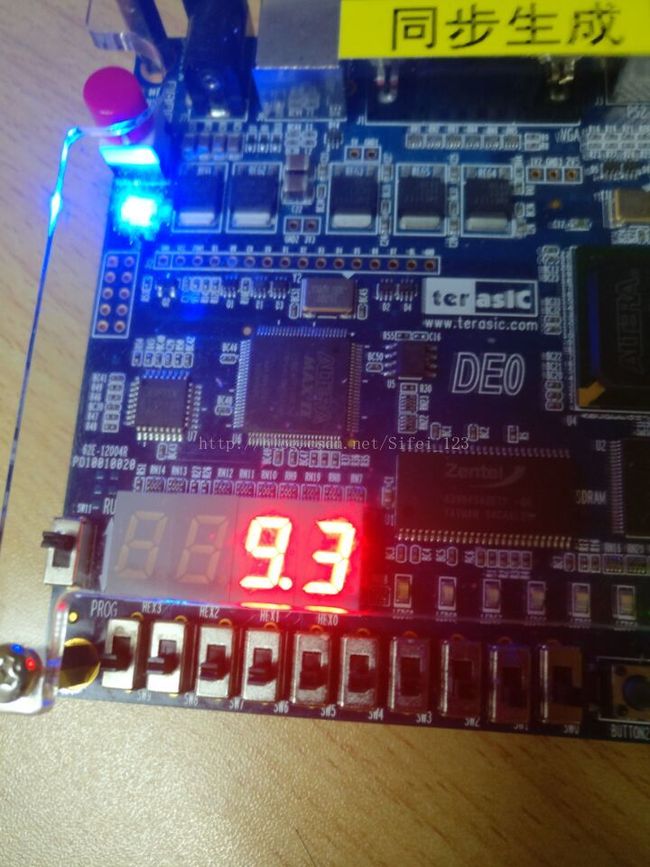

3.制作精度为0.1秒,范围为0-9.9秒的计时秒表,并且带清零、暂停功能。

i)需要创建的Symbol的verilog 文件代码如下

module cnt(

input CLK,

output reg [32-1:0] OUT,

output reg OV

);

parameter MAX_CNT=5000_000;

always @(posedge CLK)

begin

if(OUT

else

OUT<=0;

end

always @ (OUT)

begin

if(OUT==MAX_CNT)

OV<=1'b1;

else OV<=1'b0;

end

endmodule

module CNT_EN(

input wire CLK,

input wire EN,CLR,STOP,

output reg [4-1:0] OUT,

output reg OV

);

always@ (posedge CLK)

begin

if(CLR) OUT<=4'b0000;

else begin

if(!STOP) begin

if(EN==1&&OUT<10)

OUT<=OUT+1'b1;

else if(EN==1&&OUT==10) OUT<=1'b0;

if(EN==0)

OUT<=OUT;

end

else if(STOP) OUT<=OUT;

end

end

always @ (OUT)

begin

if(OUT==10)

OV<=1'b1;

else

OV<=1'b0;

end

endmodule

module sel4_16(

input wire [4-1:0] IN,

input wire EN,

output reg [8-1:0] OUT,

output reg [4-1:0] OV

);

always @ (IN) begin

case (IN)

4'b0000:OUT<=8'b11000000;

4'b0001:OUT<=8'b11111001;

4'b0010:OUT<=8'b10100100;

4'b0011:OUT<=8'b10110000;

4'b0100:OUT<=8'b10011001;

4'b0101:OUT<=8'b10010010;

4'b0110:OUT<=8'b10000010;

4'b0111:OUT<=8'b11111000;

4'b1000:OUT<=8'b10000000;

4'b1001:OUT<=8'b10010000;

endcase

end

always @ (posedge EN) begin

if(EN&&OV<10)

OV<=OV+1'b1;

if(!EN) OV<=OV;

if(OV==9&&EN) OV<=4'b0;

end

endmodule

module sel4_10(

input wire [4-1:0] IN,

input wire CLR,

output reg [8-1:0] OUT,

output reg OV

);

always @ (IN) begin

if(!CLR) begin

case (IN)

4'b0000:OUT<=8'b01000000;

4'b0001:OUT<=8'b01111001;

4'b0010:OUT<=8'b00100100;

4'b0011:OUT<=8'b00110000;

4'b0100:OUT<=8'b00011001;

4'b0101:OUT<=8'b00010010;

4'b0110:OUT<=8'b00000010;

4'b0111:OUT<=8'b01111000;

4'b1000:OUT<=8'b00000000;

4'b1001:OUT<=8'b00010000;

endcase

end

else OUT<=8'b01000000;

end

//always @ (IN) begin

// if(!IN) OV<=OV+1'b1;

// else OV<=OV;

//end

endmodule

ii) 建立Bdf文件,并指派管脚

iii)编译、下载后观察现象,并通过相应的拨码开关执行暂停、清零操作