用VHDL实现有限状态机

背景

在数字系统中,有两种基本类型的电路。第一类是组合逻辑电路。在组合逻辑电路中,输出仅依赖于输入。组合逻辑电路的例子包括加法器,编码器和多路复用器。例如,在加法器中,输出只是输入的总和; 无论以前的输入或输出是什么都没有关系。第二种类型的数字逻辑电路是时序逻辑电路。在顺序逻辑电路中,输出不仅取决于输入,还取决于系统的当前状态(即输出值和任何内部信号或变量)。顺序逻辑电路的复杂程度不同于简单的计数器,这些计数器以基本序列(例如,0,1,2,3 ... 0,1,2,3 ...)从一种状态移动到另一种状态,到超大规模电路(例如微处理器)本文的重点将放在顺序逻辑电路表示为有限状态机以及如何将这些有限状态机转换为硬件描述语言VHDL。

顺序逻辑系统是有限状态机(FSM)。作为FSM,它们由一组状态,一些输入,一些输出以及一组从状态到状态的规则组成。在进行数字系统设计时,从定义系统如何与有限状态机模型一起工作开始非常常见。这一设计步骤允许设计人员从高级角度考虑设计,而不必考虑系统将实施什么样的硬件或实施设计需要哪些设计工具。一旦完全设计FSM,如果设计良好,则很容易用硬件描述语言(例如Verilog或VHDL)写出设计,以便在数字IC(集成电路)上实现。

本文将通过首先定义设计问题来完成创建数字系统的设计过程,其次,将系统的计算模型创建为有限状态机,然后将FSM转换为硬件描述语言VHDL。(VHDL实际上是双重缩写词,VHDL代表VHSIC硬件描述语言,VHSIC代表甚高速集成电路)。

读者应该有一些数字电路和IC的经验。他们还应该对VHDL有基本的了解,或者至少有一些阅读结构化计算机代码的经验。使用计算机代码的经验将帮助你认识到VHDL的一些结构和结构,但应该指出的是,VHDL不是一种编程语言; 它是一种硬件描述语言(HDL)。换句话说,您所编写的语句将在您正在设计的系统中创建硬件(门,触发器等)。

有限状态机

要设计的系统是一个非常简单的系统,其目的是引入将FSM转换为VHDL的想法。此FSM具有四个状态:A,B,C,和d。该系统具有被称为一个输入信号P,和的值P确定什么状态系统移动到下一个。只要输入P为高电平(1),系统就会将状态从A更改为B至C至D. 如果P低,并且系统处于状态A,B或C,则状态不会改变。如果系统处于状态d,则切换到乙如果P高和一,如果P低。系统还有一个称为R的输出,如果处于状态D,则该输出为1 ,否则它是0.图1是FSM的示意图,但首先这里是关于此图的一些注释:

- 圆圈代表状态

- 圆圈之间的箭头代表从状态变为状态的规则。例如,在这个系统中,如果输入P等于1(否则它保持在状态A),状态机从状态A移到状态B,

- 圆圈下方的信息代表每种状态下的输出值。

- 从“无处”到A的箭头表示A是初始状态。

图1.简单的有限状态机

这个完全定义的状态机可以很容易地转换为VHDL。请记住,在编写VHDL代码时,您正在做的是描述如何实现硬件(即数字门)。因此,例如,当您在此系统中定义一组状态(如A,B,C和D)时,这些状态将由位来表示,更具体地由触发器的输出表示。在一个有四个状态的系统中,就像这个状态一样,可以用2个位来表示这四个状态(2个触发器)。还有其他方式可以代表国家。其中一种方法是使用四位,其中每一位表示一个状态,但一次只能打开一位。所以A将由0001表示,B乘以0010,C乘以0100,D乘以1000.使用高级硬件描述语言的好处之一是,您通常可以忽略这一级别的细节。

图2显示了在将VHDL代码合成为创建硬件时将创建的硬件电路的总体思路。

图2.为状态机创建的逻辑的框图表示

此图表明,有一组Ñ触发器表示的状态。还有一些逻辑使用触发器的输出和系统的输入来确定下一个状态。最后,有一些逻辑解码触发器的输出值来创建m个输出信号。

同样,在使用HDL时,您通常可以忽略设计中的这一级别细节。了解HDL创建什么样的电路仍然很重要,因为可能会有一段时间您必须计算并最小化设计中的逻辑门数。了解您的HDL声明创建的内容后,您可以设计最大限度地减少大门的创建。

VHDL设计实现

编写此FSM的VHDL的第一步是定义VHDL实体。VHDL实体描述了您正在设计的系统的外部接口,其中包括输入,输出和实体名称。实体名称将为SimpleFSM,输入为时钟信号,复位信号和P信号,输出为R信号。应该提到的是,时钟信号是周期性的高低电平信号,它控制着这个同步系统的定时。任何同步系统都有一个控制时钟信号,用于同步系统中的所有模块,使它们同时发生变化。

把所有的信息放在一起给出一个看起来像这样的SimpleFSM实体:

ENTITY SimpleFSM is -- SimpleFSM实体定义

PORT (clock: IN STD_LOGIC;

P: IN STD_LOGIC;

reset: IN STD_LOGIC;

R : OUT STD_LOGIC);

END SimpleFSM;

关于实体的最后一点是所有的输入和输出都是单个位,所以可以使用数据类型std_logic,它是VHDL中的标准类型,用于单位信号。

下一步是定义实体的功能; 这块VHDL被称为体系结构。我们正在实现的功能是图1中定义的状态机的功能。下面的示例显示了实现SimpleFSM所需的代码。虽然这段代码是特定于SimpleFSM的,但我会描述代码中的每一部分,以便将代码替换为您自己的状态机的代码是一个简单的过程。

Architecture RTL of SimpleFSM is

TYPE State_type IS (A, B, C, D); -- 定义状态

SIGNAL State : State_Type; -- 创建信号

-- 不同状态

BEGIN

PROCESS (clock, reset)

BEGIN

If (reset = ‘1’) THEN -- 复位reset,复位状态为A

State <= A;

ELSIF rising_edge(clock) THEN

-- clock上升沿触发状态转变

CASE State IS

-- If the current state is A and P is set to 1, then the

-- next state is B

WHEN A =>

IF P='1' THEN

State <= B;

END IF;

-- If the current state is B and P is set to 1, then the

-- next state is C

WHEN B =>

IF P='1' THEN

State <= C;

END IF;

-- If the current state is C and P is set to 1, then the

-- next state is D

WHEN C =>

IF P='1' THEN

State <= D;

END IF;

-- If the current state is D and P is set to 1, then the

-- next state is B.

-- If the current state is D and P is set to 0, then the

-- next state is A.

WHEN D=>

IF P='1' THEN

State <= B;

ELSE

State <= A;

END IF;

WHEN others =>

State <= A;

END CASE;

END IF;

END PROCESS;

R <= ‘1’ WHEN State=D ELSE ‘0’;

END rtl;

这是状态机所需的全部代码。现在我们来看看架构代码的一些细节。

架构定义指出:

Architecture RTL of SimpleFSM is

该语句是VHDL体系结构的标准语句,它基本上说明了体系结构中将要描述的抽象级别。代表寄存器传输级别的RTL是抽象的中间级别。

行为 是最高级别的抽象,在编写行为代码时,您只需要定义输入和输出之间的关系,而不指定如何实现这些关系。有时行为描述太高而不能实际合成硬件。如果你正在做一个模拟,只需要一个块以某种方式行事,那么行为模型就足够了。

结构 代码是最低级别的抽象。在编写结构代码时,您将描述低层结构(如逻辑门)如何连接在一起以提供所需的系统。如果您需要对将要创建的逻辑门进行精确控制,那么您需要一个结构模型。

RTL适合在中间。它具体描述输入和输出之间的关系,描述数据如何在硬件寄存器之间移动。RTL描述可用硬件实现。对于这个特定的例子,了解体系结构类型(行为,RTL或结构)的细微差别并不是很重要,你只需要将它定义为某种东西。

下一个块定义状态并创建一个将定义状态作为其值的信号。在这里列出的状态应该与FSM图中由圆圈表示的状态一一对应。

TYPE State_type IS (A, B, C, D); -- the 4 different states

SIGNAL State : State_Type; -- Create a signal that uses

-- the 4 different states

下一条语句是在其灵敏度列表中使用信号时钟和复位的VHDL过程的开始

PROCESS (clock, reset)

BEGIN

If (reset = ‘1’) THEN -- Upon reset, set the state to A

State <= A;

ELSIF rising_edge(clock) THEN

同样,关于流程声明的许多细节可以在本文中被忽略。所有你需要了解的是,在RTL级设计中,这个过程将创建一个寄存器,用于在过程中为它们分配的所有信号。在这种情况下,只有状态信号具有分配,因此将创建由足够的触发器组成的用于表示状态值的寄存器。该寄存器将被同步到时钟的上升沿,并可通过复位信号进行异步复位。在图2中可以看到由该过程创建的电路的一般视觉表示。

rising_edge(clock)语句后面的代码体是一个VHDL case语句,它将被合成为逻辑,用于控制在时钟的每个上升沿上State变化的值。例如,声明

WHEN A =>

IF P='1' THEN

State <= B;

END IF;

意味着如果状态的值为A,则如果信号P为1,则在时钟上升沿将状态更改为B.

案例中的最后一个陈述是

WHEN others =>

State <= A;

这个陈述是一个全面的声明,以确保如果状态不知为何具有不等于A,B,C或D的值,那么它将重置为A的值。

代码的最后一部分在流程之外完成并创建一个组合逻辑块。

R <= ‘1’ WHEN State=D ELSE ‘0’;

这个陈述正在做的是确定输出R的值。如果国家是D,R将是1在所有其他州将为0。这里需要注意的一点是,这个状态机的输出仅依赖于状态。目前状态是确定输出的唯一状态的状态机称为Moore状态机。另一大类的状态机是输出不仅取决于当前状态,还取决于输入。这种状态机称为Mealy状态机。在实践中,使用什么样的状态机通常没有关系,如果您知道您使用的是哪种状态机,则无关紧要。所有重要的是你按照你的定义来实现状态机。

设计这个系统的最后几个步骤将包括模拟系统以确保它完成预期的工作,然后在物理系统(CPLD,FPGA,ASIC等)上最终综合硬件实现。

概要

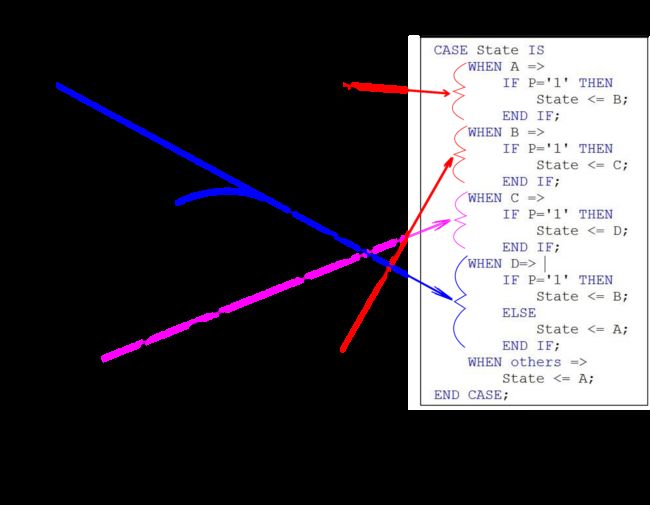

这些图表显示了有限状态机图和实现状态机所需的VHDL代码之间的关系。

图3. FSM图和VHDL中的状态定义

图4. FSM图和VHDL中的状态转换规则

图5. FSM图和VHDL中的输出

总结

本文对硬件描述语言的本质以及HDL语句与所实现硬件之间的关系进行了一些讨论。但是,主要目的是向您展示如何编写VHDL来实现有限状态机。该过程涉及创建一个定义状态机的输入和输出的VHDL实体,然后在VHDL体系结构块中写入状态转换的规则。使用此处提供的模板,您应该拥有实现自己的FSM所需的所有信息。