- xilinx工具编译ADI官方no-os和HDL工程步骤

ni1978

驱动fpgac语言驱动开发

以AD738x这款ADC为例,xilinx软件版本为2022.2:HDL工程:下载HDL工程:GitHub-analogdevicesinc/hdlathdl_2022_r2(GitHub-analogdevicesinc/hdlathdl_2022_r2)解压后,打开vivado2022.2,此时不要建工程,在tclconsole里输入cdc:/hdl-hdl_2022_r2/projects/

- 国产高兼容性ADC的突破:CYD7606N对比AD7606的核心优势

上海宸屿电子

电子元器件国产替代

在工业自动化、电力监测等领域的核心数据采集系统中,多通道同步采样ADC始终扮演着关键角色。目前AD7606长期主导这一市场,而上海宸屿电子推出的国产芯片CYD7606N正凭借深度兼容性与性能优化,成为极具竞争力的国产替代方案。其核心价值体现在三大技术突破:硬件与软件全兼容,实现零成本迁移CYD7606N采用与AD7606完全一致的64引脚LQFP封装(10mm×10mm),引脚功能定义实现100%

- Java小白入门200例56之鸡兔同笼问题

编程界小明哥

Java小白入门200例javajava小白入门实例

作者简介作者名:编程界明世隐简介:CSDN博客专家,从事软件开发多年,精通Java、JavaScript,博主也是从零开始一步步把学习成长、深知学习和积累的重要性,喜欢跟广大ADC一起打野升级,欢迎您关注,期待与您一起学习、成长、起飞!引言很多Java初学者问我,新手明明很用心、很努力学习的Java知识,转头又忘记了,很让人犯愁,小白如何能够快速成长、成为大牛呢?其实要成为大神的技巧只有一个:“多

- 【STM32】ADC的认识和使用——以STM32F407为例

Aeonio

嵌入式STM32stm32嵌入式硬件单片机

【STM32】ADC的认识和使用——以STM32F407为例文章目录【STM32】ADC的认识和使用——以STM32F407为例一、ADC简介ADC特性参数STM32F407的ADC主要特性ADC框图①输入电压②输入通道③转换顺序⑤转换时间⑦中断DMA请求(==只适用于规则组==)ADC工作模式单次转换模式和连续转换模式扫描模式不同模式组合的作用二、ADC配置单通道ADC采集配置步骤单通道ADC采

- 基于ZYNQ7000的AD9226采集卡实现(1、采集数据到PL)

目标AD9226为12位,65MHz采样率ADC。基于ZYNQ7010平台,PL端采集AD数据,通过内部AXI总线,将数据搬运到PS的DDR。可以将如上目标分解为3个小目标实现PL采集AD9226模块,采集后的数据为AXIS接口。实现PL侧DMA可搬运AXIS数据到PS的DDR,可配置地址,帧长度,帧数量等。实现PS侧DMA驱动本章节实现第一个小目标:硬件:主控板采集模块模块引脚功能:D0-D11

- AD7606过采样模式

零度随想

嵌入式硬件fpga开发

AD7606的过采样模式(OversamplingMode)是其重要特性之一,它可提升信噪比(SNR)、有效分辨率、降低系统噪声。✅一、什么是过采样(Oversampling)过采样是指ADC内部将每个通道采样多次,然后进行数字平均滤波,以减少随机噪声、提升信号质量。在AD7606中,过采样是由芯片内部硬件自动完成的:每次外部采样触发→芯片在内部进行多次转换→平均值输出对外仍只输出1个16位数据→

- 嵌入式开发学习日志Day14(ARM体系架构——RTC及ADC)

一、RTCRTC(实时时钟):非易失性在IMX6ULL内部SNVS(安全的非易失性存储器)提供RTC功能;原理图:二、ADC2.1基本概念ADC(模拟数字转换器):用于将连续变化的模拟信号转换为离散的数字信号以便数字系统对它进行处理;模拟信号:一般指连续变化的电压信号,其值在一定范围内变化;数字信号:由一系列离散数字表示仅取有限值,通常以二进制表示;2.2工作原理将模拟信号分割成一系列离散的取样,

- 从零玩转CanMV-K230(9)-Timer、RTC、ADC、WDT、File

叶与花语

K230人工智能AIK230python

文章目录前言一、Timer构造函数初始化销毁函数示例代码二、RTC构造函数initdatetime示例代码三、ADCAPI示例代码四、WDTAPI示例代码五、File示例代码总结前言本章介绍K230常用外设的使用方法,相关内容的详细介绍可以参考K210的教程,这里主要展示K230的使用代码一、Timer定时器(Timer)的作用在于生成精确的计时,当达到预设的时间点时,提醒我们进行特定的操作。Ti

- 【k230基础教程之ADC,RTC,TIMER,WDT】

k230基础教程之ADC,RTC,TIMER,WDT一,ADC1.read_u16方法2.read_uv方法示例二,RTC1.init方法2.detatime方法示例三,TIMER(定时器)1.init方法2.deinit方法软件定时器控制LED灯四,WDT(看门狗)1.feed方法示例本教程皆来自立创官方教程,为博主学习使用所记录,使用开发板为立创的庐山派,如有需求可自行访问立创官网关于这些外设

- 稳转细胞株构建全攻略:从理论到实践的生物制药核心技术解析

北京义翘神州

稳转细胞株构建服务

为何稳转细胞株成为生物制药领域的“兵家必争之地”?稳转细胞株被称为“药物研发的基石”,是单克隆抗体、双抗、疫苗、ADC等生物制品规模化生产的核心环节,还是药物生产成本、效率和质量的关键决定因素。一株高产稳定的细胞株有可能直接缩短药物上市周期3-5年。稳定细胞株因其稳定性高,适用于各种研究应用,包括重组蛋白、抗体生产、结构生物学和功能性研究等。那么,如何打造一株理想的稳转细胞株呢?义翘神州在重组表达

- 鼎盛合|如何做一个智能测脂懒啊体脂秤方案?

鼎盛合设计开发

单片机mcu

随着健康管理意识的提升,智能体脂秤逐渐成为家庭健康监测的核心设备。本文基于DSH38M93主控芯片与CS1237高精度ADC芯片,提出一种创新性的智能测脂蓝牙电子秤设计方案,重点阐述其技术实现原理与系统架构设计。一、技术原理与核心器件选型称重测量原理采用高精度应变片式传感器构建惠斯通电桥,通过CS1237芯片进行24位Δ-Σ模数转换。当用户站立时,四角传感器产生0-20mV差分信号,经128倍PG

- 9-STM32的ADC采样和DAM配置

水果里面有苹果

嵌入式软件stm32单片机嵌入式硬件

STM32的ADC采样和DAM配置Adc_Init();//ADC初始化My_DMA_Config(DMA1_Channel1,(u32)&ADC1->DR,(u32)&ADC1_Value,ADC_CHANNEL_NUM*ADC_C_VAL_TIMES);//配置DMA通道DMA_Cmd(DMA1_Channel1,ENABLE);//启动DMA通道ADC_SoftwareStartConvCm

- 【基于ESP32-S3的Modbus RTU单双精度浮点数验证方案】

2345VOR

#Arduino小项目开发工业通讯esp32s3ModBusRTU浮点数

基于ESP32-S3的ModbusRTU单双精度浮点数验证方案一、核心功能升级在工业自动化场景中,单纯的整型数据已无法满足高精度测量需求。本文在原有ADC数据采集方案基础上,通过ModbusRTU协议扩展实现以下功能升级:新增1路16位浮点数(3.3V量程)新增1路32位双精度浮点数(±2.5V量程)保持原有4通道ADC数据传输本方案在原有ADC数据采集基础上,重点实现单双精度浮点数(float&

- RK3399 驱动开发 _ 07 - ADC 开发

chenkanuo

驱动开发

文章目录前言一、ADC简介二、ADC配置1.dts节点配置2.重新编译并烧录三、ADC值获取1.计算采集到的电压2.获取ADC值在这里插入图片描述总结前言在RK3399平台开发过程中,经常需要用到ADC功能。例如:检测主板温度、复位/音量按键、DRAMID检测等。一、ADC简介RK3399板卡上常见的AD接口有2种:温度传感器(TemperatureSensor)、逐次逼近ADC(Successi

- ADC中断 电流值异常问题

沙琪玛666

算法

voidgetPowSum(void){staticuint16_ti=0;//基准电流采样12323//staticuint16_tia_buffer[MEDIAN_FILTER_SIZE]={0};//uint16_tfiltered_IA=medianFilter(ia_buffer,ADC_Value.value.IA);//采样数据累加ADC_Value.value.MV_16500_I

- 基于ARM+FPGA+ADC的储能协调控制器/EMS,支持全国产,支持实时系统

深圳信迈主板定制专家

电力新能源人工智能网络fpga开发arm开发

协调控制器是一款灵活可定制逻辑的多功能控制装置,可根据实际应用环境需求定制对应的控制逻辑,应用范围广泛,既可作为新能源站(光伏、风电、储能)的协调控制器,也可作为微网控制器或者综合控制器。产品特点1、支持图形化逻辑组态工具实现装置接口信号、处理逻辑、输出控制及事故告警的现场可视化组态、程序升级,可根据现场需求灵活定制功能;2、具备多路信号采集、多路控制输出;3、具有多种通讯接口,具备强大快速的通信

- STM32[笔记]--4.嵌入式硬件基础

wind_one1

STM32入门教程stm32嵌入式硬件笔记

4.嵌入式硬件基础4.1认识上官二号开发板主控芯片:STM32F103C8T6高速晶振:8M低速晶振:32.768kLED:5颗KEY:3个主控芯片内部的资源如下项目介绍内核Cortex-M3Flsah64K*8bitSRAM20K*8bitGPIO37个GPIO,分别为PA0-PB15,PC13-PC15,PD0-PD1ADC2个12bitADC合计12了通道,外部通道:PA0到PA7+PB0到

- TI SAR ADC

,这里简单介绍下TISAR原理及相关技术时域交织ADC通过并行多个子ADC,使其依次对输入进行采样、转换、输出的一种高速ADC结构。这种类型ADC的采样率可以达到子ADC的M倍,M是通道数,同时又具有子ADC的精度及特点。M通道时域交织ADC基本原理图如上图所示。子ADC采样率为fs/M,其中fs是时域交织ADC采样率。各子ADC采样时钟均匀分布,依次按相位延迟1/fs完成各自转换后再通过选择器(

- 技术Q&A | ADC/DAC芯片测试研讨会笔记请查收!

德思特

半导体测试系统ADC测试DAC测试

6月19日,《ADC/DAC芯片测试前沿:德思特ATX系统高效方案与实战攻略》线上研讨会圆满结束。感谢大家的观看与支持!在直播间收到一些观众的技术问题,我们汇总了热点问题并请讲师详细解答,在此整理分享给大家,请查收!基本知识储备:ADC/DAC芯片测什么?Q:你们可以做哪些类型的ADC芯片测试?你们可以测的ADC分辨率位数多高?主要支持三类主流ADC芯片:Pipeline型、逐次逼近型(SAR型)

- stm32引脚功能

desssq

armarm开发嵌入式硬件

一、输入模式模拟输入模式功能:将引脚直接连接到片上的ADC(模数转换器)或DAC(数模转换器,如果支持)模块。特点:禁止施密特触发器(数字输入缓冲器被关闭),避免引入数字噪声。禁止上拉和下拉电阻。引脚状态不能被CPU读取(读取IDR寄存器为0)。引脚电平由外部模拟信号直接决定。典型应用:连接模拟传感器(温度、光照、电压、电流等)到ADC进行采样。浮空输入模式功能:引脚作为纯数字输入。特点:施密特触

- 程序代码篇---ESP32-S3小智固件

Atticus-Orion

深度学习篇程序代码篇上位机知识篇AIEsp32-S3小智

Q1:ESP32-S3小智语音对话系统的整体架构是怎样的?A1:该系统采用“语音采集→唤醒词检测→ASR→NLP→TTS→语音播放”的流水线架构:硬件层:ESP32-S3芯片+麦克风阵列(如INMP441)+扬声器(如MAX98357A)。驱动层:ESP-IDF或Arduino框架提供的I2S、ADC、DAC驱动。算法层:唤醒词检测:基于MicroML(如TensorFlowLiteMicro)。

- 简说 STM32的ADC

STM32F1系列ADC简介的原文,出自参考手册RM0008。STM32F1ADC简介要点很好,你问的是逐次逼近型ADC(SARADC,SuccessiveApproximationRegisterADC)的工作原理。我来详细讲解,并配上简化时序逐次逼近ADC原理基本思路逐次逼近型ADC的核心思想是:从高位到低位逐步判断每一位的值(0或1),通过与输入电压比较,不断逼近输入电压,直到确定完整的数字

- ZigBee_CC2530_03H_ADC寄存器

ADC支持多达14位模数转换,有效位数(ENOB)多达12位。ADC包括一个具有多达8个独立配置通道的模拟多路转换器和参考电压发生器,并且通过DMA将转换结果写入存储器。具有多种运行模式。ADC主要特征如下:可选的采样率,可设置分辨率(7~12位)。8个独立的输入通道,单端或者差分。参考电压可选为内部、外部单端、外部差分或AVDD5。中断请求产生。转换结束时DMA触发。温度传感器输入。电池测量能力

- 中科亿海微SoM模组——中频信号采集存储卡

ehiway

fpga开发

数字中频信号采集存储是指利用ADC、FPGA实现对信号进行数字化采集、处理和存储传输的过程。该技术在通信、雷达、无线电等领域具有重要应用。通过高速ADC将模拟信号转换为数字信号,并在FPGA中进行数字信号处理,将数据存储、传输到外部存储器。中科亿海微开发的基于FPGA的中频信号采集存储卡,利用FPGA实现数字中频信号采集和处理,可以提高系统灵活性和性能,适用于需要高速数据处理和实时响应的应用场景。

- H750 双ADC交替采样 CUBEMX

現実君

算法

HAL_ADCEx_Calibration_Start(&hadc2,ADC_CALIB_FACTOR_LINEARITY_REGOFFSET,ADC_SINGLE_ENDED);//精校ADC采样HAL_ADCEx_Calibration_Start(&hadc1,ADC_CALIB_FACTOR_LINEARITY_REGOFFSET,ADC_SINGLE_ENDED);HAL_ADC_Sta

- STM32F407 ADC 模式详解:单次转换、连续转换、扫描模式、非扫描模式

Bu Bu M

stm32嵌入式硬件单片机

前言在STM32F407中,ADC(模数转换器)模块常用于采集模拟信号,比如读取光敏电阻、电压、电流、温度传感器等。STM32的ADC模式较多,初学者常常会混淆:单次转换和连续转换的区别扫描模式和非扫描模式分别用于什么场景本篇文章将全面讲解STM32F407中ADC的四种核心工作模式,带你从概念到应用搞懂它们的配置和组合。一、ADC模式分类总览STM32F407的ADC模式可以从两个维度理解:分类

- Python实现USB转SPI接口与ADS1256数据采集芯片通信测试

永不放弃yes

本文还有配套的精品资源,点击获取简介:该教程展示了如何使用Python语言通过USB转SPI接口与ADS1256数据采集芯片进行通信测试。ADS1256是一款高精度模数转换器,适用于多通道测量和信号处理。通过编写Python代码,项目的核心是读取ADS1256采集到的模拟信号,并将其转换为数字数据,涉及设置ADC参数以及管理SPI通信协议。教程包括了SPI通信协议、ADS1256芯片的配置和特性、

- 价格性价比高系列的高性能单片机MS32C001-C

郦777

单片机嵌入式硬件

MS32C001-C系列微控制器采用高性能的32位ARM®Cortex®-M0+内核,宽电压工作范围的MCU。嵌入18KBFlash和1.5KBSRAM存储器,最高工作频率24MHz。包含多种不同封装类型产品。芯片集成1路12位ADC,2个16位定时器。MS32C001-C系列微控制器的工作温度范围为-40~85°C,工作电压范围1.7~5.5V。芯片提供sleep/stop低功耗工作模式,可以满

- 工作频率可达144MHz的PY32F403系列单片机

郦777

单片机嵌入式硬件

PY32F403单片机典型工作频率可达144MHZ,内置高速存储器,丰富的增强型I/O端口和外设连接到外部总线。PY32F403系列单片机包含3个12位的ADC、2个12位DAC、最多10个16位通用定时器、2个16位电机控制PWM定时器,具有死区时间生成和紧急停止功能、2个基本定时器、还包含标准的通信接口:2个I2C接口、3个SPI接口、1个USB接口、1个CAN接口、1个SDIO接口和5个UA

- 十七、【ESP32全栈开发指南:ADC接口使用】

爱睡觉的王宇昊

ESP32esp32adc物联网嵌入式stm32霍尔传感器

一、概述ESP32集成两个12位逐次逼近型模数转换器(SARADC),共支持18个模拟输入通道:ADC1:8通道(GPIO32-GPIO39)ADC2:10通道(GPIO0、GPIO2、GPIO4、GPIO12-GPIO15、GPIO25-GPIO27)1.1ADC限制ADC2与Wi-Fi冲突:ADC2在Wi-Fi驱动启用时不可用,需在未启动Wi-Fi时使用。硬件限制:绑带引脚限制(GPIO0/2

- Spring4.1新特性——Spring MVC增强

jinnianshilongnian

spring 4.1

目录

Spring4.1新特性——综述

Spring4.1新特性——Spring核心部分及其他

Spring4.1新特性——Spring缓存框架增强

Spring4.1新特性——异步调用和事件机制的异常处理

Spring4.1新特性——数据库集成测试脚本初始化

Spring4.1新特性——Spring MVC增强

Spring4.1新特性——页面自动化测试框架Spring MVC T

- mysql 性能查询优化

annan211

javasql优化mysql应用服务器

1 时间到底花在哪了?

mysql在执行查询的时候需要执行一系列的子任务,这些子任务包含了整个查询周期最重要的阶段,这其中包含了大量为了

检索数据列到存储引擎的调用以及调用后的数据处理,包括排序、分组等。在完成这些任务的时候,查询需要在不同的地方

花费时间,包括网络、cpu计算、生成统计信息和执行计划、锁等待等。尤其是向底层存储引擎检索数据的调用操作。这些调用需要在内存操

- windows系统配置

cherishLC

windows

删除Hiberfil.sys :使用命令powercfg -h off 关闭休眠功能即可:

http://jingyan.baidu.com/article/f3ad7d0fc0992e09c2345b51.html

类似的还有pagefile.sys

msconfig 配置启动项

shutdown 定时关机

ipconfig 查看网络配置

ipconfig /flushdns

- 人体的排毒时间

Array_06

工作

========================

|| 人体的排毒时间是什么时候?||

========================

转载于:

http://zhidao.baidu.com/link?url=ibaGlicVslAQhVdWWVevU4TMjhiKaNBWCpZ1NS6igCQ78EkNJZFsEjCjl3T5EdXU9SaPg04bh8MbY1bR

- ZooKeeper

cugfy

zookeeper

Zookeeper是一个高性能,分布式的,开源分布式应用协调服务。它提供了简单原始的功能,分布式应用可以基于它实现更高级的服务,比如同步, 配置管理,集群管理,名空间。它被设计为易于编程,使用文件系统目录树作为数据模型。服务端跑在java上,提供java和C的客户端API。 Zookeeper是Google的Chubby一个开源的实现,是高有效和可靠的协同工作系统,Zookeeper能够用来lea

- 网络爬虫的乱码处理

随意而生

爬虫网络

下边简单总结下关于网络爬虫的乱码处理。注意,这里不仅是中文乱码,还包括一些如日文、韩文 、俄文、藏文之类的乱码处理,因为他们的解决方式 是一致的,故在此统一说明。 网络爬虫,有两种选择,一是选择nutch、hetriex,二是自写爬虫,两者在处理乱码时,原理是一致的,但前者处理乱码时,要看懂源码后进行修改才可以,所以要废劲一些;而后者更自由方便,可以在编码处理

- Xcode常用快捷键

张亚雄

xcode

一、总结的常用命令:

隐藏xcode command+h

退出xcode command+q

关闭窗口 command+w

关闭所有窗口 command+option+w

关闭当前

- mongoDB索引操作

adminjun

mongodb索引

一、索引基础: MongoDB的索引几乎与传统的关系型数据库一模一样,这其中也包括一些基本的优化技巧。下面是创建索引的命令: > db.test.ensureIndex({"username":1}) 可以通过下面的名称查看索引是否已经成功建立: &nbs

- 成都软件园实习那些话

aijuans

成都 软件园 实习

无聊之中,翻了一下日志,发现上一篇经历是很久以前的事了,悔过~~

断断续续离开了学校快一年了,习惯了那里一天天的幼稚、成长的环境,到这里有点与世隔绝的感觉。不过还好,那是刚到这里时的想法,现在感觉在这挺好,不管怎么样,最要感谢的还是老师能给这么好的一次催化成长的机会,在这里确实看到了好多好多能想到或想不到的东西。

都说在外面和学校相比最明显的差距就是与人相处比较困难,因为在外面每个人都

- Linux下FTP服务器安装及配置

ayaoxinchao

linuxFTP服务器vsftp

检测是否安装了FTP

[root@localhost ~]# rpm -q vsftpd

如果未安装:package vsftpd is not installed 安装了则显示:vsftpd-2.0.5-28.el5累死的版本信息

安装FTP

运行yum install vsftpd命令,如[root@localhost ~]# yum install vsf

- 使用mongo-java-driver获取文档id和查找文档

BigBird2012

driver

注:本文所有代码都使用的mongo-java-driver实现。

在MongoDB中,一个集合(collection)在概念上就类似我们SQL数据库中的表(Table),这个集合包含了一系列文档(document)。一个DBObject对象表示我们想添加到集合(collection)中的一个文档(document),MongoDB会自动为我们创建的每个文档添加一个id,这个id在

- JSONObject以及json串

bijian1013

jsonJSONObject

一.JAR包简介

要使程序可以运行必须引入JSON-lib包,JSON-lib包同时依赖于以下的JAR包:

1.commons-lang-2.0.jar

2.commons-beanutils-1.7.0.jar

3.commons-collections-3.1.jar

&n

- [Zookeeper学习笔记之三]Zookeeper实例创建和会话建立的异步特性

bit1129

zookeeper

为了说明问题,看个简单的代码,

import org.apache.zookeeper.*;

import java.io.IOException;

import java.util.concurrent.CountDownLatch;

import java.util.concurrent.ThreadLocal

- 【Scala十二】Scala核心六:Trait

bit1129

scala

Traits are a fundamental unit of code reuse in Scala. A trait encapsulates method and field definitions, which can then be reused by mixing them into classes. Unlike class inheritance, in which each c

- weblogic version 10.3破解

ronin47

weblogic

版本:WebLogic Server 10.3

说明:%DOMAIN_HOME%:指WebLogic Server 域(Domain)目录

例如我的做测试的域的根目录 DOMAIN_HOME=D:/Weblogic/Middleware/user_projects/domains/base_domain

1.为了保证操作安全,备份%DOMAIN_HOME%/security/Defa

- 求第n个斐波那契数

BrokenDreams

今天看到群友发的一个问题:写一个小程序打印第n个斐波那契数。

自己试了下,搞了好久。。。基础要加强了。

&nbs

- 读《研磨设计模式》-代码笔记-访问者模式-Visitor

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

import java.util.ArrayList;

import java.util.List;

interface IVisitor {

//第二次分派,Visitor调用Element

void visitConcret

- MatConvNet的excise 3改为网络配置文件形式

cherishLC

matlab

MatConvNet为vlFeat作者写的matlab下的卷积神经网络工具包,可以使用GPU。

主页:

http://www.vlfeat.org/matconvnet/

教程:

http://www.robots.ox.ac.uk/~vgg/practicals/cnn/index.html

注意:需要下载新版的MatConvNet替换掉教程中工具包中的matconvnet:

http

- ZK Timeout再讨论

chenchao051

zookeepertimeouthbase

http://crazyjvm.iteye.com/blog/1693757 文中提到相关超时问题,但是又出现了一个问题,我把min和max都设置成了180000,但是仍然出现了以下的异常信息:

Client session timed out, have not heard from server in 154339ms for sessionid 0x13a3f7732340003

- CASE WHEN 用法介绍

daizj

sqlgroup bycase when

CASE WHEN 用法介绍

1. CASE WHEN 表达式有两种形式

--简单Case函数

CASE sex

WHEN '1' THEN '男'

WHEN '2' THEN '女'

ELSE '其他' END

--Case搜索函数

CASE

WHEN sex = '1' THEN

- PHP技巧汇总:提高PHP性能的53个技巧

dcj3sjt126com

PHP

PHP技巧汇总:提高PHP性能的53个技巧 用单引号代替双引号来包含字符串,这样做会更快一些。因为PHP会在双引号包围的字符串中搜寻变量, 单引号则不会,注意:只有echo能这么做,它是一种可以把多个字符串当作参数的函数译注: PHP手册中说echo是语言结构,不是真正的函数,故把函数加上了双引号)。 1、如果能将类的方法定义成static,就尽量定义成static,它的速度会提升将近4倍

- Yii框架中CGridView的使用方法以及详细示例

dcj3sjt126com

yii

CGridView显示一个数据项的列表中的一个表。

表中的每一行代表一个数据项的数据,和一个列通常代表一个属性的物品(一些列可能对应于复杂的表达式的属性或静态文本)。 CGridView既支持排序和分页的数据项。排序和分页可以在AJAX模式或正常的页面请求。使用CGridView的一个好处是,当用户浏览器禁用JavaScript,排序和分页自动退化普通页面请求和仍然正常运行。

实例代码如下:

- Maven项目打包成可执行Jar文件

dyy_gusi

assembly

Maven项目打包成可执行Jar文件

在使用Maven完成项目以后,如果是需要打包成可执行的Jar文件,我们通过eclipse的导出很麻烦,还得指定入口文件的位置,还得说明依赖的jar包,既然都使用Maven了,很重要的一个目的就是让这些繁琐的操作简单。我们可以通过插件完成这项工作,使用assembly插件。具体使用方式如下:

1、在项目中加入插件的依赖:

<plugin>

- php常见错误

geeksun

PHP

1. kevent() reported that connect() failed (61: Connection refused) while connecting to upstream, client: 127.0.0.1, server: localhost, request: "GET / HTTP/1.1", upstream: "fastc

- 修改linux的用户名

hongtoushizi

linuxchange password

Change Linux Username

更改Linux用户名,需要修改4个系统的文件:

/etc/passwd

/etc/shadow

/etc/group

/etc/gshadow

古老/传统的方法是使用vi去直接修改,但是这有安全隐患(具体可自己搜一下),所以后来改成使用这些命令去代替:

vipw

vipw -s

vigr

vigr -s

具体的操作顺

- 第五章 常用Lua开发库1-redis、mysql、http客户端

jinnianshilongnian

nginxlua

对于开发来说需要有好的生态开发库来辅助我们快速开发,而Lua中也有大多数我们需要的第三方开发库如Redis、Memcached、Mysql、Http客户端、JSON、模板引擎等。

一些常见的Lua库可以在github上搜索,https://github.com/search?utf8=%E2%9C%93&q=lua+resty。

Redis客户端

lua-resty-r

- zkClient 监控机制实现

liyonghui160com

zkClient 监控机制实现

直接使用zk的api实现业务功能比较繁琐。因为要处理session loss,session expire等异常,在发生这些异常后进行重连。又因为ZK的watcher是一次性的,如果要基于wather实现发布/订阅模式,还要自己包装一下,将一次性订阅包装成持久订阅。另外如果要使用抽象级别更高的功能,比如分布式锁,leader选举

- 在Mysql 众多表中查找一个表名或者字段名的 SQL 语句

pda158

mysql

在Mysql 众多表中查找一个表名或者字段名的 SQL 语句:

方法一:SELECT table_name, column_name from information_schema.columns WHERE column_name LIKE 'Name';

方法二:SELECT column_name from information_schema.colum

- 程序员对英语的依赖

Smile.zeng

英语程序猿

1、程序员最基本的技能,至少要能写得出代码,当我们还在为建立类的时候思考用什么单词发牢骚的时候,英语与别人的差距就直接表现出来咯。

2、程序员最起码能认识开发工具里的英语单词,不然怎么知道使用这些开发工具。

3、进阶一点,就是能读懂别人的代码,有利于我们学习人家的思路和技术。

4、写的程序至少能有一定的可读性,至少要人别人能懂吧...

以上一些问题,充分说明了英语对程序猿的重要性。骚年

- Oracle学习笔记(8) 使用PLSQL编写触发器

vipbooks

oraclesql编程活动Access

时间过得真快啊,转眼就到了Oracle学习笔记的最后个章节了,通过前面七章的学习大家应该对Oracle编程有了一定了了解了吧,这东东如果一段时间不用很快就会忘记了,所以我会把自己学习过的东西做好详细的笔记,用到的时候可以随时查找,马上上手!希望这些笔记能对大家有些帮助!

这是第八章的学习笔记,学习完第七章的子程序和包之后

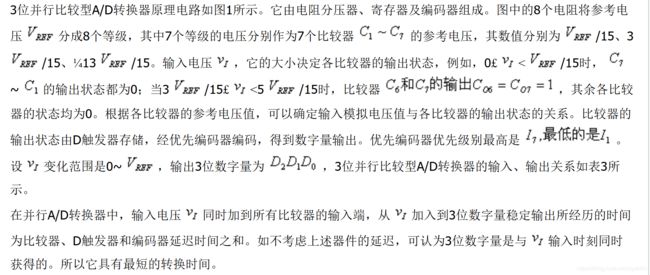

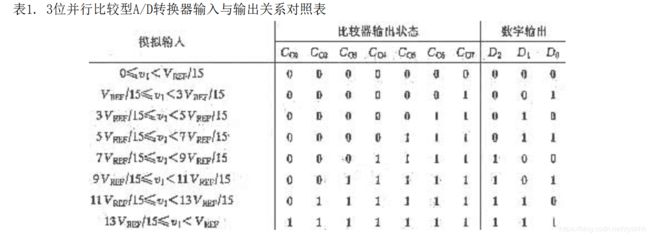

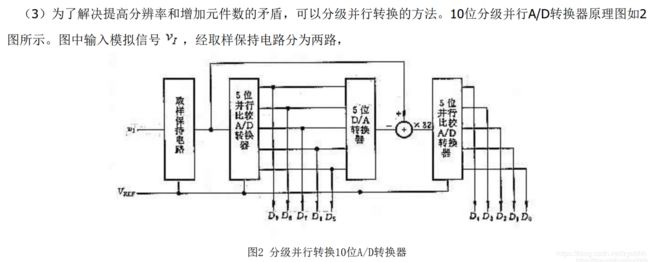

其实就是将一次比较变成了两次比较,可以成倍数的减少所需要的比较器的个数。对于n位的逐次比较器就需要比较n次,而对于并行比较型ADC只需要比较两次,因此在速度上是很高的。

其实就是将一次比较变成了两次比较,可以成倍数的减少所需要的比较器的个数。对于n位的逐次比较器就需要比较n次,而对于并行比较型ADC只需要比较两次,因此在速度上是很高的。