mpc8321记录

PowerQUICC II processors

MPC8321 PowerQUICC II Pro 是经济高效的MPC8323E 系列网络通信处理器的一员, 它能满足小型办公室/家庭办公室 (SOHO)、宽带接入、路由器和工业控制等多种应用的需求。与目前的 PowerQUICC 处理器相比,它能提供更好的CPU性能、额外的功能和更快速的接口, 并可满足上市时间、价格、功耗和板上空间等重要要求。

内核复合体

MPC8321 包含一个配置独特的 e300c2 (基于MPC603e)内核。这一版本的 e300 内核没有浮点单元 (FPU),它包括双整数单元和一个修改过的乘法指令。这些结构方面的增强特性允许并行执行更有效的操作,从而显著提高了性能。该内核还包括一个 16 KB 的 L1 指令、数据缓存和 片上内存管理单元 (MMU)。

MPC8321 还包括一个 32 位 PCI 控制器、四个 DMA 通道、一个灵活的本地总线和一个 32 位DDR-1/DDR-2 SDRAM存储器控制器。

QUICC Engine 技术

全新单RISC版本的QUICC Engine通信引擎构成了MPC8321的网络能力核心。QUICC Engine 模块包含几个外设控制器和一个 32 位单RISC控制器。独特的微代码包支持网络地址端口转换 (NAT)、防火墙、 IPsec和高级服务质量 (QoS)。协议支持由该器件的主要动力组件——统一通信控制器 (UCC)提供。五个 UCC 每一个都可以支持一系列通信协议:

- 三个 10/100 Mbps以太网

- 高级数据链路控制(HDLC)

- 四个时分复用(TDM)

- 二进制同步通信协议(BISYNC)

- UCC 也可支持 USB 2.0 (全速/低速).

系统接口单元

MPC8321系列包括一个 32位双倍数据传输速率 (DDR)-1/DDR/2 内存控制器、 一个 32位外设组件互联(PCI) 控制器、 一个 16 位本地总线和四个直接存储器存取(DMA)通道。

PowerQUICC® II Pro系列产品比较

| MPC8321 | MPC8321E | MPC8323 | MPC8323E | |

| 浮点单元 | 0 |

0 |

0 |

0 |

| H/W Security | No |

Sec 2.2 |

No |

Sec 2.2 |

| UTOPIA I/F (8-bit) | No |

No |

Yes |

Yes |

| I2C | 1 |

1 |

1 |

1 |

| QMC Support | up to 64–ch @ 64kbps |

up to 64–ch @ 64kbps |

up to 64–ch @ 64kbps |

up to 64–ch @ 64kbps |

| Memory Controller (no ECC) | 32-bit 266 MHz DDR1/DDR2 |

32-bit 266 MHz DDR1/DDR2 |

32-bit 266 MHz DDR1/DDR2 |

32-bit 266 MHz DDR1/DDR2 |

| QUICC Engine RISC Units | 1 |

1 |

1 |

1 |

| QUICC Engine Freq up | up to 200 MHz |

up to 200 MHz |

up to 200 MHz |

up to 200 MHz |

| 以太网 | up to 3 - 10/100 |

up to 3 - 10/100 |

up to 3 - 10/100 |

up to 3 - 10/100 |

| PCI | 32-bit up to 66 MHz |

32-bit up to 66 MHz |

32-bit up to 66 MHz |

32-bit up to 66 MHz |

| Local bus | 16-bit up to 66 MHz |

16-bit up to 66 MHz |

16-bit up to 66 MHz |

16-bit up to 66 MHz |

| UART | 2 |

2 |

2 |

2 |

| USB | USB 2.0 FS/LS |

USB 2.0 FS/LS |

USB 2.0 FS/LS |

USB 2.0 FS/LS |

| L1 I/D Cache | 16KI/16KD |

16KI/16KD |

16KI/16KD |

16KI/16KD |

| Integer Units | 2 |

2 |

2 |

2 |

| TDM I/F | up to 4 – 32ch w/QMC |

up to 4 – 32ch w/QMC |

up to 4 – 32ch w/QMC |

up to 4 – 32ch w/QMC |

| 封装类型和焊端数 | 516-PBGA |

516-PBGA |

516-PBGA |

516-PBGA |

| e300c2 | e300c2 |

e300c2 |

e300c2 |

e300c2 |

| up to 333 MHz | up to 333 MHz |

up to 333 MHz |

up to 333 MHz |

up to 333 MHz |

1、结构框图

芯片主要的特征如下:

高性能,具有一四级流水线的超标量处理器核心和低中断

延迟时间

•双整数单位,负载/存储,系统寄存器,分支处理单元

•16K字节指令高速缓存和16字节的数据缓存和锁定功能

•动态电源管理

•增强硬件程序的调试功能

• 软件实现技术与飞思卡尔的处理器家族power架构兼容

2)QUICC引擎1.0block

-对通信外设灵活支持32位RISC控制器具有以下特点:

-每一条指令的一个时钟

-独立的锁相环的工作频率,是独立于系统的总线和核心频率为了电源和性能优化

-32位指令对象代码

---从内部只读存储器ROM或内存RAM中执行代码

---32位算术逻辑单元(ALU)的数据路径

---模块化的架构,允许简单的功能增强

--- slave bus为了寄存器和多用户内存空间的CPU访问

---16字节的用户数据RAM

-串行DMA通道用于接收和发送的所有串行通道

-五统一通信控制器(UCC)支持以下协议接口:

---10 / 100 Mbps以太网/IEEE 802.3通过MII和RMII接口。

---ATM通过UPC(mpc8323特定)

---通过串行接口的串行ATM

---HDLC /透明(码率高达70 Mbps)

---HDLC总线(码率高达10 Mbps)

---异步HDLC(码率高达2 Mbps)

---UART

---双同步(比特率高达2 Mbps)

--- 四个TDM接口支持多达64QUICC的多通道控制器(QMC),每个运行在64 kbps

-ATM控制器

---全双工SAR协议在OC-3速率通过 UTOPIA L2(mpc8323特殊)

---AAL5,aal0 协议。TM 4.1 CBR,VBR,UBR,UBR +traffic类型

---ATM反向复用能力(IMA)

---1UTOPIA L2总线控制器(UPC)支持31个端口(mpc8323特殊)

---USB 1.1全/低码率兼容

---USB 2全/低码率兼容(不是高速)

---USB主机模式

---USB从机模式

-时隙分配器和4TDM串行接口

---独立接收和发送路由RAM伴随每入口512 路由。

-13独立波特率发生器和19个输入引脚来给以下提供时钟: UCCs,Si,UPC,USB, 时间戳和计时器。

-数据加密标准执行单位(DEU)

---DES和3DES算法

---两个键(K1,K2键)或三个键(K1,K2,K3)for 3DES

---ECB和CBC模式为了DES和3DES

-高级加密标准单位(AESU)

---Rijndael对称密钥密码的实现

---密钥长度128-,192- 和256位

---ECB,CBC,CCM和计数器(CTR)模式

-消息摘要执行单位(mdeu)

---SHA具有160或256位的消息摘要

---MD5具有128位的消息摘要

--- HMAC具有两者算法

---动态密码执行单位算法通过一个集成控制器

---256字节的缓冲区大小对于每个执行单位,以及流量控制为大数据规模

---支持多 杰出的总线处理

--取在加密频道的FIFO

-可编程时间支持DDR1和 DDR2 SDRAM

-512Mbyte寻址空间

-支持2X16的设备

-支持以下的SDRAM配置:

---64兆到1 Gbit设备以及x8 / x16 / x32数据端口(X4数据端口没有直接支持)。一些2- Gbit设备是否支持取决于内部设备配置。

-存储器的单一的物理bank(一个片选)伴随八个逻辑bank

-支持最大8个同时开放的 页

-睡眠模式支持 SDRAM 自刷新

-On-the-fly power management using CKE

-注册SIMM支持

-2.5V SSTL2_兼容I/O for DDR1,1.8-v SSTL_18兼容I/O for DDR2

5)PCI接口

-32位的PCI接口,操作在高达66MHZ

-3.3V兼容PCI

-支持主机和代理模式

-PCI的读访问的存储器预取和支持延迟读取操作

-Inbound and outbound write posting

-PCI内部配置寄存器可访问

-可选择的硬件执行的一致性

6)本地总线控制器(LBC)

•多路复用和非复用的26位地址和16位数据,运行速度高达66MHZ

•四片选支持四个外部的从设备

•支持最多64M字节的存储

•高达eight-beat burst转移(8拍的突发传输)

•16 - 8位端口尺寸

•每个片选都有2个协议引擎:

---通用芯片选择机(GPCM)

---三个用户可编程机(UPMS)

•功能和可编程兼容性伴随MPC8349中断控制器

•支持外部和内部离散的中断源

•支持一个外部(可选)和七个内部机器检查中断源

•可编程最高优先级请求

•四组可编程优先级中断

•针对通信处理器的外部和内部中断

-重定向中断外部的PCI_INTA信号当in core disable mode

•每个中断源的唯一向量号

8)I2C接口

-二线接口串行数据SDA和串行时钟SCL

-多主设备支持

-主或从的I2C模式支持

-在芯片上的数字滤波消除在总线上的尖峰信号

9)DMA(直接存储器访问)控制器

-四个独立的完全可编程DMA通道

-错位的转移能力的源/目的地址

-数据链接和直接模式

-在完成段和链时产生 中断

10)DUART

-与原16450 UART和pc16550D 编程模式 兼容

11)并行I/O

-通用I/O(GPIO)

---在各种芯片接口上,有128个并行输入/输出 复用引脚

-中断能力

12)系统计时器

-周期中断定时器

-实时时钟

-软件看门狗定时器

-2个通用定时器

13)IEEE 1149.1兼容的JTAG边界扫描

14)集成PCI总线和SDRAM的时钟产生

e300c2核心集成了五个执行单元--两个整数单位(IU1和IU2)伴随完整的乘法和除法,一个分支处理单元(BPU)伴随静态分支预测,一个加载/存储单元(LSU)为了数据转移,和系统寄存器单元(SRU)。执行五个指令并行的能力,并使用简单指令的快速执行时间产生高效率和吞吐量。大多数整数指令在一个时钟周期执行;2个整数指令可以同时执行伴随双整数单元。

存储器映射

2、完整的IMMR映射

在一些特殊的情况,保留位不被清除,并且保持复位值。因此,软件必须执行“读-改变-写“并且保证这些位的复位值不被改变。

除非在特定的块中声明,否则所有访问和从内存映射寄存器必须用32位访问。没有支持除了32位的访问。

3、QUICC引擎内部存储器映射

映射到连续的存储器块,内部空间是1M。QUICC引擎内部存储器空间的最后758K是保留的,为了将来的扩展。任何保留区域的访问都会导致未定义的行为。

章节3 信号描述

本章介绍了mpc8323e外部信号。它被组织成以下几个部分:

概述信号和交叉引用的信号,提供多种功能,其中包括2列表:一个有序的功能块和一个字母。

1)复位配置信号列表

2)在重置时输出信号状态列表

3)并行输入/输出信号

信号名上带横线的表示当低电平时是活跃的。内部的信号名表现为斜体。

3.1信号概述

The MPC8323E signals are grouped as follows:

• DDR memory interface signals :65信号

• PCI interface signals:54信号

• QUICC Engine interface signals:128信号PA、PB、PC、PD

• DUART interface signals:8信号

• I2C interface signals:2信号

• Local bus interface signals:42信号

• PIC interface signals:13信号

• PM interface signal:1信号

• JTAG(5信号), PMC(1信号), system control signals(3信号)

• Clock signals:10信号

注意,端口引脚没有内部上拉电阻。

外设 I/O ports’ 重要的特征:

• Ports A, B, C, and D all have 32 pins.

• All ports are bidirectional.

• All ports have alternate on-chip peripheral functions.

• Each pin has four direction options: Input, Output, I/O and Disabled. A disabled pin is not driving

any value and can be left floating outside the device (no need for external pull up or pull down).

• All port pins are disabled at hard reset.

• Usually pin values can be read while the pin is connected to an on-chip peripheral (this is not

possible for port pins, which are used as PCI pins).

• Open-drain capability on all port pins

• Some of the port pins can be used as interrupt input pins.

每个端口具有6个存储器映射:CPODRx, CPDATx, CPDIR1x, CPDIR2x, CPPAR1x and CPPAR2x。

CPODRx决定open-drain configuration for each pin.

CPDATx确定读写.

CPDIR1x and CPDIR2x registers (two bits per pin) 决定输入还是输出.

CPPAR1x and CPPAR2x registers (two bits per pin) 决定每个引脚的功能。

章节4 重启、时钟和初始化

复位,时钟,和控制信号提供了许多选项的操作装置。各种模式和特征在硬复位或复位电源时可配置。很多可配置的功能加载到该设备上通过一个复位配置字,并且一些设备的信号在复位序列中被用作重置配置输入。

4.1功能描述

设备具有几种输入复位逻辑:

• Power-on reset (PORESET)

• External hard reset (HRESET)

• External soft reset (SRESET)

• Software watchdog reset

• System bus monitor reset

• Checkstop reset

• JTAG reset

• Software hard reset

• Software soft reset

4.3.2 复位配置字

复位配置字控制时钟比率和其他基本设备的功能,如PCIhost或代理模式,启动位置,和端模式。重置配置字是从本地总线或I2C接口或上电或硬复位过程中硬编码的值加载的。

虽然配置复位字是在硬复位流中加载的,但是时钟和PLL模式仅在PORESET置位时(在上电复位流中)被复位。

复位配置字寄存器(RCWLR和RCWHR)中的值仅反映在复位流过程中的状态。一些参数和模式的值可以在存储器映射寄存器中被修改。

复位配置的设定可以通过以下只读存储器映射寄存器得到:

复位配置字低寄存器RCWLR

复位配置字高寄存器RCWHR

复位状态寄存器RSR

系统PLL模式寄存器SPMR

4.3.2.1.1系统PLL配置

系统PLL比率复位,建立时钟比率在CLKIN(PLL host)或者PCI_CLK(PCI代理模式)输入信号和内部设备的csb_clk之间。csb_clk驱动内部单元并且feed e300 内核PLL。系统时钟(CLKIN/PCI_SYNC_IN)输入频率的支持范围是25~66MHZ。

4.3.2.2.1 PCI HOST/agent 配置

在Host模式,设备可以立即master 传输到PCI接口。如果是pci agent设备,设备直到外部host使能它去做,才能去做 MaterPCI 传输。外部Host通过合理的配置设备的接口的控制寄存器来使能它。

4.3.3 加载复位配置字

装置加载复位配置字是从local bus EEPROM或者I2C串行EEPROM,或者使用hard-coded配置。

4.3.3.1从local bus EEPROM中加载

复位配置字被假定位于一个EEPROM器件,其连接到设备本地总线的LCS0。因为这个EEPROM端口的大小是未知的,所有配置字从位置被按字节读取,独立于端口大小。

为了从本地总线EEPROM加载复位配置字,PCI_SYNC_IN/PCI_CLK输入时钟被32分频为了使能慢频率存储器的工作。

显示的EEPROM内容的一个例子,包括前言,复位配置字和额外的初始化数据,和CRC校验。在这个例子中,它是假定EEPROM包含信息附加到重置配置字,它应该在该装置完成复位流后加载到功能状态中。

4.3.3.3缺省复位配置字

如果设备被配置成不从本地总线EEPROM和I2C EEPROM的复位配置字中加载,还可以用五个hard-coded中一个的默认选项,由复位配置输入信号选择,CFG_RESET_SOURCE[0:2].在这种模式下,设备被假定成一个PCI代理,因此只有时钟模式在四种选择中不同。

4.4时钟

设备原始时钟源可以是CLKIN或者PCI_CLK,取决于设备是配置成PCIhost还是PCI代理模式。

4.4.1在PCI host模式下的时钟

设备被配置为PCI主模式,RCWH[PCIHOST]=1,CLKIN是原始时钟。CLKIN feed PCI时钟分频(除以2)并且PCI_SYNC_OUT和PCI_CLK_OUT多路复用。CFG_CLKIN_DIV可以配置成CLKIN或者CLKIN/2输入来驱动PCI_SYNC_OUT信号输出。

4.4.1.1PCI时钟输出(PCI_CLK_OUT[2:0])

当设备被配置为PCI主模式,提供三种时钟输出信号,PCI_CLK_OUT[0:2]给外部PCI代理。

当设备从复位中启动,PCI时钟输出被禁止,并且驱动为平稳低状态。每个独立时钟输出可以被使能,通过设置相应的OCCR[PCICOEn]位。所有输出时钟彼此phase alignedPCI_SYNC_OUT.

4.4.2时钟在PCI代理模式

PCI_CLK是输入时钟源。CLKIN/CLKIN需要接地。时钟输出信号PCI_CLK_OUTn和PCI_SYNC_OUT没被使用。CFG_CLKIN_DIV配置输入可以被用来double内部时钟频率。

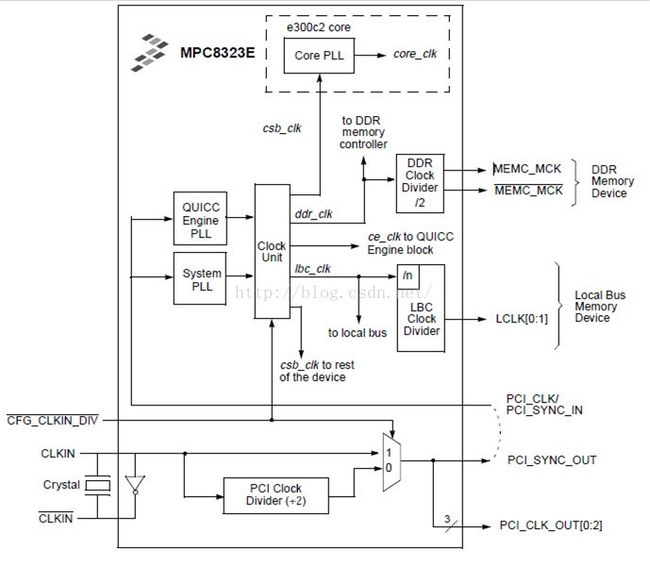

4.4.3系统时钟域

初始时钟输入(PCI_CLK/PCI_SYNC_IN)频率被系统锁相环PLL倍频,并产生四种主要的时钟域:

• The coherent system bus clock (csb_clk)

• The QUICC engine clock (ce_clk)

• The internal clock for the DDR controller (ddr_clk)

• The internal clock for the local bus interface unit (lbc_clk)

csb_clk = [PCI_SYNC_IN × (1 + ~CFG_CLKIN_DIV)] × SPMF

在PCI主模式,PCI_SYNC_IN × (1 + ~CFG_CLKIN_DIV)是CLKIN频率。

当CLKIN是输入时钟源,

ce_clk = (primary clock input × CEPMF) ÷ (1 + CEPDF)

当PCI_CLK是输入时钟源,

ce_clk = [primary clock input × CEPMF × (1 + ~CFG_CLKIN_DIV)] ÷ (1 + CEPDF)

章节5 系统配置

该设备提供了一个灵活的本地内存映射。本地内存映射是指通过处理器看到的32位地址空间

当它访问内存和输入/输出空间。内部DMA引擎也看到同样的存储器映射。所有的DDR SDRAM和局部总线内存控制器存访问的内存都存在于这个存储器映射中,内存映射的配置与控制和状态寄存器也一样。

本地内存映射是由一组九个本地访问窗口定义的。这些窗口中的每一个将存储区域映射到一个特定的目标的界面,如DDR SDRAM控制器或PCI控制器。在msc7104的DSP子系统无法运行。注意本地访问窗口不执行任何地址转换。每个窗口的大小从4字节到2 GB配置。

窗口号 目标接口 说明

0 配置寄存器IMMR 固定的2M窗口大小

1~4 local bus

5~6 PCI

7~8 DDR SDRAM

5.2地址转换与映射

在添加任何e300c2 MMU地址转换操作中,三个不同类型的转换和映射操作是在transactions上执行的在集成器件的水平。如下:

•本地地址映射到目标接口

•转换的本地32位地址到外部地址空间

•转换外部地址到本地的32位地址空间

本地访问窗口执行本地地址空间内的目标映射。这个本地访问窗口不执行任何地址转换。

outbound窗口执行从本地32位地址空间映射到PCI地址空间,这可能比当地的空间大得多。

inbound窗口执行地址转换,从PCI外部地址空间到本地地址空间。

5.2.4本地可访问寄存器描述

5.2.4.1内部存储器映射基址寄存器IMMRBAR

IMMR窗口包含配置、控制和状态寄存器,还有内部设备存储器阵列。内部存储器映射占有2M的存储器区域。IMMR默认的基址是0XFF400000。因为IMMRBAR是位于本地access寄存器开始地址的偏移地址0X0处,所以IMMRBAR总是指向自己。写入IMMRBAR可以修改该基址。

5.2.8 outbound地址转换和映射窗口

outbound地址转换和映射涉及到从本地32位地址空间到外部地址空间以及特别是I/O接口的属性的地址转换。在此设备上,PCI block具有outbound地址转换单元。PCI控制器具有六个outbound串口,并且还有一个默认的窗口。

5.2.9 Inbound地址转换和映射窗口

涉及从I/O接口的外部地址空间(如PCI地址空间)到处理器的内部接口占有的内部地址空间的地址转换。PCI控制器具有inbound地址转换单元。